目录

[一. 概述](#一. 概述)

[二. 3D-IC 描述语言使用限制](#二. 3D-IC 描述语言使用限制)

Calibre® 3DSTACK 应用程序可帮助您验证包含倒装芯片 、硅通孔(TSV) 以及其他 2.5D 和 3D-IC 结构的设计。

一. 概述

传统集成电路(IC)为独立封装 ,可通过 Calibre nmDRC、Calibre nmLVS、Calibre RVE 和 Calibre DESIGNrev 在芯片级 完成验证。3D-IC 由多个堆叠芯片 组成,通过interposer 上的走线 或专用过孔 / bump 实现互连。Calibre 3DSTACK 工具用于验证这些芯片之间的接口 ,其中可能包含block box IP。

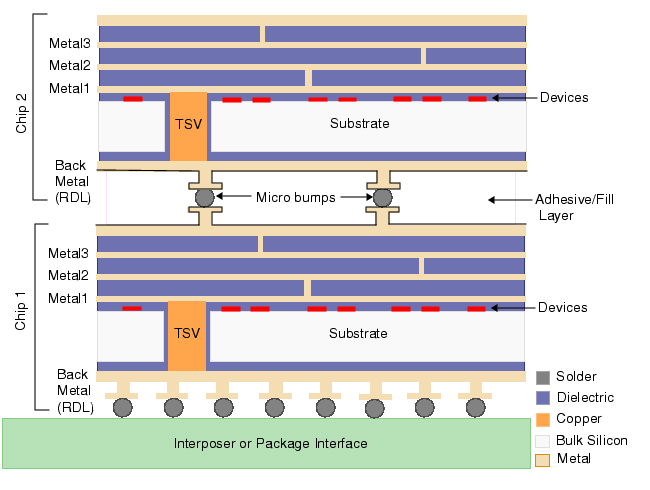

图 1-1 展示了 3D-IC 的横截面示意图。2.5D 和 3D-IC 结构的核心区别 在于是否使用SI interposer。

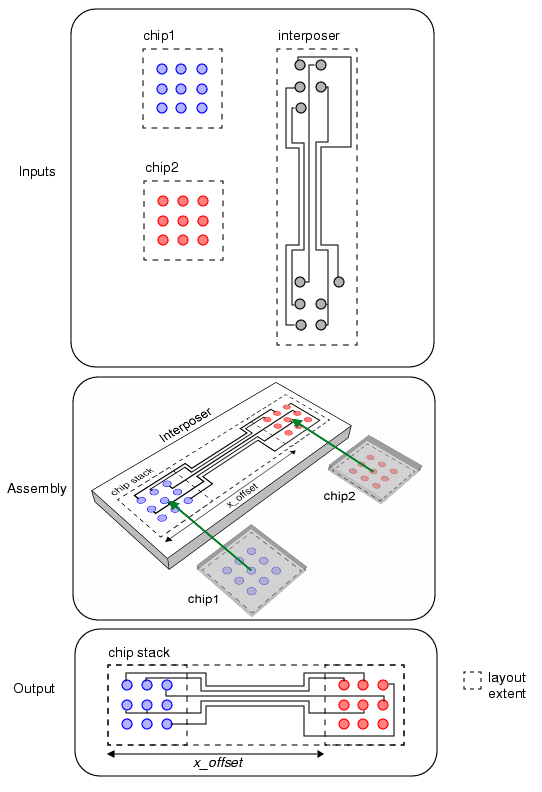

如图 1-2 所示,SI interposer 用于实现芯片之间焊盘的电气连接 。这些芯片既可以采用 TSV (支持进一步堆叠),也可以不包含 TSV (此类芯片无法进一步堆叠,通常为倒装芯片)。2.5D 结构 使用SI interposer ,而3D-IC 结构 在有源硅 中集成 TSV,形成完整的 3D 堆叠。

硅通孔(TSV) 是一种贯穿芯片衬底 或硅中介层 的过孔。通常,在包含 TSV 的芯片中,器件和金属层制造于芯片的一侧(正面) ,而额外的金属层则制造于芯片的另一侧(背面) 。正面金属层的制造工艺节点通常比背面金属层更先进 。可通过称为ubump的焊料小球实现多芯片之间的连接,详见图 1-1。

图 1-1. 基于 TSV 的 3D-IC 横截面

图 1-1. 基于 TSV 的 3D-IC 横截面

Calibre 3DSTACK 通过扩展现有 Calibre 验证流程 来支持上述结构的验证。现有 Calibre 流程独立处理每个设计 ,而 Calibre 3DSTACK 则专注于设计之间的接口验证 。设计的装配依据 3DSTACK 规则文件 中的指令完成,包括 x/y 轴偏移量 、旋转角度 和放大系数。

例如,在图 1-2 中,两个设计(chip1 和 chip2)需装配在一个SI interposer 上。为完成DIE 堆叠,chip2 需沿 x 轴偏移 x_offset,SI interposer 需顺时针旋转 90 度 。图 1-2 总结了 3DSTACK 装配操作所需的输入 和输出。

图 1-2. 3DSTACK 装配

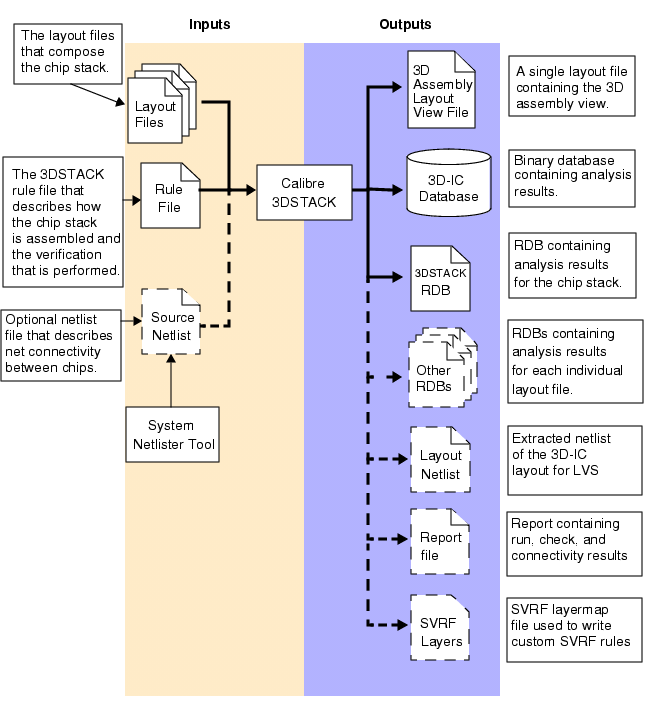

图 1-3 展示了 Calibre 3DSTACK 支持的输入文件 和生成的输出文件 。可通过 3DSTACK 规则文件中指定的命令,对装配完成的芯片堆叠执行尺寸检查(DRC)和连通性操作(LVS)。

图 1-3. 输入与输出

下图展示了使用 Calibre 3DSTACK 验证设计的典型工作流程。

图 1-4. Calibre 3DSTACK 流程

二. 3D-IC 描述语言使用限制

使用 Calibre 3DSTACK 工具的规则文件语言时,必须遵守特定的使用要求。

本文包含来自 3D-IC 描述语言(3DIC_DL) 的代码,该语言由 Mentor Graphics 产品使用,用于支持 2.5D/3D IC 应用。

三、需求条件

运行 Calibre 3DSTACK 工具前,必须完整安装 Calibre 并拥有相应的许可证 。堆叠中的所有芯片必须已通过 DRC 和 LVS 验证。

必须具备以下 Calibre 许可证:

-

Calibre nmDRC-H 和 Calibre nmDRC

-

Calibre nmLVS-H 和 Calibre nmLVS

-

Calibre DESIGNrev

-

Calibre RVE(强烈建议用于调试结果)

必须设置 CALIBRE_HOME 或 MGC_HOME 环境变量,指向 Mentor Graphics 软件目录的位置。有关详细信息。

必须定义以下输入:

-

组成 3D assembly 的版图文件 :版图格式需为 GDS、OASIS®¹ 或 LEF/DEF 。单元和引脚名称不得包含空格,否则会导致导出的网表出错。

-

有效的 Calibre 3DSTACK 规则文件:rule file 以及标准 Tcl 结构。

-

芯片堆叠的源网表 :必须选项