SoC(片上系统)里"系统总线与互连"部分包含的 4 个硬件模块,一句话概括:它们一起保证 AXI 总线"跑得快、不堵车、还能事后查问题"。逐条翻译+解释如下:

-

Network interconnect (NoC) AXI arbiter

中文:网络互连型 AXI 仲裁器。

作用:芯片里几十个主设备(CPU、GPU、DMA、ISP、AI 核...)都要访问内存或外设,这个仲裁器决定"谁先走、谁后走",并按 AXI 协议把数据包路由到对应从设备,相当于十字路口的智能红绿灯+高架桥。

-

Quality of service controller (QoSC)

中文:服务质量控制器。

作用:给不同主机设"优先级 + 带宽上限"。例如把 GPU 设为高优先级,保证图形不卡顿;把后台 DMA 设低优先级,防止它把总线吃光。简单说就是"VIP 车道 + 限速牌"。

-

Performance monitor (PERFMON)

中文:性能监视器。

作用:实时统计每条 AXI 通道的吞吐、延迟、拥塞次数,软件可以读出这些数据,知道"哪段路在堵车",用于后期性能调优。

-

Debug monitor (DBGMON)

中文:调试监视器。

作用:在系统死机或重启前,自动把最近若干条 AXI 事务(地址、长度、读写类型、主设备 ID 等)录下来,工程师事后就能像查"行车记录仪"一样,定位是谁发了非法地址或把系统卡死。

总结:

这 4 块逻辑合起来,让 SoC 内部的高速总线既跑得快(仲裁+QoS),又能量得清(PERFMON),还能查得出问题(DBGMON)。

SoC 里"时钟和复位"子系统的顶层设计目标,翻译成大白话就是:

"让全芯片的时钟和复位既'省电线'又好配置,还要让多核/多外设互不干扰。"逐条拆开说:

-

Clock control module (CCM)

中文:时钟控制模块。

作用:一个集中式"时钟总机"。所有 PLL、分频器、门控开关都归它管,软件只需写它的寄存器,就能打开/关闭或切换任何模块的时钟,而不用到处找分散的寄存器。

-

Simplified clock tree structure

中文:简化的时钟树结构。

作用:把以前"PLL→多级分频→再分频→再门控"的复杂树状图,砍成"根时钟(root clock)→叶子"两层,硬件走线少,时钟抖动和 skew 也更容易控制。

-

Unified clock programming model for each clock root

中文:每个时钟根采用统一编程模型。

作用:不管是 CPU 根时钟、还是 USB、GPU、AI 根时钟,寄存器位域都一样:使能位 + 分频系数 + 选择开关。驱动工程师记住一套 API 就能配完全片,减少"踩坑"。

-

Multicore awareness for resource domains

中文:支持多核资源域感知。

作用:把时钟/复位按"域"划分,例如 Cortex-A 域、Cortex-M 域、外设域。各核可以独立开关自己域内的时钟或复位,不会误伤别人;做低功耗时,A 核休眠掉自己的域,M 核还能继续跑。

-

System reset controller (SRC)

中文:系统复位控制器。

作用:统一产生"上电复位、按键复位、看门狗复位、软件复位"等各种复位源,并按域分级送出。比如只复位 USB 子系统,而 CPU 不跑飞;也能做"一次性全芯片复位"。还提供复位状态寄存器,软件一读就知道"上次是谁把我重启的"。

总结:

CCM + 简化时钟树 + 统一寄存器模型,让"时钟"又好配又省电;

SRC + 多核域隔离,让"复位"既灵活又安全。

整套机制的目的就是:减少走线、降低功耗、方便软件、支持多核异构场景。

把这段话翻译成一句人话:

"芯片给 160 条外设中断配了'双路电梯'------A53 走 GIC,M7 走 NVIC;另外放 3 台一模一样的'智能 DMA'搬运工,1 号干杂活,2、3 号专职给音频通道扛数据。"

逐条拆开说:

-

160 条共享外设中断

- 所有外设(USB、以太网、SPI...)的中断线先汇到一条"总中断池",一共 160 根。

- 然后同时接到两个 CPU 的 interrupt controller:

-- Cortex-A53 端:ARM 公版 GIC(Generic Interrupt Controller),支持优先级、亲和性,可以把中断动态分给 4 个 A53 核。

-- Cortex-M7 端:NVIC(Nested Vectored Interrupt Controller),实时核用, latency 低,嵌套优先级硬实时。 - 好处:同一根中断线,既能让 Linux 在 A53 上响应,也能让 RTOS 在 M7 上响应,软件想怎么拆就怎么拆。

-

Smart DMA(SDMA)引擎

- 3 颗硬件微码 DMA 控制器,内部固件可编程,支持链表、循环缓冲、scatter-gather、自动流控。

- 三颗完全同构,但复位后分别绑定到不同外设,避免"抢通道"。

-

SDMA-1:通用搬运工

- 给"慢速"外设打杂:UART、SPI、I²C、CAN、PWM、ADC...

- 典型场景:115200 bps UART 连续收 1 KB 数据,CPU 睡觉,SDMA-1 帮你搬进内存,完成后发中断。

-

SDMA-2 / SDMA-3:音频专用搬运工

- 固定给音频接口:SAI-1/2/3/5/6/7、SPDIF-Rx/Tx、PDM 麦克风输入。

- 支持 8~32 bit、8 kHz~384 kHz、TDM、I²S、左对齐、DSP 等各种格式;可以双缓冲循环,实现 0 CPU 占用的 "录音 → 内存 → 回放" 链路。

- 两颗分开:可以同时跑不同采样率,例如 SDMA-2 录 48 kHz PDM 麦克风,SDMA-3 把 192 kHz Hi-Res 音乐送到 SPDIF,互不干扰。

一句话总结:

160 根中断线两头接,Linux 和 RTOS 都能用;3 台智能 DMA 分工明确------1 号打杂,2、3 号专职跑音频,全程几乎不用 CPU 抬手。

把这三段话翻译成"人话"就是:

"芯片里先给你塞了几块'小内存'当应急仓库;外面能接的内存/闪存花样很多,从高速 LPDDR4 到便宜的 SPI NOR 都能用;定时器方面,每个核自带'跑表',还额外给你 6 个通用定时器、3 条看门狗、4 路 PWM,够你折腾。"

逐条拆开说:

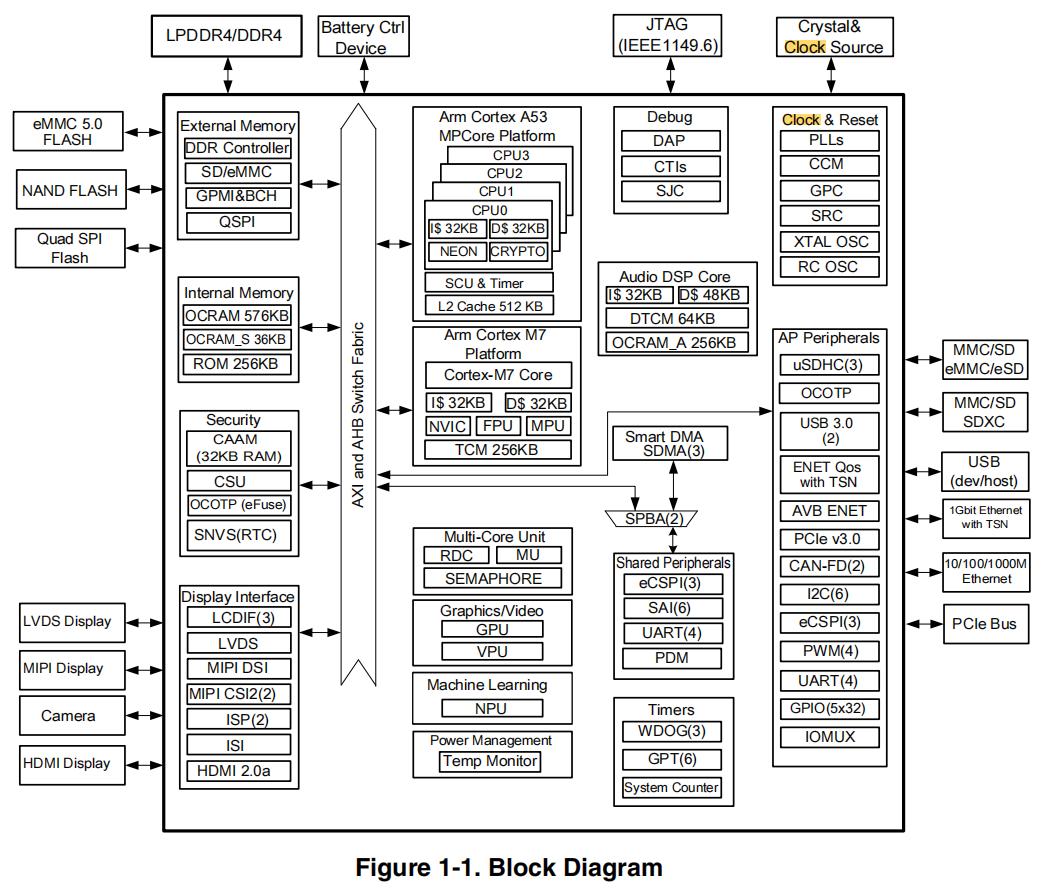

1.4.2.6 片上内存(On-Chip Memory)

- Boot ROM 256 KB

上电后第一条代码一定从这里跑,固化了芯片厂商的 bootloader,负责把外部 Flash 里的镜像搬到 DRAM 再跳过去,用户改不了。 - OCRAM 576 KB

普通"高速片上 SRAM",CPU 都能访问,常用于 DMA 缓冲、RTOS 代码段、或者 Linux 的 TCM 映射。 - OCRAM_A 256 KB

专给音频 DSP 或 Cortex-M7 用的"音频 RAM",做 48 kHz/192 kHz 低延迟链路时,把代码/数据放这里,省得和 A53 抢外部 DRAM 带宽。 - OCRAM_S 36 KB

"掉电保持 RAM",支持深睡状态 retention:主电源关掉,只留 0.9 V 待机电源,这 36 KB 数据不会丢,醒来接着用,适合存系统状态/用户数据。

1.4.2.7 外部存储接口

- 32 位 DRAM 口

-- LPDDR4-4000:等效 4 Gb/s/pin,带宽 16 GB/s(32 bit×2 ch),跑 Android/Linux 主内存。

-- DDR4-3200:桌面级条子也能接,成本更低,带宽 12.8 GB/s。 - 8 bit NAND(Raw SLC/MLC)

支持 62 bit BCH ECC,ONFi3.2 标准,100 MHz 时钟,实际裸片速度 ≈ 200 MB/s,做大容量廉价存储。 - eMMC 5.1 ×2

双路,可以一路焊 64 GB 给系统,一路留焊盘给用户扩展。 - SPI NOR ×3

存放 bootloader、裸机固件,容量 8--256 Mb,最简单便宜。 - FlexSPI

单颗 Octal-SPI(8 线)或两颗 Quad-SPI 并联,支持 XIP(eXecute In Place)。

低功耗模式下可把 DRAM 断电,代码直接在 FlexSPI Flash 里跑,唤醒更快。

1.4.2.8 定时器

- 每个 Cortex-A53 自带"Local Generic Timer"

ARM 架构标配,64 bit,向下计数,用于 Linux hrtimer / sched clock。 - Global System Counter + Timer-bus

全芯片统一节拍,4--100 MHz 可配,给所有 A53 提供同步的"墙上时间"。 - Cortex-M7 自带 SysTick

RTOS 心跳,12 MHz 起步,中断 latency 极低。 - 6 个通用定时器(GPT)

32 bit 向上/向下计数,可产生中断、输出比较、PWM、输入捕获,给裸机或 Linux 当"多路秒表"。 - 3 个看门狗(WDOG)

可设超时 0.5--128 s,支持中断→复位两级,防止系统死机;也能在深度睡眠下继续计数,做唤醒源。 - 4 路 PWM

16 bit 精度,占空 0--100 %,频率从几 Hz 到几十 MHz,能驱动 LED、马达、背光,也支持互补输出带死区,直接驱动半桥。

一句话总结:

片内先给你 1 MB+ 的"应急仓库",外面从高速 LPDDR4 到便宜 SPI NOR 全兼容;定时器从每核私藏"跑表"到 6 路通用、3 条狗、4 路 PWM,数量管够,随便你玩操作系统、音频、电机控制还是低功耗休眠。

一句话总结:

这颗芯片自带"三管炮"------3 个 LCDIF 显示控制器,分别接 MIPI 屏、LVDS 屏、HDMI 屏;同时留给摄像头"两双眼睛"------2 个 MIPI CSI + 2 个 ISP,单摄可冲 12 MP@30 fps,双摄各跑 1080p80;HDMI 口是 2.0a 标准,4Kp30 无压力,还顺带送 32 路音频输出和 1 路 eARC 回传。

逐条拆开说:

显示输出(Display)

-

三个 LCDIF 控制器

- LCDIF0 → MIPI DSI(4 data lanes)

- LCDIF1 → LVDS Tx(可拼成 4 lane 或 8 lane)

- LCDIF2 → HDMI 2.0a Tx

每个控制器只支持"单图层(one layer)",没有硬件合成,简单直接。

-

带宽分配

- 同时开 ≤2 路:每路最高 1920×1200@60 Hz

- 三全开:

-- HDMI 可上到 4K@30 Hz

-- 另外两路各跑 1080p@60 Hz

总像素率受总带宽限制,官方给出"2×1080p60 + 1×4Kp30"是同时跑的上限。

-

像素格式

8/16/18/24/32 bpp 都支持,RGB 顺序可配,方便直接接不同屏。

摄像头输入(Camera)

-

MIPI 接口

- 1×MIPI DSI(4 lane)------仅做显示

- 2×MIPI CSI(各 4 lane)------专收摄像头数据

单条 CSI 最大 1.5 Gbps/lane,4 lane 合计 6 Gbps,足够 4K raw 数据。

-

ISI(Image Sensor Interface)

一个轻量级"并口摄像头"接口,支持 BT.656/1120 等,最多 2 路,数据直接 DMA 进内存,适合低成本 CCD/CMOS 模块。

-

双 ISP(Image Signal Processor)

- 单摄模式:12 MP@30 fps 或 4K@45 fps(含去噪、WDR、3A)

- 双摄模式:每路 1080p@80 fps,独立 3A 流水线

ISP 输出可送给内存,也可直通 LCDIF 做"取景器"预览。

音频(Audio)

- HDMI 2.0a 内部带 32 通道音频流(8 路 I2S 时序打包),可输出 24-bit/192 kHz 多声道 PCM 或压缩 Bitstream(AC3/TrueHD/Atmos)。

- 1 路 S/PDIF 反方向做 eARC(Enhanced Audio Return Channel),让电视把高码率音频回传到芯片,省掉额外光纤或 I2S 线。

能做什么产品?

- 单屏 4K 机顶盒:HDMI 4Kp30 输出,一路 MIPI DSI 做前面板小屏。

- 双屏车载中控:LVDS 1080p 仪表 + MIPI DSI 1080p 中控屏,再加 2×1080p 摄像头做 AVS 全景。

- AI 相机:12 MP 传感器 + ISP,4K@45 fps 编码,HDMI 2.0 本地回放,eARC 把电视声音拉回芯片做远场语音。

一句话:

芯片给你"三屏三接口、双摄双 ISP、4Kp30+1080p80 全拿下",还带 32 声道 HDMI 音频和 eARC 回传,做车载、工控、AI 相机、机顶盒都够用。

一句话总结:

芯片里给你"一条高速 PCIe 3.0 万能扩展口 + 两个 USB 3.0 Type-C 全能口 + 三张高速存储卡槽 + 双千兆网(其中一路带 TSN 实时以太网)+ 2 路汽车 CAN-FD + 4 串口 + 6 I²C + 3 SPI",做工业网关、车载电脑、边缘服务器、NAS、工控主板都能直接出接口,不用再外挂桥接芯片。

逐条拆开说:

- PCIe 3.0 ×1(单 lane)

- 速率 8 GT/s,实测带宽 ~1 GB/s。

- 可软切 Root Complex(主)或 Endpoint(从),方便:

-- 当主机时插 NVMe SSD、AI 加速卡;

-- 当从机时把自己做成"PCIe 外设"插到 x86/ARM 主机里。 - 片内集成 PHY,省一颗外置 SerDes;支持 L1 substate,深睡时 1 mW 级别。

- USB 3.0 Type-C ×2

- 每路 5 Gbps,向下兼容 USB 2.0 HS/FS/LS。

- 集成 PHY + SS(spread-spectrum)时钟,降低 EMI,直接出 Type-C 母座。

- 可配置成:

-- 双独立 Host,同时挂 SSD + 4G 模块;

-- 一个 Host + 一个 Device(USB 网卡/声卡模式);

-- 支持 USB-PD 2.0 信号采样,外挂 PD 控制器就能 9 V/15 V 供电。

- uSDHC ×3(Ultra Secure Digital Host Controller)

- 都符合 MMC 5.1,支持 HS400 DDR 模式,单卡最高 400 MB/s,可直接焊 eMMC 当系统盘。

- 同时向下兼容 SD/SDIO 3.01,200 MHz SDR,100 MB/s,接 Wi-Fi/BT 模块或 1 TB SDXC 卡。

- 三路同时跑:

-- uSDHC0:eMMC 系统盘

-- uSDHC1:SD 卡槽用户扩展

-- uSDHC2:SDIO Wi-Fi/BT 组合卡

- 双千兆以太网

- MAC0:传统 GE,带 EEE(节能)、AVB(音视频桥接)、IEEE1588 PTP 精准对时。

- MAC1:GE + TSN(Time-Sensitive Networking),支持 802.1Qav/Qbv/Qbu 等实时队列,工业环网、汽车以太网、运动控制总线刚需。

- 两路可同时工作,做冗余或"LAN + WAN"隔离。

- FlexCAN ×2

- 每路支持 CAN 2.0B 与 CAN-FD(数据段 8 Mbps),128 组滤波器。

- 适合车载 ECU、工业 CAN-open、DeviceNet;也能做 CAN 网关转发。

- 低速串行接口

- UART ×4:最大 4 Mbps,带 64 byte FIFO、RS-485 自动方向、9-bit 多机。

- I²C ×6:最高 1 MHz(Fast-mode Plus),支持 7/10 bit 寻址、多主、SMBus 报警。

- SPI ×3:每路 4 片选,时钟 52 MHz 起,支持主/从、双线/四线 DTR,接 FLASH、ADC、OLED 都行。

典型应用组合

- 工业边缘计算机:

PCIe 插 NVMe 做系统盘,USB3.0 接 AI 相机,TSN 以太网进环网,CAN-FD 连伺服驱动,SD 卡做现场数据备份。 - 车载中控+网关:

CAN-FD 连 ECU,TSN 以太网做骨干网,USB3.0 Type-C 接 CarPlay,eMMC 跑 Android,PCIe 外挂 V2X 通信模组。 - 4G/5G 路由网关:

一路 USB3.0 接 5G 模块,一路 PCIe 插 Wi-Fi 6E 卡,双千兆以太网做 LAN/WAN,SD 卡存日志,UART 调试,I²C 挂环境传感器。

一句话:

这颗片把"高速扩展 + 高速存储 + 实时网络 + 车载总线 + 低速串口"一次性配齐,做单板计算机、工业网关、车载域控、边缘 NAS,都能直接出接口,省桥接、省 BOM、省 PCB 面积。

一句话总结:

芯片里盖了一座"硬件保险箱"------TrustZone 把 CPU 分成"安全世界/普通世界",RDC 把内存和外设切成 4 间"带锁包间";CAAM 专职做 RSA/ECC/AES/3DES 加解密加速,还能跑 Widevine/PlayReady 版权保护;HAB 把关启动链,RTIC 实时盯梢内存完整性,RNG 出真随机数,SNVS 把密钥和 RTC 放进"电池看守的保险柜",SJC 让 JTAG 调试口只能凭钥匙打开------从开机到运行,数据、代码、版权、调试口全有硬件级守护。

逐条拆开说:

- RDC(Resource Domain Controller)

- 把整个芯片的内存、外设地址空间切成 4 个"域"(Domain)。

- 每个域最多 8 段区域,可独立设"安全/非安全、CPU 核可见、读写权限"三把锁。

- 举例:Linux 跑在 Domain-0,CAN-FD 控制器只分给 Domain-2,即使 Linux 被黑也摸不到车控总线。

- Arm TrustZone

- Cortex-A53 四核自带 TZ,把世界切成 Secure World(安全)和 Normal World(普通)。

- 安全世界里跑 OP-TEE / Trusty / 厂商 TEE,普通世界跑 Android/Linux。

- OCRAM 控制器可把 576 KB 片上 RAM 划一块"仅安全世界可访问",存密钥、指纹模板都不怕主系统偷窥。

- HAB(High Assurance Boot)

- ROM 里的第一段启动代码会校验 SPL/TF-A 的 RSA/ECC 签名;签名不对直接拒绝启动,防止刷入恶意 bootloader。

- 可配置"闭合模式"------以后只认厂商私钥签过的固件,彻底堵死刷机漏洞。

- CAAM(Cryptographic Acceleration & Assurance Module)

- 硬件黑盒子,带 32 位描述符引擎,DMA 级吞吐。

-- 对称算法:AES-128/256、3DES、DES、RC4

-- 哈希/完整性:SHA-1/256/384/512、MD5

-- 公钥:RSA 2048/3072/4096、ECC P-256/384/521

-- 真随机数:符合 NIST SP800-90B/C,可用于密钥、nonce、token - 支持 DRM 场景:

-- Widevine L1/L3:在线视频 4K HDR 解密,密钥留在 CAAM 内部 RAM,主 CPU 永远拿不到明文密钥。

-- PlayReady、Studio DRM:Netflix/Disney+ 等正版内容秒开。 - 制造保护:芯片出厂时熔丝写入公钥哈希,CAAM 只认该公钥,OEM 也无法替换,防止"山寨机"克隆。

- RTIC(Real-Time Integrity Checker)

- 在后台用 DMA 把指定内存块轮询哈希(SHA-256),与预期值比对。

- 发现篡改立即触发安全中断,可自动复位或记录日志------相当于"硬件看门狗"盯着代码/数据完整性。

- SNVS(Secure Non-Volatile Storage)

- 包含:

-- 电池后备的 32 字节"安全寄存器"------存主密钥、解锁令牌,掉电/主复位也不丢。

-- Secure RTC(SRTC)------即使系统深睡,仍继续走时,防篡改时间戳。 - 安全状态机:检测到物理拆机、电压攻击、温度攻击可自动"零化"密钥。

- SJC(Secure JTAG Controller)

- JTAG 调试口默认被锁;需要 256-bit 密钥或挑战-响应才能打开。

- 产线测试完后可把密钥烧断,彻底封死调试,防止逆向。

典型安全场景

- 移动支付 POS:TEE 在 Secure World 跑银联/EMV 内核,CAAM 做 RSA 签名,主系统即使被植入木马也摸不到私钥。

- 4K 机顶盒:HAB 确保 bootloader 未被替换,CAAM 实时解密 Widevine 流,RTIC 每小时校验一次 DRM 库完整性。

- 车载网关:RDC 把 CAN-FD 与娱乐域隔离,SNVS 存车辆证书,安全 OTA 升级包必须 RSA-4096 验签才能写 eMMC。

- 工业网关:TrustZone + SNVS 保存 VPN 证书,CAAM 硬件 TLS 加速,掉电仍保持正确时间戳,防止"重放攻击"。

一句话:

从"启动链 → 运行隔离 → 加解密加速 → DRM 版权 → 密钥保存 → 调试锁死"全链路硬件保险,让代码、数据、版权、时间戳、调试口都在保险箱里完成,即便主系统被攻破,核心资产仍跑在"安全世界"里拿不走、改不了、拖不垮。

把 4 句话翻译成"人话"就是:

"多核一起干活时,芯片里放了三件'交通设施'------RDC 先给各核划'隔离带',谁只能进哪条道写死在硬件;MU 让核之间像'发快递'一样互扔短消息;SEMA4 提供'一把原子钥匙',保证同一时刻只有一个核能进共享房间;最后所有核都挂在同一套 AXI 高速公路上,既能快速互通,又不会因为抢道撞车。"

再拆开一句话:

- RDC:硬件白名单,把内存、外设切成 4 间"包间",A53、M7、DSP 只能按表进出,互不干扰。

- MU:每对核之间 4~16 个邮箱,写 32 bit 数据就触发中断,1--2 µs 送到,跨核通信不用绕内存。

- SEMA4:32/64 把硬件锁,一条指令"抢钥匙/还钥匙",谁抢到谁用共享资源,不会同时写乱数据。

- Shared bus:所有主设备(A53、M7、DSP、DMA...)共用 AXI 交叉矩阵,物理上同一条总线,逻辑上靠 RDC 限权,既省拷贝又能 QoS 保实时。

总结:

"先分区再上锁,有事写信别抢道"------让多核异构既能安全隔离,又能高效协作。

一句话:

"GPIO 就是能当普通按钮灯控的万能引脚,中断秒响应;IOMUXC 是'引脚大管家', centrally 决定每个引脚今天当 GPIO、明天当 UART、后天当 SPI------全部软件可配,省得焊死。"

拆开说:

- GPIO 模块

- 每组 32 位,每位可独立设输入/输出/开漏/推挽。

- 带边沿/电平中断,可唤醒深睡,适合做按键、LED、IRQ 触发。

- IOMUXC(Input/Output Mux Controller)

- 把"封装焊盘"与"内部外设信号"之间加了一张交换表。

- 寄存器里选 ALT0→ALT7,一键把同一个焊盘切成:

ALT0 = GPIO

ALT1 = UART_TX

ALT2 = SPI_MOSI

ALT3 = PWM... - 还顺手配上下拉、驱动能力、摆率、开漏、保压,全集中在一个模块,软件开机一次配完。

结果:

引脚数量固定,功能随意"切屏",硬件设计不用改线,软件按需开局------省 BOM、省层数、省返工。

一句话:

芯片里自带"温度计+电闸开关"------温度传感器可设多级高温报警,先降频再断电;各功能模块被划进不同"供电分区",用内部电源开关单独拉闸/送电,闲置区域直接黑灯,省电又防烫。

一句话:

芯片里埋了一套"CoreSight 全科诊断仪"------A53 四核和 M7 共用同一条跟踪高速通道,4 KB ETF 缓存随时记录指令流水;CTI 让多核之间"你停我也停",5-pin JTAG 口插进去就能单步、断点、看寄存器/内存,生产调试、现场除错、性能分析一次搞定。

一句话:

i.MX 8M Plus 上电后"只认 A53 老大"------先从你选的 NAND/eMMC/SPI 等介质里把 A53 镜像拉进来,走完安全校验(HAB)再启动;M7 此时被"按在板凳上"等命令,直到 A53 把它的固件拷进内存、验完签名、写好寄存器后才放它跑;整个启动链由 A53 一手掌控,安全可控,顺序不可颠倒。

芯片只认"小端模式"------最低字节存在最小地址 ,数据在内存里怎么摆、怎么读,都必须按小端的规矩来;

写程序、造镜像、用协议栈,一律把大端先翻转,否则 CPU 会把你当乱码。