通过在快时钟域打拍两次实现转换,实验表明3级触发器可以避免99%的时序违例。解决FPGA不同时钟数据同步的亚稳态问题。

- 亚稳态及其传播

重点! 通过两级寄存器,即使产生亚稳态也在两个寄存器之间,降低传递到后级的概率,从而减轻亚稳态对后级影响。

理论上,亚稳态产生后持续时长是随机的,意味着永远持续下去也是可能的,然而由于实际电路中存在的噪声和能量变化等一定会让亚稳态很快产生不平衡,迅速向0或者1靠拢。举个例子,就像笔尖上放一个圆球,理论上可以找一个位置永远平衡,然而实际上由于一点点的震动都会导致圆球迅速掉下去。在时钟发射沿到来后,亚稳态产生后持续时间为Tmet,在捕获沿到来时,dout的亚稳态已经消除,这样亚稳态就不会往后级传播,也就是说亚稳态在一个时钟周期内稳定就可以防止往下一级传播。实际中亚稳态的稳定都很快。而同步器打2拍就是为了在时钟频率很高的时候,捕获沿采到亚稳态向下一级传播的时候,还有一级寄存器隔离,然亚稳态在一个时钟周期内稳定下来。

假设,亚稳态在一个时钟周期内稳定不下来的概率为P,0<P<1,那么经过一级打拍稳定下来概率为1-P,经过两级打拍稳定下来的概率为1-P^2,以此类推。所以打拍越多越容易稳定下来,防止亚稳态传播。

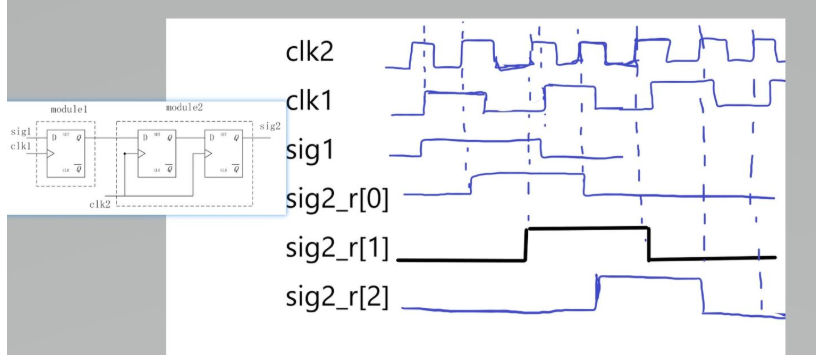

50M快时钟与异步25M慢时钟时钟域问题,通过打拍解决并且实现上升沿检测

50M快时钟与异步25M慢时钟时钟域问题,通过打拍解决并且实现上升沿检测

modelsim仿真与分析一致

modelsim仿真与分析一致

XML

module delay_clap (

input clk1 ,//slow clk

input clk2 ,//quick clk

input rst_n ,

input sig1 ,//clk1_input

output sig2 //edge_sensor

);

reg [ 2:0] sig2_r ;

always @(posedge clk2 or negedge rst_n) begin

if(!rst_n) begin

sig2_r <= 'b0;

end

else begin

sig2_r <= {sig2_r[1:0],sig1};

end

end

assign sig2 = sig2_r[1] && !sig2_r[2] ;

endmodule

//---------------------------------------------------------------------

module tb;

reg clk1 ;

reg clk2 ;

reg rst_n ;

reg sig1 ;

wire sig2 ;

always begin

clk1 = 0;

#30

clk1 = 1;

forever #40 begin

clk1 = ~clk1;

end

end

always #20 clk2 = ~clk2;

initial begin

clk2 = 0 ;

rst_n = 0 ;

sig1 = 0 ;

end

initial begin

#10;

rst_n = 1;

#20

sig1 = 1;

#80

sig1 = 0;

end

delay_clap u_delay_clap (

.clk1 (clk1 ),

.clk2 (clk2 ),

.rst_n (rst_n ),

.sig1 (sig1 ),

.sig2 (sig2 )

);

endmodule