一、引言

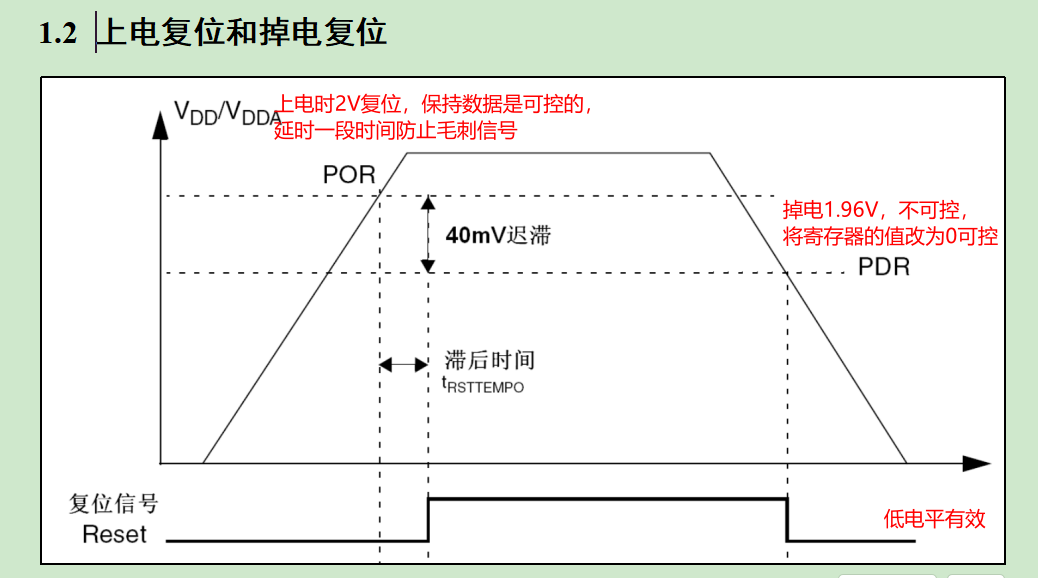

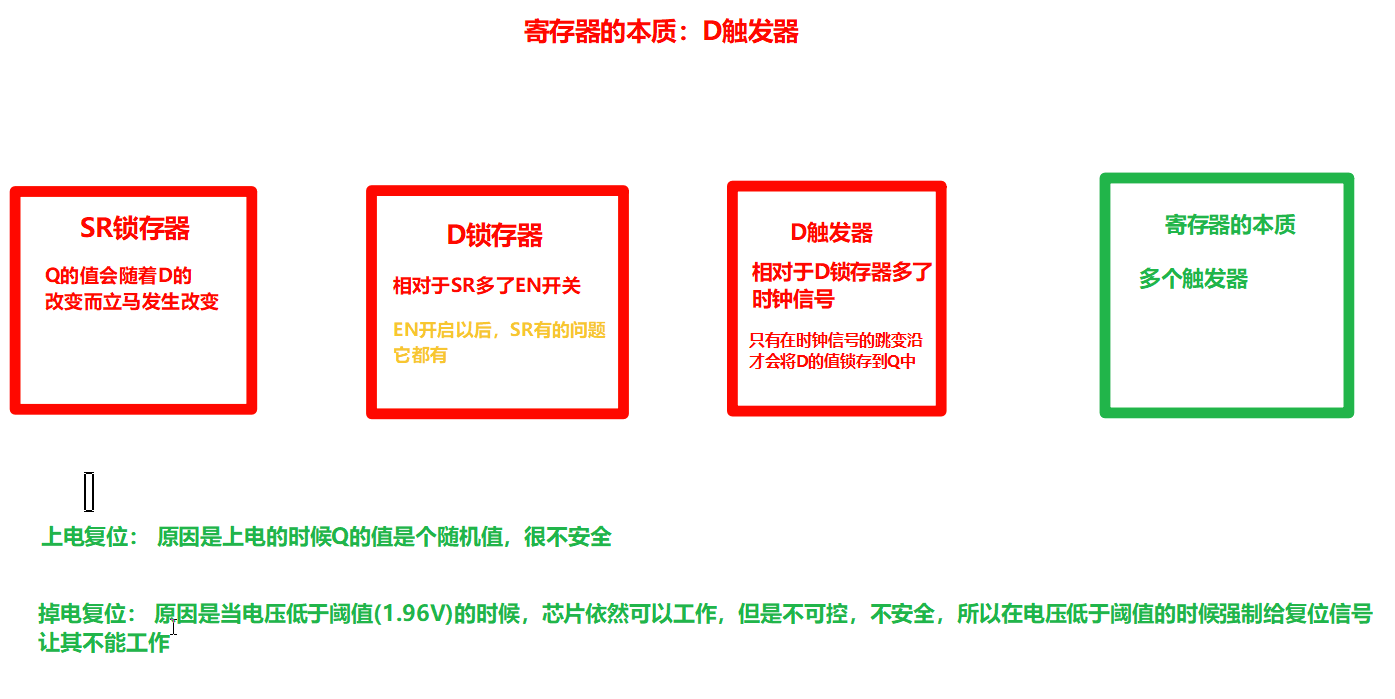

因为LED运行过程中需要清屏会出现上电复位和下电复位的概念,所以现在详细介绍下这两个概念,多少位寄存器就是多少个触发器。

上电复位POR 2V :上电把不可控的初始值刷成可控的,清空重置寄存器为可确定的值

掉电复位PDR 1.96V:强制将不确定的值置为0

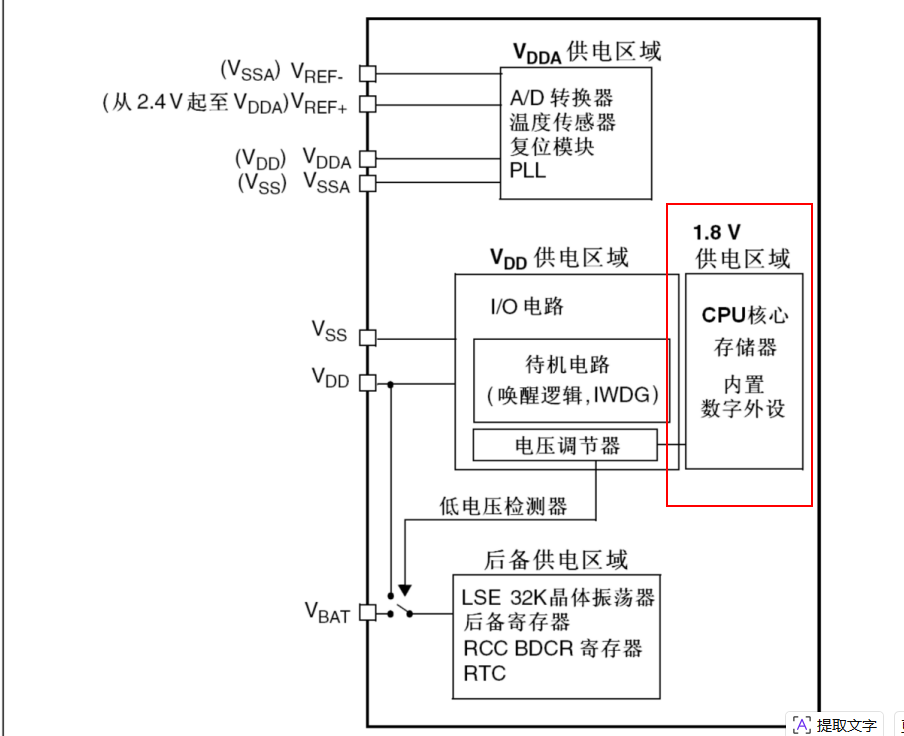

SOC 芯片一般都集成上电复位(POR)和掉电复位(PDR)功能,二者是保障芯片在电源异常时可靠启动、稳定运行的核心硬件机制,属于 SOC 电源管理模块(PMU)的标配功能。

1. 上电复位(Power-On Reset, POR)

- 触发场景:芯片接通电源时,电源电压从 0V 逐渐上升到额定工作电压(如 3.3V)。

- 核心作用 :确保电源电压稳定到芯片可正常工作的阈值后,再释放复位信号 ,让芯片从初始状态开始执行程序。

- 如果没有 POR,电源电压未稳定时芯片就可能乱执行指令,导致启动失败、程序跑飞。

- 硬件原理 :SOC 内部集成电压检测比较器,预设一个 POR 阈值(如 2.8V)。当 VDD 电压低于阈值时,复位信号有效(芯片保持复位态);当 VDD 上升到阈值并保持一段时间(去抖),复位信号释放,芯片开始启动。

2. 掉电复位(Power-Down Reset, PDR)

- 触发场景:芯片工作过程中,电源电压突然跌落(如电池电量耗尽、外部电源波动、短路等),低于安全工作阈值。

- 核心作用 :在电源电压不足以维持芯片正常工作前,强制触发复位,防止芯片因电压不足出现逻辑混乱、数据损坏(如寄存器值错乱、Flash 写入异常)。

- 硬件关联 :PDR 通常和 POR 共享同一个电压检测模块,但触发逻辑相反 ------POR 检测电压上升沿,PDR 检测电压下降沿。

- 部分 SOC 会把 PDR 细分为 欠压复位(Brown-Out Reset, BOR),本质上是同一类功能,只是命名更强调 "电压欠压" 的触发条件。

3.SOC 复位机制的补充要点

- 独立性 :POR/PDR 是纯硬件复位机制,不依赖软件配置,也不需要外部复位电路(当然可以外接复位按键做冗余)。即使芯片内部程序跑飞,只要电源异常,POR/PDR 就会强制介入。

- 复位优先级 :在 SOC 所有复位源中(POR/PDR、外部复位、看门狗复位、软件复位等),POR 优先级最高------ 芯片上电时,只有 POR 完成,其他复位源才会生效。

- 差异化配置 :中高端 SOC 会支持可编程的 BOR 阈值,比如 STM32H7 系列可以通过配置选项字节,选择不同的欠压检测阈值(如 2.1V/2.4V/2.7V),适配不同的电源稳定性需求。

4.总结

几乎所有商用 SOC 芯片都会同时集成 POR 和 PDR(或 BOR) 功能 ------POR 负责 "平稳启动",PDR 负责 "异常保护",二者共同构成芯片电源层面的第一道可靠性防线。

5.优先级

STM32 系列 SOC (主流 Cortex-M 内核)为例,整理复位源的触发条件 、核心作用 和优先级排序 ,优先级 数字越小越高,高优先级复位会覆盖低优先级复位的状态标记。

关键补充说明

- 优先级核心逻辑 :电源相关复位(POR/PDR)> 硬件复位(外部引脚)> 监控复位(看门狗)> 软件复位。原因是电源复位直接关系芯片的基础运行条件,优先级必须最高;软件复位是程序层面的操作,优先级最低。

- 复位标志查询 :SOC 会在复位状态寄存器(如 STM32 的 RCC_CSR) 中记录复位原因,程序可以通过读取该寄存器判断是哪种复位触发了启动,便于调试和异常处理。

- 跨平台一致性:其他 SOC(如 ESP32、NXP Kinetis)的复位优先级逻辑与 STM32 基本一致,差异仅在于阈值配置和寄存器命名。

q与q`区别:q`存在门电路有没有错误,特点:q与q`永远相反,只要门电路没有问题