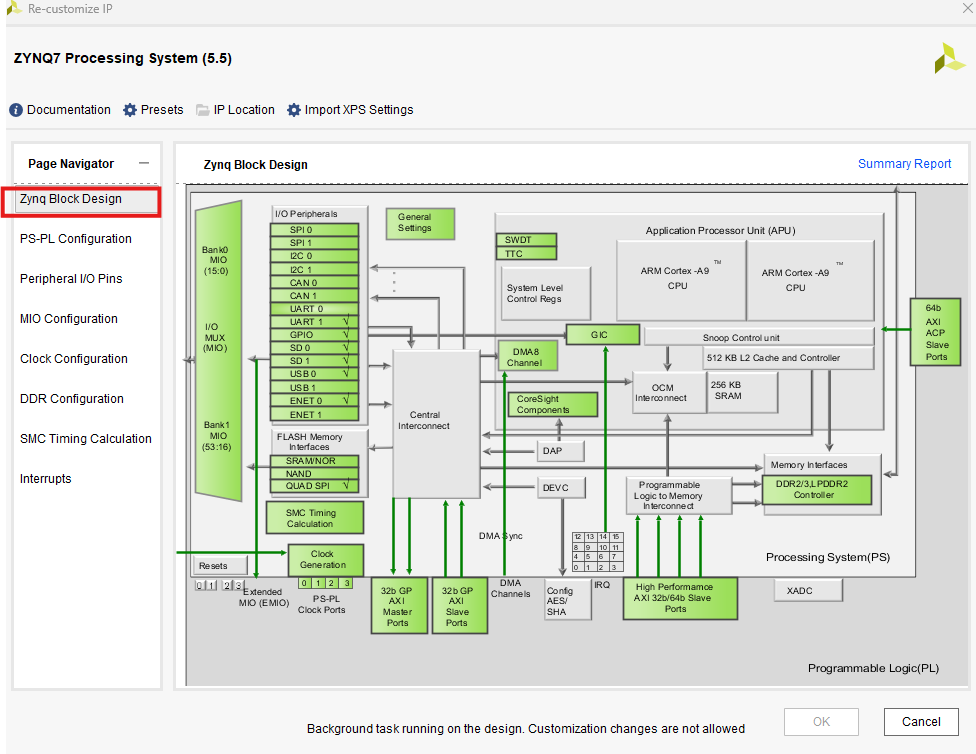

1.1 "Zynq Block Design " Tab

Zynq Block Design 页面显示了 PS 端的各种可配置块,其中灰色部分是固定的,绿色部分是可配置的,单击可配置块,可以进入相应的配置页面。

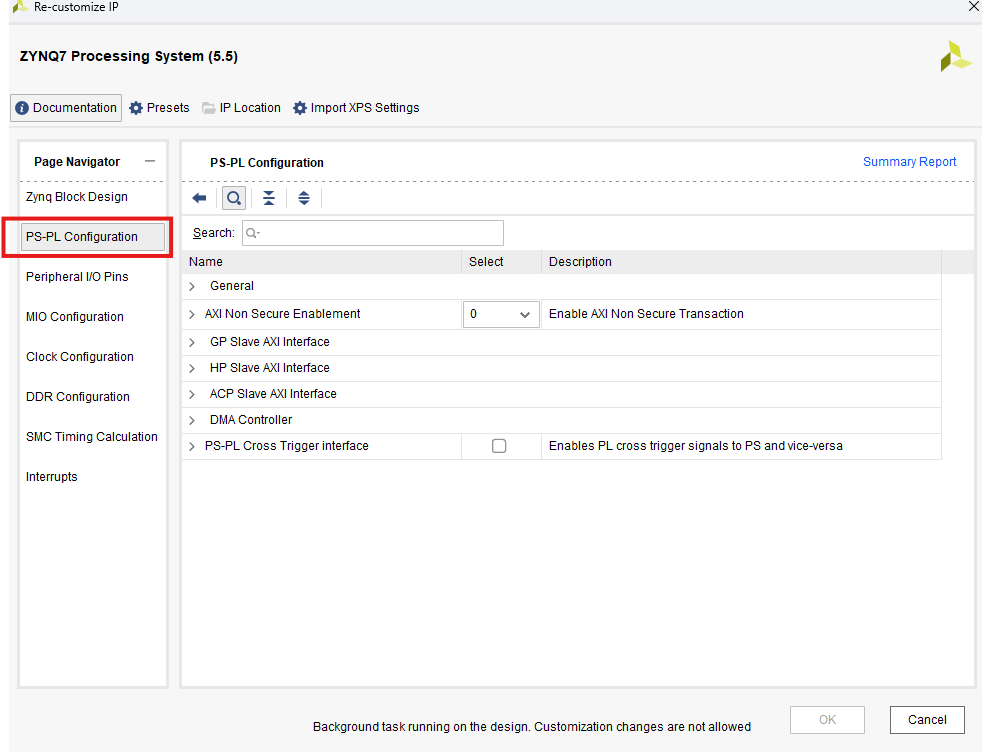

1.2 "PS-PL Configuration " Tab

PS-PL Configuration 页面用于配置 PS-PL 接口,包括 AXI、DMA 控制器 和 ACP 总线接口。

结构和配置

4个GP AXI端口:用于控制、配置、低速数据传输。

2个主接口:M_AXI_GP0, M_AXI_GP1

2个从接口:S_AXI_GP0, S_AXI_GP1

4个高性能端口:用于高速大数据量传输 (DMA, 视频流等)。

HP0, HP1, HP2, HP3 (均为从接口)

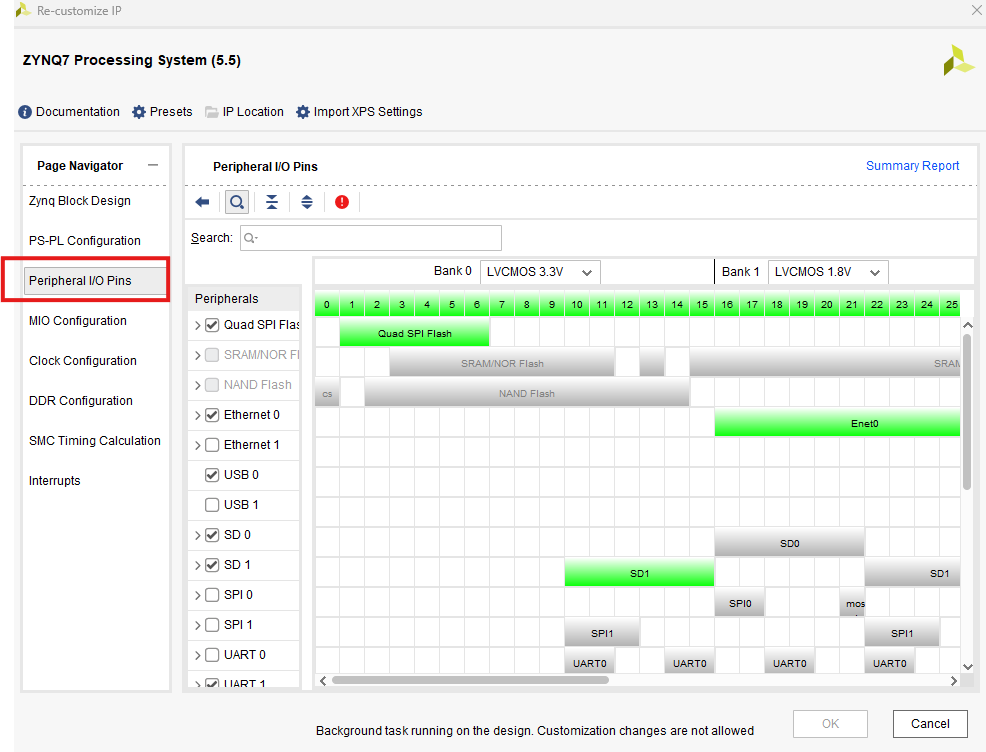

1.3 "Peripheral I/O Pins " Tab

Peripheral IO Pins 页面用于为不同的 I/O 外设配置相应 MIO/EMIO 配置。

需要根据ZYNQ芯片的原理图配置相应的PS IO。

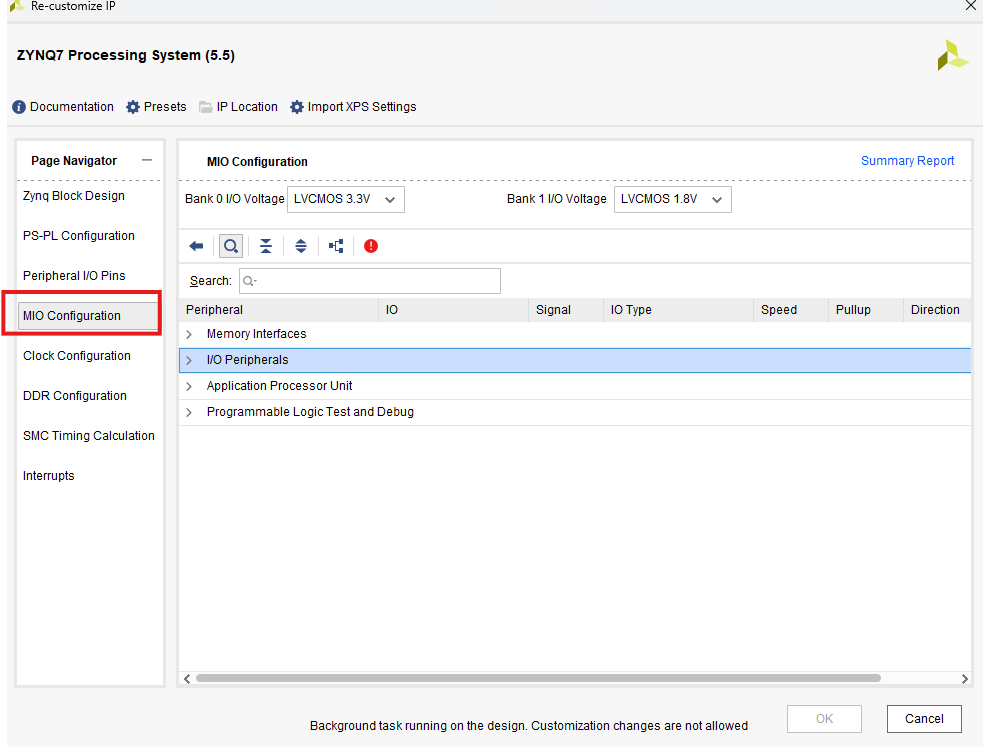

1.4 "MIO Configuration " Tab

MIO Configuration 页面用于为不同的 I/O 外设配置相应的 MIO/EMIO 引脚配置。

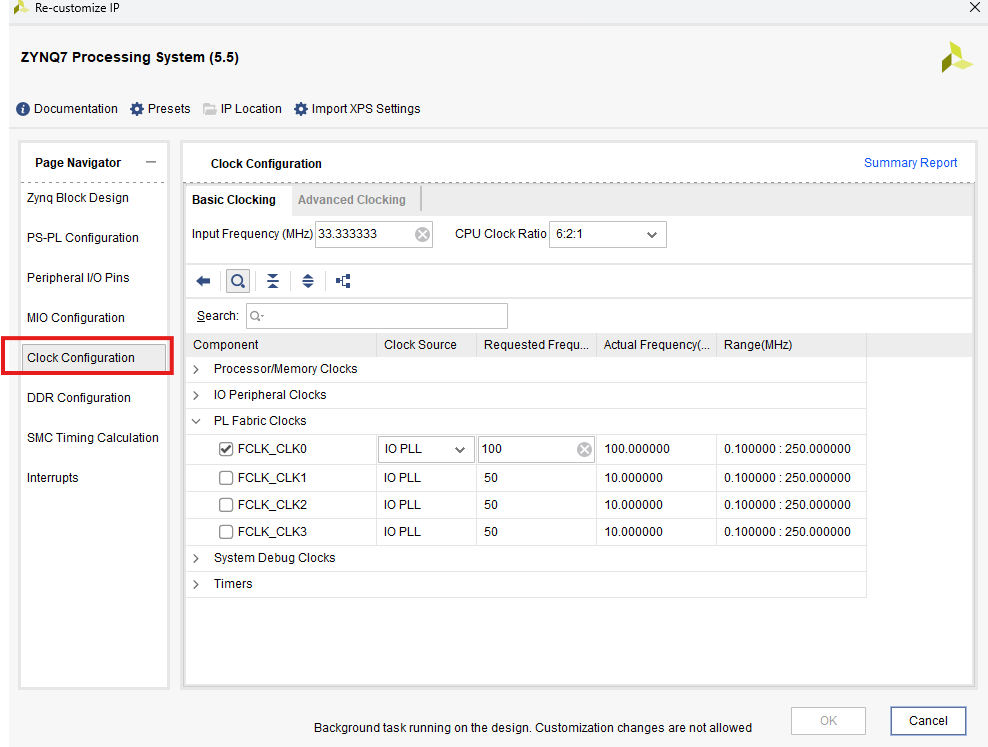

1.5 "Clock Configuration " Tab

Clock Configuration 页面用于配置处理系统 7(Processing System 7) 的外设时钟、逻辑单元时钟、DDR 和 CPU 时钟。

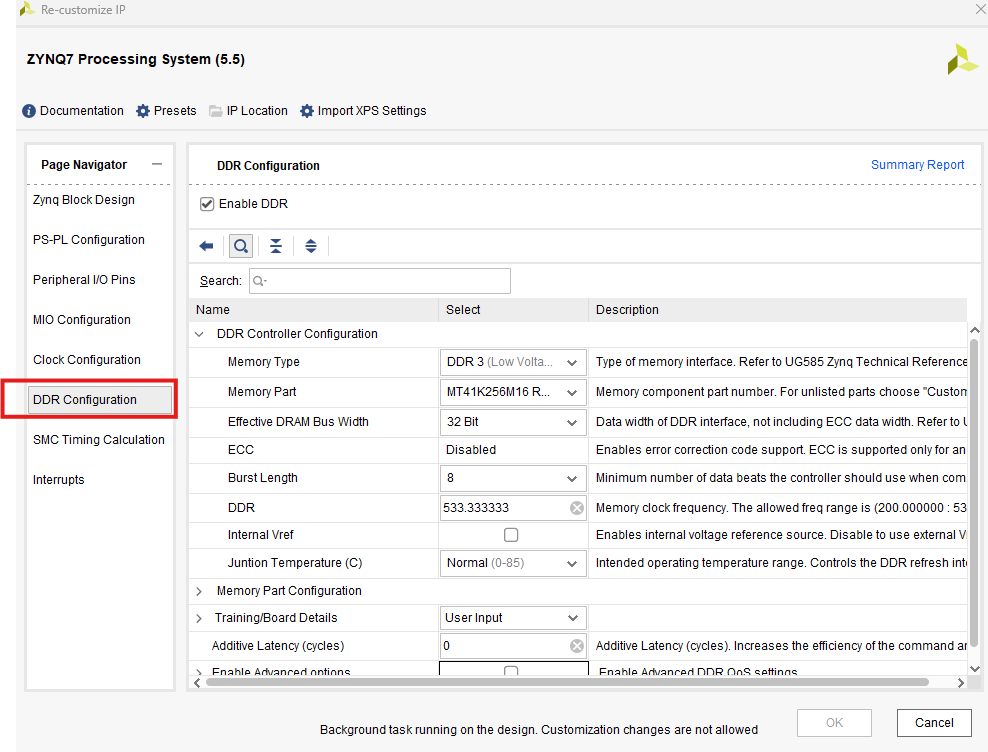

1.6 "DDR Configuration " Tab

DDR Configuration 页面用于配置用户 DDR 控制器信息。

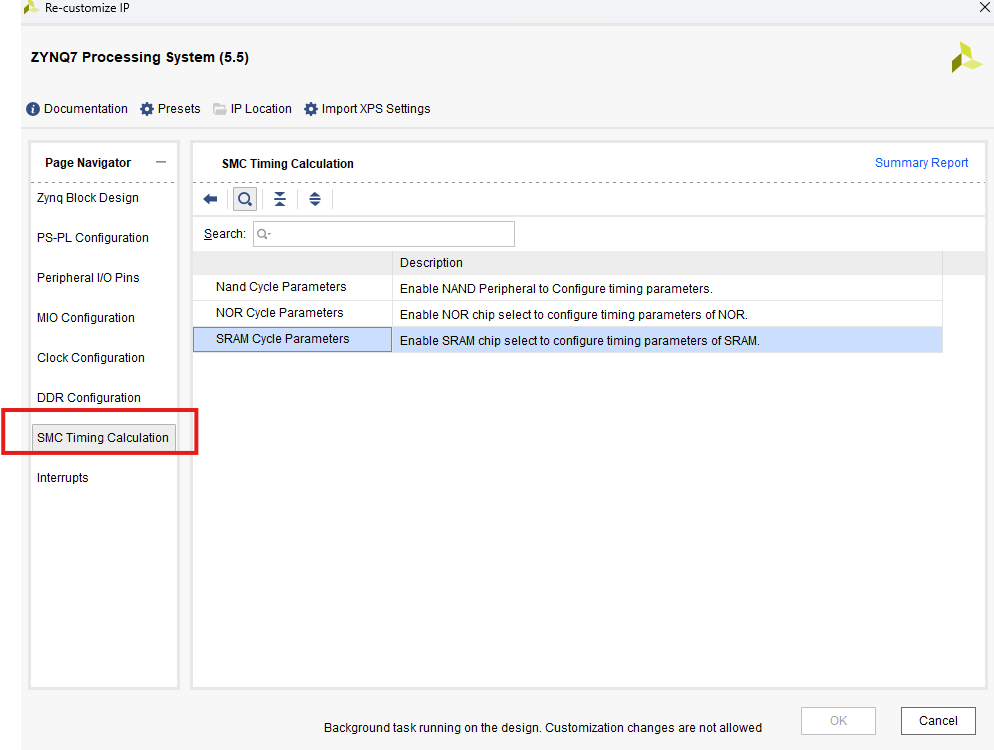

1.7 "SMC Timing Calculation " Tab

SMC Timing Calculation 页面用于执行 SMC 时序计算。

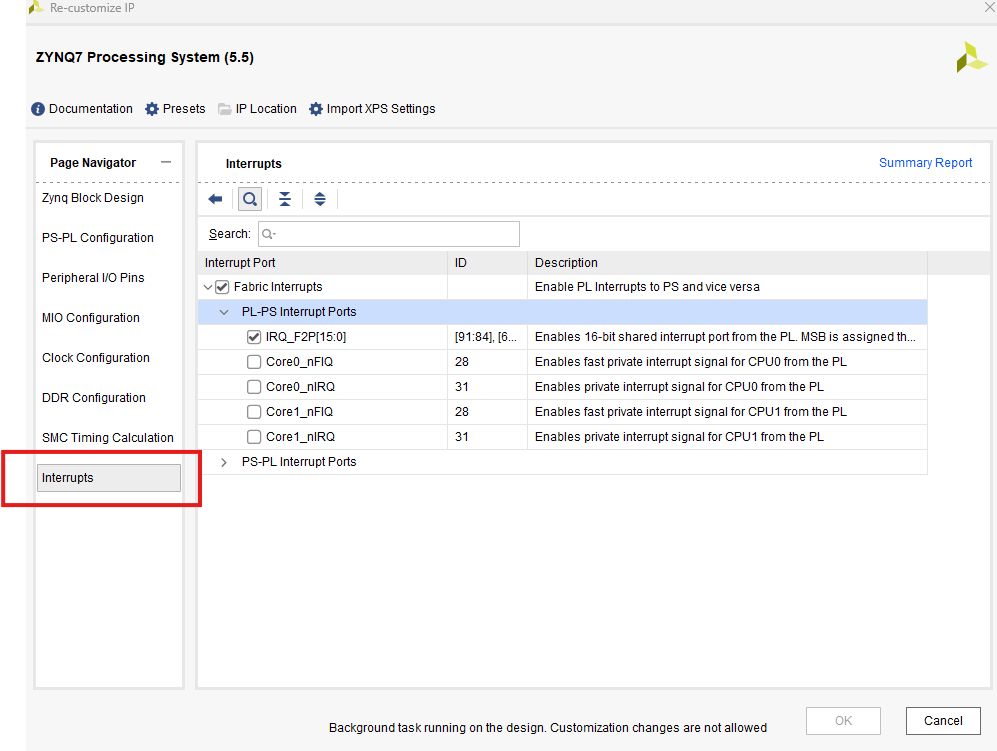

1.8 "Interrupts" Tab

Interrupts 页面用于配置 PS-PL 中断端口。