目录:

0 引言

1 什么是体系结构

2 FPGA的结构

3 FPGA的体系结构

4 FPGA的优势

5 FPGA的劣势

6 FPGA的通用应用场景

7 FPGA的特化应用场景:ASIC前体、控制系统体系结构的ASIC化演进

8 结语

正文:

0 引言

FPGA与CPU、GPU、DSP、ASIC并列,是的一种处理数字量的、执行通信/控制/运算任务的核心芯片,具备独特的优势与劣势。

为了促进深入应用FPGA的技术理念在各前沿行业被广泛接受,笔者撰写了本文,用尽可能短的篇幅,向不熟悉FPGA的专家、决策者介绍FPGA的体系结构。

1 什么是体系结构

体系结构的最标准定义来自计算机设计领域的经典书籍《计算机体系结构 量化研究方法》(作者:John L. Hennessy,David A. Patterson),笔者看的是第五版,相关英文原文是:

Genuine Computer Architecture: Designing the Organization and Hardware to Meet Goals and Functional Requirements.

翻译成中文是:

真正的计算机体系结构:为实现所要求的目标、功能而针对组织及硬件进行的设计。

笔者基于对这本书中部分内容的有限理解,基于多年FPGA应用研发经验,对上述定义进行了引申、具象化,将其推广到一切控制模块,定义体系结构为:

为实现应用场景所要求的的目标(=功能+性能),设计者对一定数量、结构的硬件资源进行组织,使其以某种模式(至少涉及各个硬件资源单元之间的空间位置关系、信号连接关系、动作逻辑关系、动作时序关系、对供电/控温/控湿/EMC/支撑等基础设施的共用关系)协同工作,上述硬件资源的物理结构以及相关的组织方式、协同工作模式的具体形式,就是为实现上述目标而设计的体系结构。

[注:笔者不知道是否有人公开过类似的、对体系结构一词的引申定义,若有,则雷同部分的原创资格属于这些定义的创作者。]

2 FPGA的结构

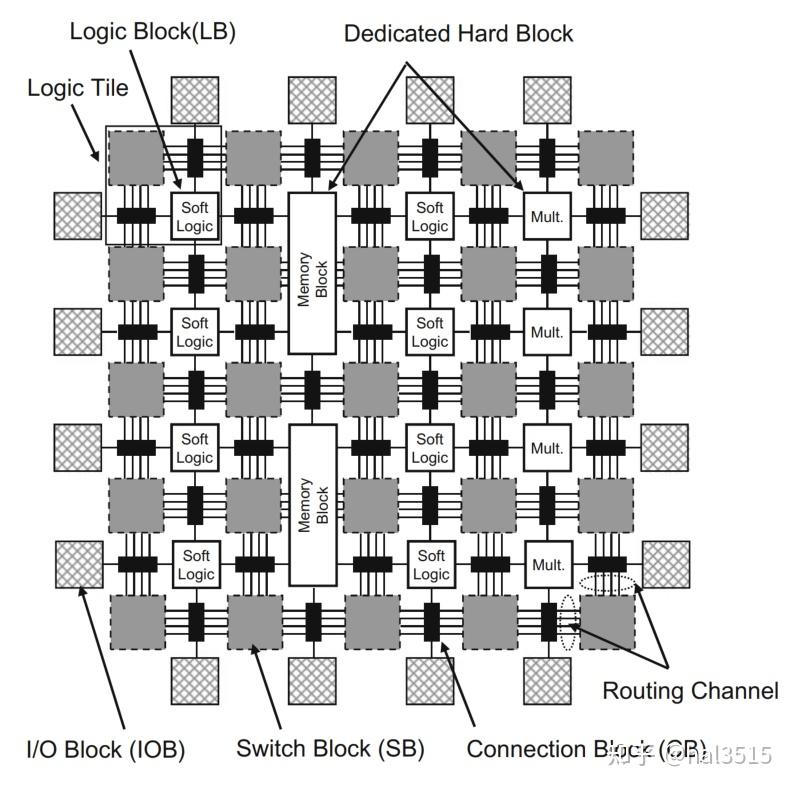

图1是FPGA(Field Programmable Gate Array,现场可编程门阵列)芯片的基本结构 (图片来源:深入理解 FPGA 的基础结构)。

图1 FPGA芯片的基本结构

其中,以分布式格局排列着大量功能可配置的硬件模块,包括(最多):

上百万个逻辑-时序-寄存器单元(Soft Logic -- 如图1所示,下同),各单元内含查找表即LUT,以实现灵活、复杂的逻辑功能,结合寄存器就能实现复杂的、直接面向应用的(而非层层映射的)时序逻辑功能;

上万个乘-加运算单元(Mult.)以实现复杂的运算功能;

两千多个存储器块(Memory Block),每个几kB,以实现数据的近场批量存储;

几百个用户输入输出模块(I/O Block),连同图中未画出的几十个带宽十几Gbps的高速串行通信接口,以实现与片外功能模块之间的互联 -- 这些功能模块包括但不限于:CPU/SoC,GPU,DSP,ASIC,DDRx-SDRAM,ADC,DAC,IPM,MEMS,图像sensor/ISP,激光/毫米波/超声波雷达,编码器,类似于六维力/力矩传感器的集成测量模块,类似于以太网PHY的通信芯片,光通信模块,射频通信模块;

以及在图中未画出的时钟处理模块、配置模块(用于配置大量可配置RAM位)、ADC、可能存在的多个硬核CPU单元/AI运算核心。

上述功能模块之间,在芯片内部的金属布线层,用分段的硬件连线 (Routing Channel)实现互联,硬件连线段之间通过硅层的可配置的互联模块(Connection Block)、切换模块(Switch Block)实现交叉互联,以提供各个功能模块之间的、极其灵活多变的可配置硬件连接(由配置模块对大量可配置RAM位写入0/1而实现)。

3 FPGA的体系结构

先说结论:

FPGA的体系结构 -- 时钟信号驱动的、用大量可灵活配置的底层硬件资源直接实现应用层算法的、分布式专用硬件算法模块的并行协作集合体。

在使用FPGA"为实现所要求的目标、功能而针对组织及硬件进行的设计(第1节的经典定义)"的过程中,FPGA应用研发工程师编写HDL(Hard Description Language,硬件描述语言)代码,以实现应用层算法为目标,定义FPGA芯片内部大量模块的工作模式、互联方式、时序配合方式,再将代码交给专用的开发软件平台,由后者将代码转换为大量可配置RAM位的取值(0/1)并且形成一个下载文件。

然后,FPGA工程师操作软件开发平台、经专用的FPGA配置线缆将这个下载文件传输到第1节所述的配置模块,由配置模块将下载文件中包含的大量0/1信息写入FPGA内部各个模块中的各个可配置RAM位,从而使这些模块在时钟信号(高端芯片主频400MHz左右)驱动下,以FPGA工程师在HDL代码中预设的模式工作(包括它们彼此之间的协同工作)、实现所需的应用层算法。

在上述配置后的FPGA芯片中,各个硬件模块各自占据物理上独立的一个硬件区块、由统一的时钟信号或互相关联的多个时钟信号驱动,模块之间并行运行(时序上可以有先后关系从而形成硬件流水线)、以可配置的专用硬件连线互联、以纳秒级精度互相协同。

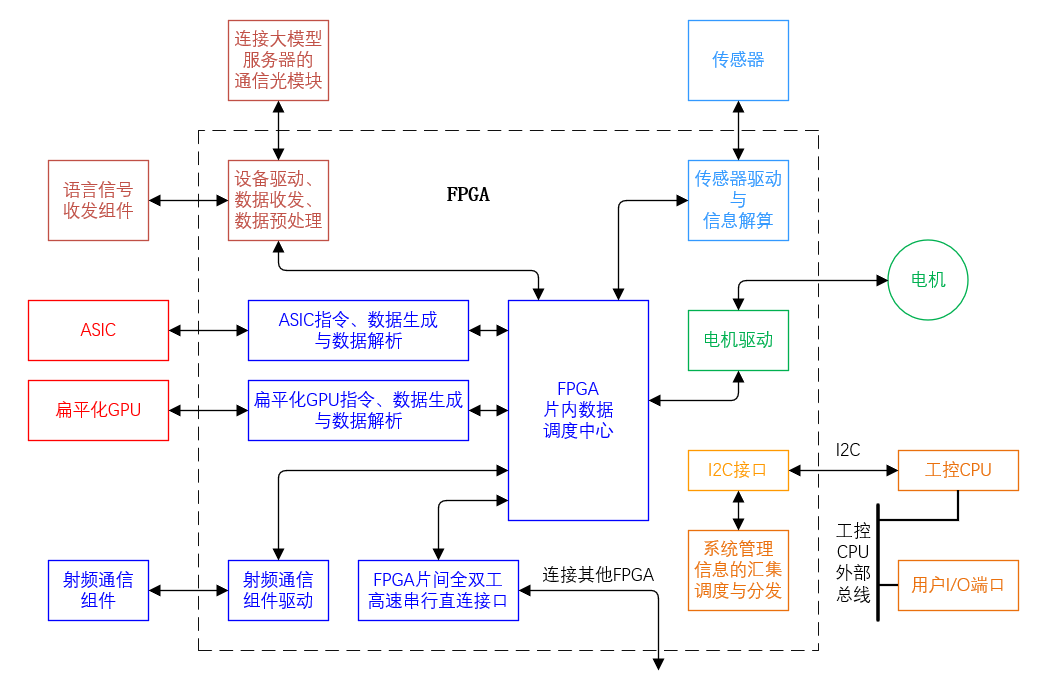

图2 基于ASIC+FPGA+扁平化GPU的人形机器人控制系统架构

图2 基于ASIC+FPGA+扁平化GPU的人形机器人控制系统架构

图2就是一个典型的案例 -- 来自笔者的知乎文章:人形机器人控制系统核心芯片从SoC到ASIC的进化路径(版本A)的图8。

4 FPGA的优势

从1.2节可以看出,在FPGA中,应用层算法的实现,是由大量分立的、可配置的底层硬件基础单元的定制化集合完成的,即,硬件底层实现的算法就是应用层算法 ,相比于CPU+软件体系结构的多个软件层:机器码、汇编码、操作系统、API、应用程序,FPGA的这个特征,使控制系统体系结构的功能映射/抽象的层级数量大幅度减少 ,并且以专用的硬件布线直连各个算法模块。

这种实现应用层算法的模式,不必再如CPU+软件体系结构那样时分复用硬件系统(硬件底层单元构成的CPU core)、读取指令、解析并执行指令、串行执行各个算法模块;实现算法的硬件模块可以直接访问物理上邻近的RAM块(如图1 所示),不必再访问多级存储器(寄存器、1-2-3级Cache、内存),因此节省了大量时钟周期。

同时,FPGA基于片内可配置硬件布线直连的低延迟时钟网络、低至2~3ns的时钟周期,为上述运算、互联、协同提供了精准的时间节拍。

并且,由于FPGA的算法抽象层次少、硬件动作直接就是应用层功能,其在执行相同算法的情况下,功耗远低于CPU、GPU。

5 FPGA的劣势

CPU+软件已经主导自动控制系统体系结构40年,即使是GPU,也要依靠CUDA这种复杂的附加抽象层级,使其体系结构兼容现有的软件生态。

FPGA体系结构与CPU体系结构的差别,显著大于GPU体系结构与CPU体系结构的差别。FPGA研发生态与软件研发生态的对接工作已经做了十几年,据笔者所知,目前还达不到CUDA的水平。

这就导致,多年来一直主导自动控制系统研发工作的、擅长软件的项目负责人/系统架构师,因为对FPGA体系结构不了解,导致对其不信任(黑箱决策风险)。

同时,FPGA应用研发由于需要在硬件底层进行设计、应对调试场景,其开发工具的抽象层次也比较较低,其研发时长显著大于CPU应用研发 ,并且相关人才的市场存量也比软件人才少得多,导致人力资源综合成本显著增加。

以上因素共同导致,即使不考虑GPU,在控制系统架构设计工作中,FPGA也被项目负责人视为万不得已(兼具多通道、大数据量、大运算量、算法复杂、强实时性)才考虑引入的技术。

并且,由于FPGA的功能实现依赖于对大量RAM位的配置,这就导致其运行主频通常低于400MHz,约为高端CPU/GPU主频的10~20%,从而对冲、稀释了FPGA在体系结构方面的优势。

另外,在多通道、大数据量、大运算量应用场景下,虽然FPGA的实时性已被反复证明显著优于CPU,但由于高端GPU执行简单重复算法时的并行算力大约是FPGA的几十上百倍,导致GPU在这类场景下 (尤其是在执行较复杂算法的FPGA优势场景下)的实时性性能很可能与FPGA有可比性,并且未曾做过实测对比验证。

6 FPGA的通用应用场景

上述底层硬件层面的并行性,使FPGA在执行同时要求多通道并行、大数据量、大运算量、算法不易简化的的数据采集-运算-控制反馈控制功能时,其实时性(低延迟量 & 低延迟抖动量,下同)性能显著优于CPU+软件体系结构。

相比于GPU,FPGA虽然在并行算力方面有显著的差距,但GPU适用于高并行度的简单算法,FPGA则由于其底层硬件的高度灵活性,能够在提供远较CPU丰富的强实时性并行算力的同时,实现远较GPU应用层算法复杂的强实时性算法,卡到了两者之间的生态位。

进而,图1中位于FPGA内部外圈的、经可配置硬件布线资源连接片内各个算法模块的大量I/O Block,确保了片内算法模块与片外功能模块(如第2节列举的)之间的大带宽、强实时性互联,确保了整个反馈控制系统的强实时性。

7 FPGA的特化应用场景:ASIC前体、控制系统体系结构的ASIC化演进

尤其重要的是,FPGA的体系结构与ASIC的体系结构非常相似,除了灵活性、中小批量投片成本的差距之外,后者具备前者一切体系结构特征、性能优势并且予以极致化。

二者在结构层面的表观区别在于,将FPGA中的可配置RAM位改成了固化的硬件,尤其是将FPGA中由位于硅层的可编程结构进行分段、衔接(见图1)的硬件连线,完全固化到了金属布线层;深层次区别则是,在底层模块级别进行了大量极致优化(例如将可配置的LUT改成固化的逻辑门阵列)。

由此导致,ASIC既具备FPGA体系结构的优势,又大幅度提高了运行主频、降低了功耗,由此导致:FPGA的经典应用场景是,验证ASIC逻辑原型设计的功能。

事实上,FPGA在江湖上还有一个外号:可编程ASIC。

关于将FPGA作为ASIC前体的应用场景,本文希望强调的是:

在控制系统体系结构技术演进的层面 ,在某些具备大批量市场应用前景的、对控制系统性能需求极高的前沿应用领域(例如人形机器人),由FPGA在体系结构层面"卡CPU、GPU的bug" (如第6节所述)的同时强调将其ASIC化之后的性能跃升前景(!!!!!) ,深入参与控制系统的原型设计,运用其结构及功能可以灵活配置的特征、绕开ASIC投片成本高的劣势,针对应用场景的反馈进行快速迭代,为最终以ASIC为核心实现这类领域核心产品的控制系统铺平道路。

笔者的知乎文章:人形机器人控制系统核心芯片从SoC到ASIC的进化路径(版本A),就是针对这个方向的一次探讨。

8 结语

FPGA相比于CPU、GPU,有其独特的性能优势,占据独特的生态位。

FPGA的劣势使其被擅长软件的广大项目负责人/系统架构师视为歧途。

至少在具有广阔应用前景的、对控制系统性能需求极高的前沿技术领域, 例如人形机器人,FPGA由于其"ASCI前体"的属性,理应被视作控制系统技术架构的核心备选项之一。