在指尖轻触手机屏幕的瞬间,一个微小的静电火花可能已悄然产生------其电压可能高达数千伏,足以击穿现代芯片中仅1-2纳米厚的栅氧化层。随着半导体工艺迈入7nm、5nm甚至2nm时代,晶体管愈发精密,后端金属(BEOL)层数增至12层以上,器件栅氧化层厚度持续缩减,芯片对静电放电(ESD)的耐受度大幅下降。这一"隐形杀手"正成为芯片可靠性的最大威胁之一,可能导致器件即时损坏或电路隐性损伤,显著降低设备整体性能与使用寿命。

传统设计依赖工程师经验,在I/O端口手动添加二极管或GGNMOS等保护器件。但在数十亿晶体管交织的复杂SoC中,ESD电流可能绕过预设路径,通过电源网络、金属互连甚至衬底耦合,找到意想不到的"捷径"直击核心电路。如何系统性地识别并封堵这些风险?答案是:PERC(Programmable Electrical Rules Checking)。

PERC:不止于规则检查,更是可靠性审计官

PERC并非普通版图验证工具的简单延伸,它融合了电路拓扑、物理布局与寄生参数提取能力,能对全芯片进行路径级ESD电流仿真,精准评估每一条潜在泄放通路的可靠性。作为Calibre验证工具的子工具,PERC基于Tcl语言开发,具备可编程特性,支持用户自定义规则文件,这使其比其他方法更适用于ESD保护布局的检测。

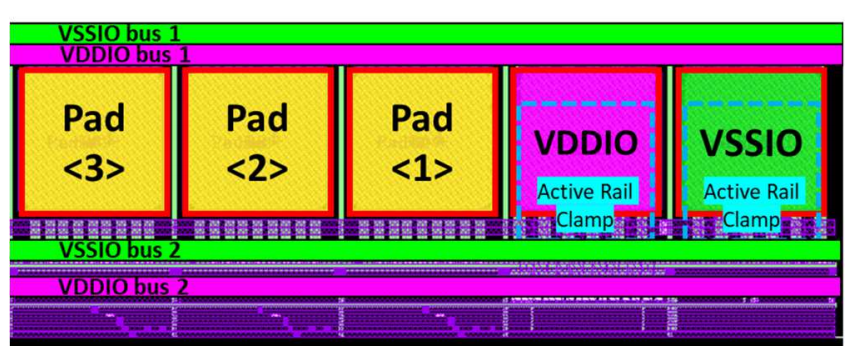

如图1所示,在一个典型的多电源域SoC中,GPIO焊盘通过二极管连接至VDDIO/VSSIO,而轨钳(Rail Clamp)则负责将ESD电流导向主电源/地网格。轨钳作为关键保护器件,需与各电源域形成有效通路,通过分布式设计可降低单点过热风险。然而,若焊盘环布线电阻过高,或不同接地域之间缺乏反向并联二极管(APD),ESD电流便可能滞留于局部区域,引发热失效。PERC的核心能力在于:它不仅能"看见"设计的保护结构,更能通过逻辑驱动布局(LDL)技术,验证这些结构在实际工况下是否真正有效。

图1:全芯片ESD保护网络示意图 (来源:《通过PERC编程实现有效的ESD设计》) 注:不同颜色代表不同电源/地网络

小节点下的三大挑战与PERC应对之道

挑战一:寄生电阻主导防护效果

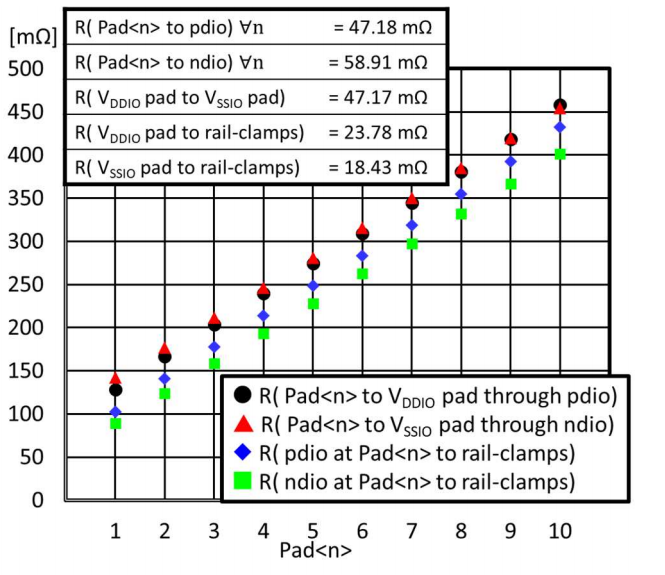

在先进工艺中,BEOL的片电阻和通孔阻抗显著影响ESD性能。随着芯片尺寸不断增大,环绕整个芯片的电源线和地线长度持续增加,寄生电阻也随之增大,这些寄生电阻会降低ESD电流通过保护电路的分流能力。手工计算寄生电阻容易出错,布局后仿真又过于耗时,而PERC通过LDL技术可自动提取从I/O焊盘到轨钳的点对点(P2P)电阻,并与设定阈值比对。举例,在某40nm RF SoC中,通过PERC P2P分析发现某段总线电阻超标,优化后使IO到VDDIO的路径电阻降低20%,且未增加焊盘到pdio的布线电阻,同时确保所有ESD器件的电流密度(Current Density,CD)违规率为零。

挑战二:保护拓扑高度多样化

不同接口(如USB、MIPI、HDMI)对漏电、耐压要求各异,导致ESD方案千差万别:有的用双二极管,有的用堆叠NFET,还有的采用分布式轨钳。二极管保护装置的串联数量、NFET的堆叠数量需根据接口特性优化,若为每种结构编写独立规则,维护成本将不可控。对此,有团队在研究成果中提出参数化+递归编程策略:将所有拓扑抽象为"起点→ESD器件→终点"的统一模式,通过Tcl脚本动态适配不同器件类型与连接方式。ESD工程师只需维护一个参数化程序,新增器件类型或调整检测需求时,仅需补充参数条目即可,这不仅提升规则复用性,更确保签核标准的统一性。

挑战三:全芯片集成后的"最后一公里"风险

单个IP模块通过ESD验证,并不意味着整颗芯片安全。ESD保护网络并非局限于单一IP模块,只有当芯片完全组装后才算完整。例如,保护GPIO的双二极管可能位于同一IO单元内,但必须在焊盘环的其他位置配置轨钳才能形成有效防护;某ADC芯片虽在单元级达标,但因顶层布线存在高阻节点,导致CDM测试失败。PERC支持全芯片级CD/P2P分析,可模拟封装级连接(如引线框架的下键合环),真实还原ESD电流分布。通过对不同焊盘组合的电阻扫描,能快速定位系统级布线缺陷等薄弱环节,指导布局迭代优化。

图2:GPIO焊盘P2P电阻随位置变化曲线 (来源:《通过PERC编程实现有效的ESD设计》) 注:异常高阻点揭示了系统级布线缺陷

效率革命:从"指数爆炸"到"线性增长"

早期PERC规则常因重复遍历器件而导致运行时间激增。相关文献数据显示,对含复杂多指5二极管串的RF IP模块,朴素实现的PERC规则耗时长达91分钟,而采用动态规划+缓存机制的优化版本仅需3秒,文件体积也大幅缩减。

其关键在于引入"Label"和"Cache"两大数据结构:

-

Label:记录已访问的ESD器件,避免重复探索,确保每个器件仅被分析一次;

-

Cache:缓存网络下游的ESD器件集合,实现结果复用,无需重复探索相同下游连接。

通过这一优化,算法复杂度从指数级降至线性级,逼近理论最优。这使得PERC不仅能用于流片前签核,更能作为迭代设计工具,在开发早期快速反馈优化建议。值得注意的是,Calibre PERC支持多线程计算,虽拓扑搜索部分的加速效果无法与核心数呈完全线性比例,但结合优化后的规则文件,仍能显著提升全流程效率。

结语:可靠性,是先进制程的底线

在摩尔定律放缓的今天,芯片竞争已从性能转向质量与可靠性。PERC技术正是这一转型的关键支撑,它不仅是流片前的最后一道防线,更是贯穿IP开发、Pad Ring设计到SoC集成的全流程保障。从ESD器件识别(通过GDS标记层"ESD_DEVICE"实现)到寄生参数提取,从单路径电阻检测到全芯片电流分布仿真,PERC通过参数化编程、智能算法优化与全局视角分析,构建了完整的ESD可靠性验证体系。

PERC-LDL分析本质为静态分析,虽无法模拟有源器件的导通电压和CDM事件的瞬态电感效应,但通过导入100纳秒时间线参数(TLP)数据和短脉冲VFTLP测量的导通电阻值,可有效评估HBM和CDM两类ESD风险,核心目标是快速量化并定位内部器件的潜在风险。

高效的PERC规则 = 参数化设计 × 智能算法 × 全局视角。唯有如此,才能为每一颗纳米级芯片,织就一件真正可靠的"防弹衣",护航先进制程芯片在复杂应用场景中的稳定运行。