本博文主要交流设计思路,在本博客已给出相关博文约150篇,希望对初学者有用。注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。

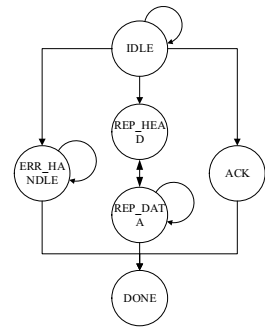

(b)应答状态机

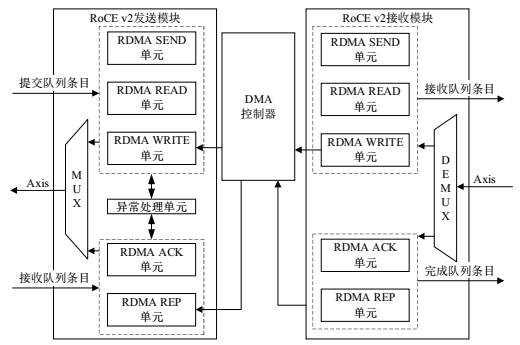

当 RoCE v2 发送模块检测到接收队列非空时,则从接收队列中提取一个接收队列条目,根据不同的接收队列条目状态和不同的操作类型进入不同的数据包生成流程,这一过程由应答状态机实现,应答状态机的状态转移图如图 1所示,对于各个状态的详细说明如下:

图1 应答状态机状态转移图

IDLE:空闲状态,系统复位后请求状态机将进入 IDLE 状态。当检测到接收队列非空时,从接收队列中读取一个接收队列条目,而后解析接收队列条目是否异常。如发现异常,则跳转至 ERR_HANDLE 状态。如果接收队列条目状态正常,则解析接受请求类型,对于 SEND、WRITE 指令跳转至 ACK 状态;对于 READ 指令,跳转至REP_HEAD 状态。如果接收队列为空,则保持 IDLE 状态。

ERR_HANDLE:异常处理状态。在该状态下将异常接收队列条目提交到异常处理单元,进行异常处理,等待异常处理结束后跳转至 DONE 状态。

ACK:无数据应答状态。此状态下将根据接收队列条目中的远程主机队列 ID 和操作类型组装 ACK 应答包,并发送到远程主机。发送完毕后跳转到 DONE 状态。

REP_HEAD:有数据应答头发送状态。在此状态下将根据接收队列条目中的远程主机队列 ID 和操作类型组装 REP 应答包。同时将请求数据长度与以太网单数据帧最大长度进行比较。如果请求长度超过单数据帧最大程度,则 REP 包头部中的操作类型被置为 FIRST/ MIDDLE/LAST;反之 REP 包头部中的操作类型被置 ONLY。同时将请求数据起始地址、请求数据长度通知给 DMA 控制器,而后跳转至 REP_DATA 状态。

REP_DATA:有数据应答数据发送状态。在该状态下将 DMA 控制器返回的数据组装为 REP 包,直到达到以太网单数据帧最大长度或用户请求长度。而后对数据长度进行判断。如果数据已发送完毕,则跳转至 DONE 状态;如果仍有数据未发送完毕,则跳转回 REP_HEAD 状态,重复 REP 数据包发送流程。若请求数据超时,则返回 IDLE 状态并返回异常完成条目。

DONE:应答完成状态。该状态下将发送寄存器中剩余的最后一帧数据并生成指令完成信号。在一个时钟周期后回到 IDLE 状态。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望