一、ARM基本知识

- 嵌入式:以应用为中心,以计算机技术为基础,软硬件可裁剪的专用计算机系统。

- 计算机系统组成:硬件系统,软件系统(应用软件、系统软件)。

- 计算机硬件组成:运算器、控制器、存储器、输入设备、输出设备。

- CPU :中央处理器,数据运算、指令处理。

- GPU:图像处理单元,图形数据处理、图像渲染。

- FPU:浮点数单元,浮点数运算与处理。

- MPU:微处理器,仅含 CPU 模块,需外接存储、外设等功能模块。

- MCU:微控制器,集成 CPU、RAM、ROM、IO、UART、定时器、中断系统,实现简单控制。

- SOC:片上系统,整合多个功能芯片(如 CPU、GPU、NPU、存储控制器等)到单一芯片。

- DSP:数字信号处理器,是为了高强度数学运算而设计的一种专门芯片。

二、ARM内核

1.ARM发展与分类

早期经典内核ARM1 ~ ARM11,对应指令集版本 ARMv1 ~ ARMv4。

现代 Cortex 系列内核:分为三大产品线

- Cortex-A:面向高性能应用(如手机、平板),带内存保护单元(MPU),支持复杂操作系统。

- Cortex-R:面向实时控制场景(如汽车电子、工业控制),强调高可靠性和低延迟。

- Cortex-M:面向微控制器(MCU),主打低功耗、低成本,是物联网和嵌入式设备的主流选择。

2.指令集

CISC(Complex Instruction Set Computer):复杂指令集

RISC(Reduced Instruction Set Computer): 精简指令集

处理器指令集架构:x86(CISC),ARM(RISC),MIPS(RISC),RISC-V(RISC)

3.核心器件

| 器件名称 | 作用说明 |

|---|---|

| 通用寄存器组(R0~R15) | 存储临时计算数据和指令执行上下文,是 CPU 高速读写的 "临时仓库"。 - R13(SP)是栈指针,管理函数调用的栈空间;R14(LR)是链接寄存器,保存函数返回地址;R15(PC)是程序计数器,指向当前执行的指令地址。 |

| 状态寄存器(CPSR/SPSR) | - CPSR(当前程序状态寄存器)记录 CPU 当前的运行状态(如中断屏蔽标志、运算结果标志)。 - SPSR(保存程序状态寄存器)用于在异常发生时保存 CPSR 的值,异常退出后恢复现场。 |

| 算术逻辑单元(ALU) | 执行算术运算(加减乘除)和逻辑运算(与、或、非、移位),是 CPU 的 "计算引擎"。 |

| Cache(i-Cache / d-Cache) | - i-Cache(指令缓存)存储近期频繁执行的指令,减少从内存取指令的延迟。 - d-Cache(数据缓存)存储频繁访问的数据,提升数据读写速度。 |

| 内存管理单元(MMU) | 仅在 Cortex-A 等高端内核中存在,负责虚拟地址到物理地址的映射,支持内存分页和权限管理,是多任务操作系统的基础。 |

三、ARM处理器工作模式

| 模式名称 | 类型 | 触发条件 | 核心作用 |

|---|---|---|---|

| User(用户模式) | 非特权模式 | 正常程序执行时 | 大部分应用程序的运行模式,权限受限,防止错误代码破坏系统。 |

| FIQ(快速中断模式) | 特权模式 | 高优先级中断请求 | 处理紧急事件(如高速数据传输),拥有更多私有寄存器,中断延迟最低。 |

| IRQ(普通中断模式) | 特权模式 | 普通中断请求 | 处理常规外设中断(如键盘、定时器),是最常用的中断处理模式。 |

| Supervisor(管理模式) | 特权模式 | 系统复位或执行软中断指令 | 操作系统内核的运行模式,负责系统初始化、内存管理和任务调度。 |

| Abort(终止模式) | 特权模式 | 内存访问异常(如地址错误、权限不足) | 处理内存故障,保护系统避免非法内存操作导致崩溃。 |

| Undef(未定义模式) | 特权模式 | 执行未定义指令或协处理器指令 | 处理指令错误,可用于软件仿真协处理器功能。 |

| System(系统模式) | 特权模式 | 由操作系统切换进入 | 使用与用户模式完全相同的寄存器集,但拥有特权权限,用于执行需要高权限的系统任务。 |

| Monitor(监控模式) | Cortex-A 特有特权模式 | 安全相关事件触发 | 实现安全监控和隔离(如 TrustZone 技术),负责在安全与非安全世界之间切换。 |

四、ARM寄存器

ARM 有37个32-Bits长的寄存器

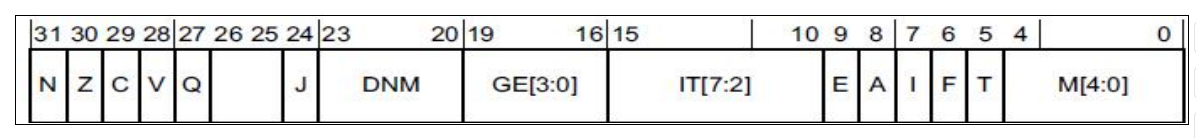

程序状态寄存器

条件位:

- N = Negative result from ALU

- Z = Zero result from ALU

- C = ALU operation Carried out or borrow

- V = ALU operation oVerflowed

E位:大小端控制位

A位:A=1 禁止不精确的数据异常

中断禁止位:

- I = 1: 禁止 IRQ.

- F = 1: 禁止 FIQ

Mode位:

处理器模式位

- 10000 User mode;

- 10001 FIQ mode; 10011 SVC mode;

- 10111 Abort mode; 11011 Undfined mode; 11111 System;

- 10110 Monitor mode; 10010 IRQ

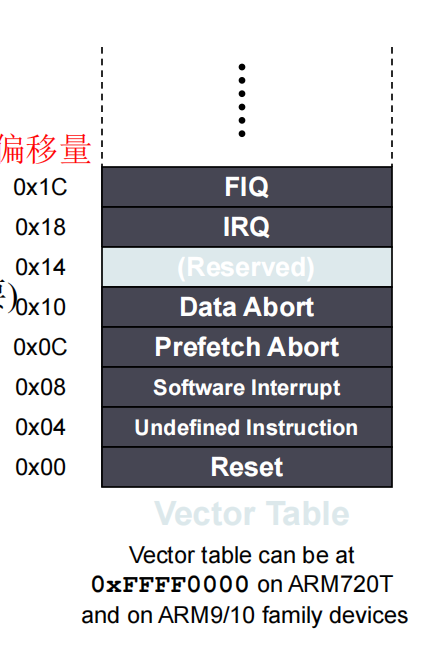

五、异常处理

当异常产生时, ARM core:

- 当前程序状态寄存器 CPSR 的内容,复制到对应异常模式的保存状态寄存器 SPSR_<mode>

- 设置适当的 CPSR 位:

- 改变处理器状态进入 ARM 态

- 改变处理器模式进入相应的异常模式

- 设置中断禁止位屏蔽同级或更低优先级的中断 (如果需要)

- 保存返回地址到 LR_<mode>

- 设置 PC 为相应的异常向量

返回时, 异常处理需要:

- 从 SPSR_<mode>恢复CPSR,将处理器状态、中断使能位等恢复到异常发生前的状态。

- 从LR_<mode>恢复PC的值,跳转到异常发生前的代码继续执行。