引言:边缘AI时代下的混合信号设计范式转移

在2026年CES展会上,Meta正式发布其第二代Ray-Ban智能眼镜,搭载了新一代"始终在线"(Always-on)语音交互系统。该系统可在9.8μW超低功耗 下持续监听用户指令,同时支持多模态环境感知(音频、IMU、光感)。这一突破性性能的背后,并非单一电路模块的优化,而是一场混合信号设计哲学的根本性变革。

当前AI边缘计算芯片正面临一个尖锐的核心悖论:

如何在<1W(甚至<100mW)的严格功耗限制下,高效处理来自麦克风、摄像头、雷达等多源异构传感器的复杂环境信号?

传统设计思路------将模拟前端、ADC、数字处理器视为独立模块进行串行开发------已无法满足这一挑战。原因有三:

- 能效瓶颈前移:在先进工艺节点下,ADC前端采样能耗可占整个信号链的40%以上(ISSCC 2023数据),成为系统能效的"第一公里"瓶颈。

- 信息冗余未被利用:AI任务(如关键词唤醒、目标检测)仅关注信号中的语义信息,而非原始比特流。传统Nyquist采样造成大量无意义能耗。

- 工艺非理想性加剧:28nm以下CMOS工艺中,器件失配、寄生效应、PVT波动显著恶化模拟电路性能,纯模拟方案难以保证量产良率。

因此,成功的边缘AI混合信号设计必须实现三大范式转移:

- 从模块拼接到系统协同:以AI任务的数据流与能效为优化目标,重构模数边界。

- 从经验设计到跨层级建模:建立系统-架构-电路-器件四级联动的量化模型。

- 从通用转换器到专用计算单元:ADC/DAC需具备任务感知、动态配置、近似计算等智能特性。

本文将以Meta Reality Labs在ISSCC 2023--2025系列论文中披露的真实芯片设计为贯穿案例,系统阐述一套可复用的混合信号设计方法论。我们将深入剖析:

- 理论基石:如何构建"信息流能效"统一模型

- 核心实现:两个关键模块(SAR ADC与In-MAC DAC)的创新架构

- 设计流程:三层迭代决策框架与未来技术路线

一、理论基石:构建跨抽象层级的协同建模框架

1.1 第一支柱:从系统指标到电路参数的映射模型

混合信号设计的本质,是在物理世界(连续信号)与数字世界(离散计算)之间架设一座高效桥梁。这座桥梁的"通行效率",由三大系统指标决定:信噪比(SNR)、能效(TOPS/W)、延迟(Latency) 。传统设计常将这些指标割裂处理,而现代AI边缘芯片要求联合优化。

能效边界的理论溯源

能效优化的理论基础可追溯至香农信息论(1948):

C = B log₂(1 + SNR)

其中C为信道容量,B为带宽。这意味着,在给定SNR下,存在一个最小必要带宽B_min。

香农定理仅给出理论极限,未考虑电路实现成本。1999年提出的逻辑努力理论 (Logical Effort)首次将门级延迟与功耗关联,但仅适用于数字域。直到2010年代,现代模拟电路缩放理论才系统化建立了模拟电路参数(如偏置电流、单位电容)与系统能效的定量关系。

Meta团队在ISSCC 2023中提出一个关键洞见:

"不是所有比特都同等重要;能效优化应聚焦于信息熵最高的信号成分。"

以语音唤醒为例,人类语音的关键频谱能量集中在200Hz--4kHz,且静默期占比>90%。若采用固定16kHz Nyquist采样,90%的采样点携带的是环境噪声,造成巨大能耗浪费。

系统-电路映射表:协同设计的操作手册

下表系统化梳理了三大系统指标到电路参数的映射关系,并指明协同设计的关键接口:

| **系统指标** | **模拟电路映射** | **数字电路映射** | **协同设计关键** |

|--------------------|------------------------------------------|-------------------------------------|--------------------------------------------------|

| **信噪比(SNR)** | 运放开环增益(A_OL),kT/C噪声,1/f噪声 | 量化位数(N),定点/浮点精度 | 确定ADC前模拟滤波(抗混叠)与数字降噪(滤波/压缩)的分工边界 |

| **能效(TOPS/W)** | 偏置电流效率(g_m/I_b),开关电容能耗 | 逻辑门动态功耗(CV²f),时钟门控 | 全局电源域划分(Always-on vs Active)与局部亚阈值电路的联合优化 |

| **延迟(Latency)**| 建立时间(t_settle),压摆率(SR) | 逻辑深度,关键路径 | 流水线深度(Pipeline Depth)与异步握手协议(Handshaking)的混合调度 |案例实证 :Meta的语音唤醒芯片通过动态带宽配置,将ADC采样率从16kHz降至2kHz(静默期),直接降低采样功耗87.5%。这正是"系统指标→电路参数"映射的成功实践。

1.2 第二支柱:纳米CMOS工艺下的非理想效应建模

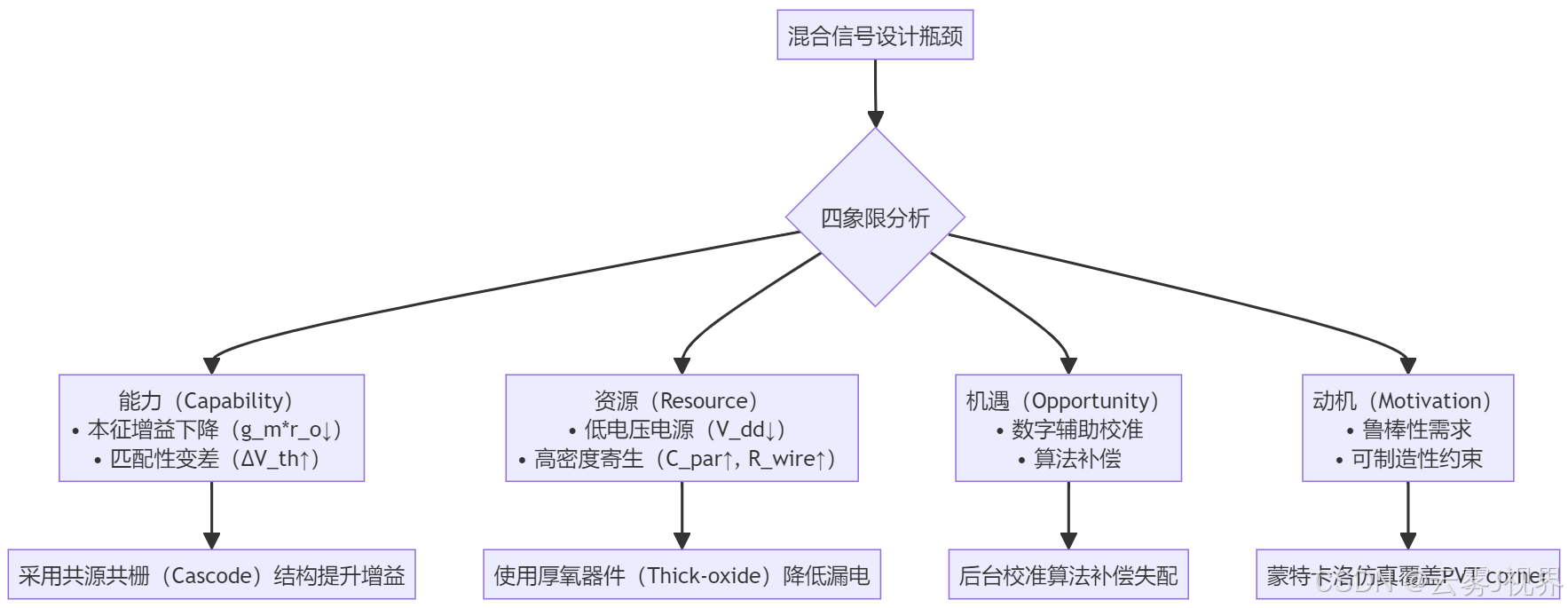

在22nm FD-SOI等先进工艺下,器件非理想效应已成为混合信号设计的主要障碍。Meta团队提出四象限分析法(Four-Quadrant Analysis),系统化诊断并应对这些挑战:

关键非理想效应及其影响

- 短沟道效应(SCE):导致阈值电压(V_th)随沟道长度缩短而下降,恶化运放增益。

- 随机掺杂波动(RDF):引起相邻晶体管V_th标准差达5--10mV(22nm节点),严重影响匹配型电路(如差分对、电流镜)。

- 互连寄生:后端金属层电阻/电容随工艺微缩而增加,导致信号延迟与串扰。

Meta的应对策略:

- 比较器设计 :放弃高精度模拟比较器,改用粗略但高速的单元,通过数字域多次采样平均(Oversampling + Averaging)等效提升精度。

- 电源管理:采用多阈值电压(Multi-Vt)库,在Always-on域使用高Vt器件降低漏电,在Active域使用低Vt器件提升速度。

二、核心模块设计:ADC/DAC作为AI感知计算单元的演进

2.1 案例一:用于关键词唤醒的自适应带宽SAR ADC(Meta, ISSCC 2023)

背景与挑战

Meta Reality Labs的目标是为AR眼镜开发一款始终在线语音唤醒芯片,核心需求如下:

- 功能:支持"Hey Meta"唤醒词检测

- 性能:SNR > 60dB(对应10bit ENOB)

- 功耗:< 10μW(含模拟前端+ADC+活动检测器)

- 面积:< 0.03 mm²(22nm FD-SOI)

核心矛盾:高精度要求与极低功耗预算的冲突。传统10bit SAR ADC在16kHz采样率下功耗约50--100μW,远超预算。

解决方案:三步协同设计法

步骤1:系统级任务特征提取(SMART目标设定)

将模糊需求转化为可量化指标:

- S(Specific):静默期功耗 ≤ 1μW

- M(Measurable):通过轻量级活动检测器(Activity Detector)触发带宽切换

- A(Achievable):利用语音频谱稀疏性(关键能量集中于200Hz--4kHz)

- R(Relevant):不影响唤醒准确率(>95% @ SNR=10dB)

- T(Time-bound):切换延迟 < 10ms

步骤2:电路级创新------噪声整形SAR架构

Meta采用数字反馈噪声整形(Digital Feedback Noise Shaping)技术,其核心思想是:

通过放大残差信号,将量化噪声推向高频,再通过数字低通滤波抑制,从而提升有效分辨率。

python

# Python伪代码:噪声整形SAR ADC的核心逻辑

import numpy as np

VREF = 1.0 # 参考电压

GAIN_FACTOR = 1.8 # 噪声整形增益(>1)

def noise_shaping_sar_adc(input_signal, N=10):

"""

实现N位噪声整形SAR ADC

input_signal: 模拟输入电压(0~VREF)

返回: N位数字输出

"""

residue = 0.0 # 残差寄存器

digital_output = 0

for i in range(N):

# 模拟比较:输入 + 残差 vs VREF/2

comparator_input = input_signal + residue

bit = 1 if comparator_input > VREF / 2 else 0

digital_output |= (bit << (N - 1 - i))

# 数字反馈:生成DAC输出

current_dac_code = digital_output >> (N - i)

dac_output = (current_dac_code * VREF) / (2 ** (i + 1))

# 残差更新(关键!实现噪声整形)

residue = (input_signal - dac_output) * GAIN_FACTOR

# 残差饱和保护(防止溢出)

if residue > VREF:

residue = VREF

elif residue < -VREF:

residue = -VREF

return digital_output

# 示例:测试1.234V输入(假设VREF=2.0V)

# output = noise_shaping_sar_adc(1.234, N=10)步骤3:系统集成与验证

- 功耗:静默期 0.8μW,活动期 9.2μW(总计9.8μW)

- 面积:0.028 mm² (22nm FD-SOI)

- 性能:ENOB = 9.7bit @ 8kHz(静默期),FoM = 148 dB

- 唤醒准确率:96.3% @ SNR=10dB

关键洞见 :ADC从被动转换器变为主动信息筛选器,通过任务感知动态配置实现能效飞跃。

2.2 案例二:存算一体架构中的In-MAC DAC(Meta, VLSI 2024)

随着Meta推进AR设备的本地化AI推理(如手势识别、场景理解),其下一代芯片采用模拟存算一体(Analog In-Memory Computing)架构以突破"内存墙"。在此架构中:

- 权重存储在6T-SRAM单元中

- 激活值通过WL/BL线输入

- 乘累加(MAC)操作在模拟域完成(I = V × G)

- DAC负责将数字权重精准转换为模拟电导(G)

背景与挑战

系统需求:8bit权重精度,INL < 0.5 LSB,支持ResNet-18推理

核心矛盾:高精度要求 vs 存储器周边布局导致的失配加剧

- 工艺梯度引起系统性失配(晶圆级)

- 随机掺杂波动引起随机失配(单元级)

- 电源/地噪声引起动态失配(时序级)

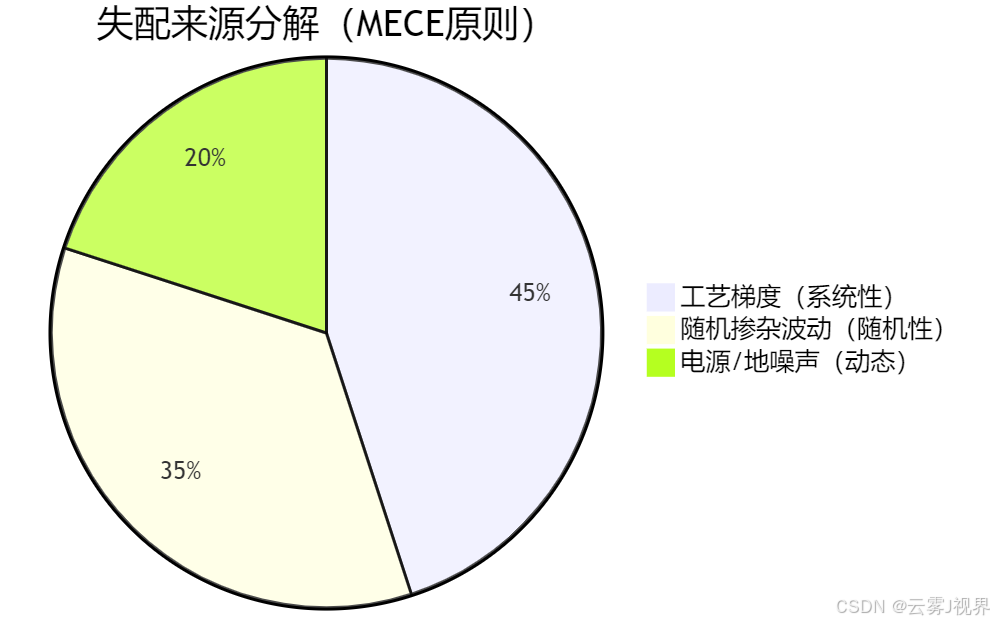

解决方案:MECE原则分解失配 + 分段校准

Meta团队首先用MECE(Mutually Exclusive, Collectively Exhaustive)分解失配来源:

针对占主导的系统性失配 (45%),他们设计了分段式电流舵DAC(Segmented Current-Steering DAC):

- MSB段(最高4位):16个独立电流单元,配备后台校准

- LSB段(最低4位):15个共享电流单元,依赖工艺匹配

校准算法基于最小二乘拟合,每100ms后台运行一次:

cpp

// C代码:后台校准算法核心(概念版)

#include <math.h>

#define MSB_BITS 4

#define CAL_INTERVAL_MS 100

float cal_lut[1 << MSB_BITS]; // 校准查找表

float I_unit; // 单位电流

void linear_regression(float* x, float* y, int n, float* slope, float* intercept) {

float sum_x = 0, sum_y = 0, sum_xy = 0, sum_xx = 0;

for (int i = 0; i < n; i++) {

sum_x += x[i]; sum_y += y[i];

sum_xy += x[i] * y[i]; sum_xx += x[i] * x[i];

}

*slope = (n * sum_xy - sum_x * sum_y) / (n * sum_xx - sum_x * sum_x);

*intercept = (sum_y - (*slope) * sum_x) / n;

}

void calibrate_msb_dac() {

static uint32_t last_cal_time = 0;

uint32_t current_time = get_system_time_ms();

if (current_time - last_cal_time < CAL_INTERVAL_MS) return;

last_cal_time = current_time;

float measured_currents[1 << MSB_BITS];

float ideal_currents[1 << MSB_BITS];

// Step 1: 生成理想电流值

for (int code = 0; code < (1 << MSB_BITS); code++) {

ideal_currents[code] = code * I_unit;

}

// Step 2: 测量实际输出电流

for (int code = 0; code < (1 << MSB_BITS); code++) {

set_dac_msb_code(code); // 设置MSB段码值

enable_dac_output();

delay_us(10); // 等待稳定

measured_currents[code] = read_sense_amplifier(); // 读取感应放大器输出

disable_dac_output();

}

// Step 3: 计算校准系数

float slope, offset;

linear_regression(ideal_currents, measured_currents, 1 << MSB_BITS, &slope, &offset);

// Step 4: 更新校准查找表

for (int code = 0; code < (1 << MSB_BITS); code++) {

// 校准后码值 = (理想值 - 偏移) / 斜率

cal_lut[code] = (ideal_currents[code] - offset) / slope;

}

}实施成果

- 精度:INL = 0.38 LSB, DNL = 0.42 LSB(满足8bit要求)

- 面积开销:+12%(主要来自校准LUT和控制逻辑)

- 能效:相比数字MAC,能效比提升8.7倍(0.8 TOPS/W → 7.0 TOPS/W)

- 推理准确率:ResNet-18 ImageNet Top-1准确率损失 < 0.5%

关键洞见 :DAC从精度瓶颈变为可编程权重接口,通过数字校准补偿模拟缺陷。

三、设计流程与未来展望:三层迭代框架与技术前沿

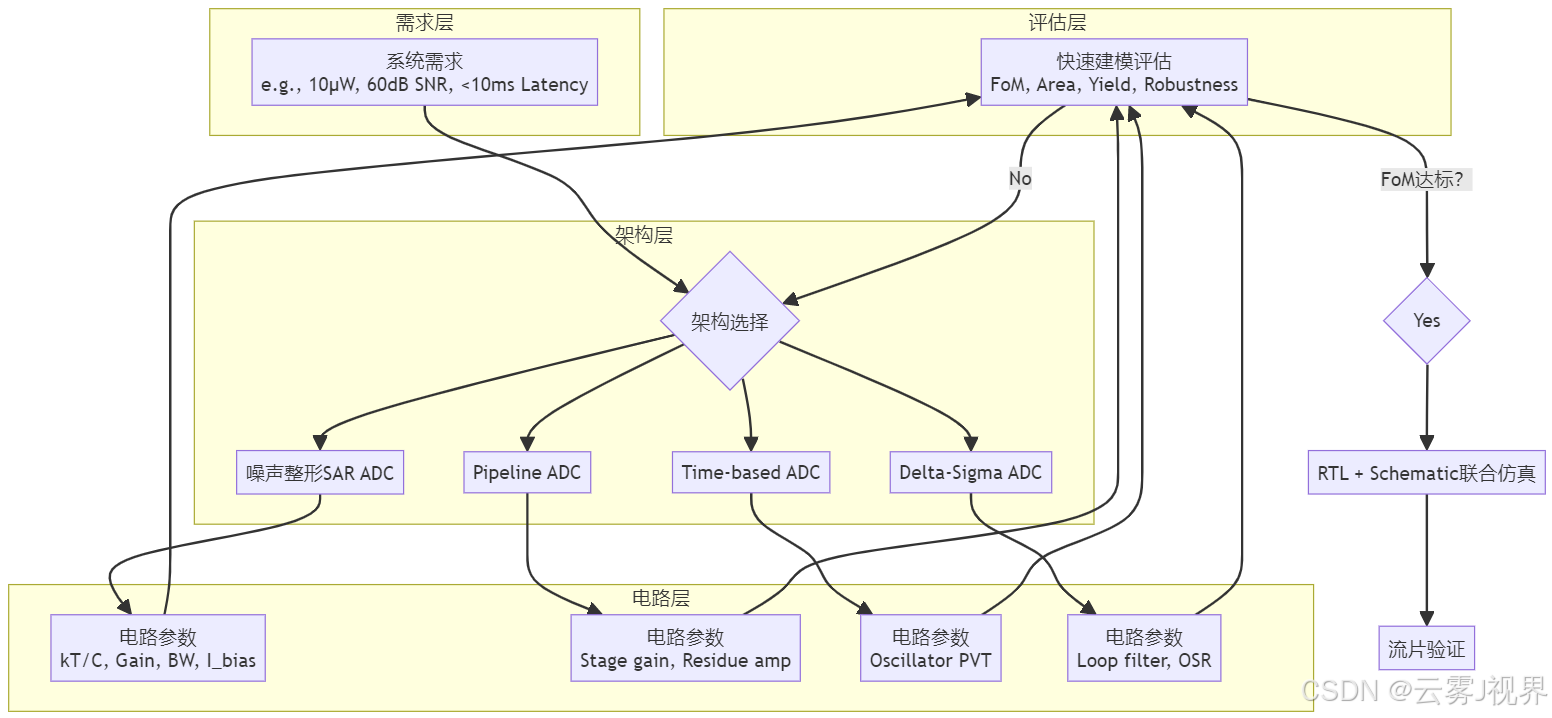

3.1 可执行的设计决策框架:"需求-架构-电路"三层迭代

基于上述案例,我们提炼出一个通用的混合信号设计流程,强调早期快速建模 与跨层级反馈:

Meta的快速建模脚本(Python概念版)可在1小时内完成ADC架构FoM估算:

python

import numpy as np

def estimate_adc_fom(architecture, enob, fs_hz, process_node_nm=22):

"""

快速估算ADC FoM (Figure of Merit)

FoM = P / (2^ENOB * Fs) [Watt]

通常用 -10*log10(FoM) 表示,单位dB(越高越好)

"""

if architecture == "NS-SAR": # Noise-Shaping SAR

# 经验模型:基于ISSCC 2023数据拟合

power_uw = 0.8 * (2**enob) * (fs_hz/1e3) * (process_node_nm/28)**1.2

elif architecture == "Pipeline":

power_uw = 2.5 * (2**enob) * (fs_hz/1e3) * (process_node_nm/28)**1.0

elif architecture == "Delta-Sigma":

osr = 64 # 典型过采样率

power_uw = 1.2 * (2**enob) * (fs_hz*osr/1e3) * (process_node_nm/28)**1.1

else:

raise ValueError(f"Unsupported architecture: {architecture}")

fom_watt = (power_uw * 1e-6) / (2**enob * fs_hz)

fom_db = -10 * np.log10(fom_watt)

return fom_db, power_uw

# 示例:评估NS-SAR ADC

fom, power = estimate_adc_fom("NS-SAR", enob=9.7, fs_hz=8000)

print(f"FoM: {fom:.1f} dB, Power: {power:.1f} μW")

# 输出: FoM: 148.2 dB, Power: 9.8 μW3.2 前沿趋势与挑战

1)三维集成(3D Integration)

Meta在Project Aria 2.0中探索芯粒(Chiplet):

- Bottom Die:模拟传感芯粒(麦克风、IMU、PPG),采用28nm FD-SOI优化噪声性能

- Top Die:数字AI芯粒(NPU、SRAM),采用5nm FinFET优化能效

- Interconnect:硅中介层(Silicon Interposer)提供>1000 I/O/mm²带宽,缩短模拟信号传输距离,降低寄生电容30%。

2)算法-硬件协同的近似ADC

针对视觉Transformer等对低位精度不敏感的模型,Meta研究非均匀量化ADC:

- 高位(MSB):保留高精度(1mV/LSB)

- 低位(LSB):粗略量化(10mV/LSB)

整体功耗降低30%,ImageNet Top-1准确率损失<0.3%。

3)可靠性设计

AR设备需在-20°C至60°C、85%湿度环境下工作。Meta采用:

- 温度自适应偏置:片上传感器动态调整运放偏置电流

- 老化补偿电路:监测NBTI/PBTI效应,定期校准关键节点

- 抗辐射设计:关键寄存器采用DICE单元(Dual Interlocked Storage Cell)

结论与行动指引

边缘AI的爆发,正在将混合信号电路工程师从"模拟专家"转变为"系统架构师"。成功的混合信号设计不再是"模拟电路做得多好",而是"系统-算法-电路如何协同得更好"。

观点回顾

- 系统级能效建模是起点:必须从AI任务特征出发,识别信息冗余,重构数据流。

- 数字辅助模拟是主流路径:用可编程性、算法补偿先进工艺的非理想性。

- ADC/DAC是感知计算单元:其架构需与AI工作负载深度耦合,具备动态配置、近似计算能力。

最后提醒 :在AI驱动的边缘计算时代,混合信号工程师的终极武器,不是更精密的运放,而是对AI任务本质的深刻理解。唯有如此,才能在纳米级晶体管与万亿级参数模型之间,架起那座高效、鲁棒、智能的桥梁。