在半导体光电子器件的发展历程中,垂直腔面发射激光器 (Vertical-Cavity Surface-Emitting Laser, VCSEL) 代表了激光二极管技术的一次重要飞跃。

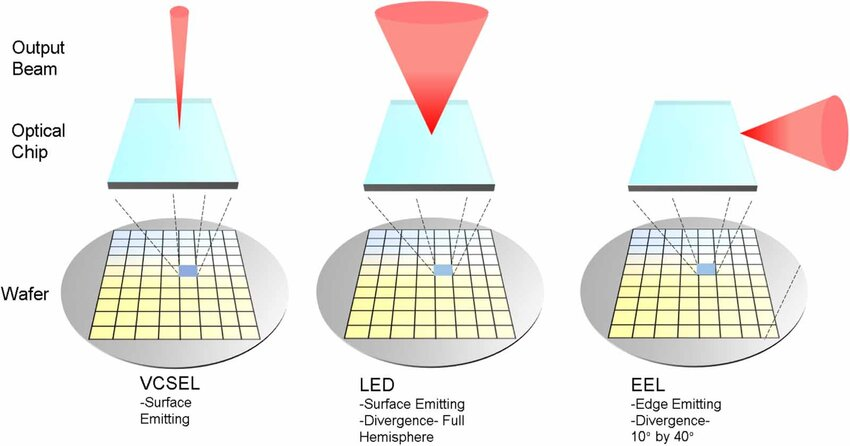

不同于传统的边发射激光器 (Edge-Emitting Laser, EEL) 依赖芯片解理面作为谐振腔反射镜,VCSEL 通过外延生长技术在垂直方向构建谐振腔,实现了光束垂直于衬底表面的出射。这种独特的几何结构赋予了 VCSEL 圆形光斑、低阈值电流以及晶圆级测试 (Wafer-Level Testing) 等显著优势。

本文将从微观物理层面出发,深入解析 VCSEL 的工作原理,并探讨其在现代光电系统中的应用价值。

01. 器件结构与物理机制

VCSEL 的设计不仅仅是材料的堆叠,更是一场在电学传导、光学谐振与热学管理之间寻求微妙平衡的艺术。其本质是一个一维光子晶体微腔 与量子阱增益介质的耦合系统。

VCSEL 的核心设计理念在于在极短的增益介质长度下实现激光振荡,这对谐振腔的设计提出了极高的要求。以下我们将剥开宏观结构的表象,深入探究其微观物理机制与设计痛点。

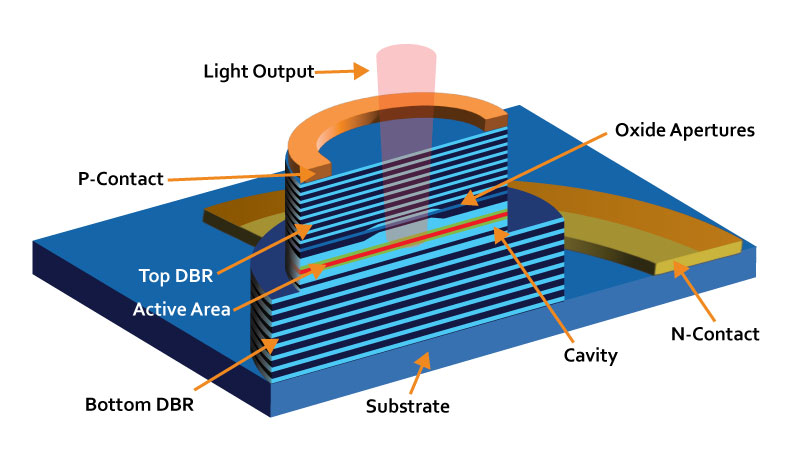

一个典型的 VCSEL 器件在纵向上可以被视为一个 法布里-珀罗 (Fabry-Pérot) 干涉仪,其主要外延结构包括以下三个部分:

1.1 分布式布拉格反射镜 (DBR):在矛盾物理场中寻求极限平衡

DBR 是 VCSEL 占据体积最大的部分(约占 90%),它绝不仅仅是一面镜子。从物理底层来看,设计 DBR 就是在解决光学反射 、电学传导 和能带势垒这三个互斥的物理难题。

A. 光学原理:为什么必须是 99.9% 反射率?

- 物理困境 :VCSEL 的核心痛点在于增益介质极短 (有源区厚度 d<50nmd < 50 nmd<50nm)。光子在有源区里穿梭一次,能激发的受激辐射微乎其微(单程增益 <1%<1\%<1%)。相比之下,边发射激光器(EEL)的光程长达数百微米,单程增益大得多。

- 工程解法 :为了让这么薄的介质产生激光,必须让光子在腔内往返振荡成百上千次,将微弱的增益累积起来。这就要求镜面的反射率 RRR 必须达到 99.9%。普通的金属镜面(如金、银)吸光损耗太大,根本无法胜任。

- 实现功能 :利用多层膜干涉原理 。我们交替生长高折射率 (nHn_HnH) 和低折射率 (nLn_LnL) 材料,每层厚度严格控制为 λ/4\lambda/4λ/4。

nHdH=nLdL=λ4n_H d_H = n_L d_L = \frac{\lambda}{4}nHdH=nLdL=4λ

这种结构迫使每一层界面的反射光在相位上完全重合(相长干涉)。几十层叠加后,形成了对特定波长的"光子禁带",实现了近乎全反射。

B. 材料原理:为什么 GaAs 基比 InP 基更好做?

- 物理困境 :外延生长工艺总有误差,工作温度变化也会导致波长漂移。如果 DBR 的反射带宽(高反带)太窄,稍微一点温度变化,激光波长就会跑出反射带,导致器件停振。带宽宽度由折射率反差 (Δn\Delta nΔn) 决定。

- 工程解法 :选择 AlAs/GaAsAlAs/GaAsAlAs/GaAs 材料体系。它们的折射率差很大 (Δn≈0.6\Delta n \approx 0.6Δn≈0.6),仅需 20-30 对就能形成很宽的反射带(~100nm),容错率极高。

- 对比反思 :长波长(1300/1550nm)通常用 InP 基材料,其折射率差很小 (Δn≈0.2\Delta n \approx 0.2Δn≈0.2)。为了达到同样的反射率,需要堆叠 50 对以上,且带宽极窄。这就是为什么长波长 VCSEL 极难制造,往往需要依靠晶圆键合技术将 GaAs DBR "嫁接"过去。

C. 电光博弈:如何让镜子导电?(调制掺杂)

- 物理困境 :这是 VCSEL 设计中最反直觉的矛盾。

- 光学的要求:为了减少光损耗,材料越纯越好(低掺杂)。

- 电学的要求 :电流必须穿过 DBR 注入有源区,根据欧姆定律,为了低电阻,材料必须重掺杂。

然而,自由载流子(电子/空穴)会直接吸收光子(自由载流子吸收 FCA),重掺杂会毁掉反射率。

- 工程解法 :调制掺杂 (Modulation Doping) 。

利用腔内的驻波 (Standing Wave) 特性。光场在腔内的分布是不均匀的,有波腹(光强最大)和波节(光强接近零)。

我们玩了一个"空间魔术":在波节 (Node) 位置进行高浓度掺杂 以导电(反正这里没光,吸不到);在波腹 (Antinode) 位置保持低掺杂以透光。 - 实现功能:在不牺牲光学性能的前提下,强行打通了电流路径。

D. 能带工程:如何消除电阻尖峰?(渐变界面)

- 物理困境 :当两种不同材料(如 AlAs 和 GaAs)接触时,由于带隙不同,界面处会形成尖锐的势垒 (Band Spike) 。

电流穿过一个 DBR 界面,就像翻越一座小山。对于 P 型 DBR,空穴有效质量大,翻山极难。如果有 30 对 DBR,就相当于串联了 30 个反向二极管,会产生巨大的电压降和焦耳热,直接烧毁器件。 - 工程解法 :组分渐变 (Graded Interface) 。

我们在生长界面时,不让组分突然变化,而是插入一层 20nm 厚的过渡层,让铝组分从 0% 线性或抛物线渐变到 100%。

这就把尖锐的"垂直峭壁"磨成了平缓的"坡道"。 - 实现功能 :利用热发射辅助隧穿机制,让载流子顺滑通过界面,将串联电阻降低 1-2 个数量级,这是 VCSEL 能在室温连续工作的关键。

1.2 量子阱有源区:应变工程与增益失谐

如果说 DBR 是 VCSEL 的骨架,那么量子阱有源区就是它的心脏。在现代高性能 VCSEL(特别是高速数据通信和 3D 传感芯片)中,设计者不再追求"完美的晶格匹配"和"完美的波长对准",而是反其道而行之,利用应变 (Strain) 和失谐 (Detuning) 这两把物理钥匙,解锁了器件性能的上限。

A. 应变工程 (Strain Engineering):为了"更轻",所以"挤压"

在早期的半导体激光器设计教科书中,原则通常是"晶格匹配",以避免缺陷。但在高性能 VCSEL 中,我们通常在 GaAs 衬底上生长 InGaAs (铟镓砷) 量子阱。由于铟原子 (In) 比镓原子 (Ga) 大,InGaAs 的晶格常数比 GaAs 大。强行把它长在 GaAs 上,晶格就会被横向压缩------这就是压缩应变 (Compressive Strain) 。

我们为什么要故意引入这种"痛苦"的应力?

-

物理困境:重空穴的惰性

在无应变的体材料 GaAs 中,价带顶部的重空穴带 (Heavy Hole, HH) 和轻空穴带 (Light Hole, LH) 是简并 (Degenerate) 的(即能量重合)。

- 有效质量大 :重空穴的有效质量 m∗m^*m∗ 很大。

- 态密度过高 :根据态密度公式 ρ(E)∝(m∗)3/2\rho(E) \propto (m^*)^{3/2}ρ(E)∝(m∗)3/2,质量大意味着态密度极大。

- 后果 :态密度大意味着能级像一个"巨大的水桶",你需要注入海量的载流子才能把它填满(实现粒子数反转)。这就导致了激光器的阈值电流很高 。

-

工程解法:打破简并

引入压缩应变后,晶格对称性被破坏,价带发生剧烈变化:

- 简并解除 :重空穴带 (HH) 和轻空穴带 (Light Hole) 在 Γ\GammaΓ 点 (k=0k=0k=0) 分离。

- 质量变轻 :最顶端的价带(参与发光的能带)变成了类轻空穴性质。其平行方向的有效质量大幅降低。

- 态密度降低:因为质量变轻,"大水桶"变成了"细试管"。

-

实现功能:性能跃迁

- 更低阈值:只需要很少的载流子就能填满能带,实现粒子数反转。阈值电流密度显著下降。

- 更高增益 :微分增益 dg/dNdg/dNdg/dN 大幅提升。这意味着同样的电流变化能激发出更多的光子,直接提升了 VCSEL 的调制带宽 (Modulation Bandwidth) ,这是实现 25G/50G 高速通信的物理基础。

B. 增益-腔模失谐 (Gain-Cavity Detuning):一场预谋的"追逐赛"

VCSEL 的另一个反直觉设计在于波长的选择。在室温下测量一颗优秀的 VCSEL 芯片,你会发现它的增益峰值波长 (Gain Peak) 和谐振腔模式波长 (Cavity Mode) 根本不对齐,通常偏差 10-15 nm。

这不是制造误差,而是极具智慧的热管理设计。

-

物理困境:不同步的红移

VCSEL 在工作时会发热(注入电流产生的焦耳热 + 环境温度)。半导体材料对温度非常敏感,但增益 和折射率对温度的响应速度截然不同:

- 增益峰红移 :随着温度升高,半导体带隙 EgE_gEg 收缩(Varshni 关系)。增益峰波长红移速度极快,约为 ∼0.32nm/∘C\sim 0.32 nm/^\circ C∼0.32nm/∘C 。

- 腔模红移 :谐振腔波长由折射率 nnn 决定 (λ=2nL/m\lambda = 2nL/mλ=2nL/m)。折射率随温度变化较小,腔模红移速度较慢,约为 ∼0.07nm/∘C\sim 0.07 nm/^\circ C∼0.07nm/∘C 。

-

工程解法:负失谐设计 (Negative Detuning)

如果我们在室温 (25∘C25^\circ C25∘C) 下将两者完美对齐:

- 当芯片工作温度升到 85∘C85^\circ C85∘C(数据中心标准工况)时,增益峰会像"跑车"一样迅速红移,把像"卡车"一样的腔模远远甩在后面。

- 后果:腔模波长处得不到足够的增益,导致激光器在高温下功率暴跌,甚至停振。

正确的做法是"抢跑" :

在室温设计时,故意把腔模波长 设定在增益峰波长 的长波方向(例如:增益峰 840nm,腔模 850nm)。

-

实现功能:高温下的完美相遇

- 室温 (25∘C25^\circ C25∘C) :两者失谐,阈值电流稍高,效率略低(但没关系,室温下本来就容易激射)。

- 高温 (85∘C85^\circ C85∘C) :随着温度升高,增益峰跑得快,腔模跑得慢。增益峰逐渐"追上"了腔模。

- 模式对准 (Mode Alignment) :在设计的工作温度点(如芯片结温 80−90∘C80-90^\circ C80−90∘C),两者完美重合。

这种设计确保了 VCSEL 在最恶劣的高温工况下,反而拥有最低的阈值 和最高的效率,极大地提升了器件的可靠性。

3. 氧化限制层:有效折射率模型与横模控制

氧化层形成的孔径不仅限制电流,更通过改变有效折射率 (Effective Index) 决定了激光是单模还是多模。

-

有效折射率模型 :

我们可以将 VCSEL 垂直方向等效为一个圆柱波导。中心未氧化区域折射率较高 (ncoren_{core}ncore),周围氧化区域折射率较低 (ncladn_{clad}nclad)。这个折射率差 Δneff\Delta n_{eff}Δneff 决定了波导对光场的束缚能力。

-

V 参数与单模条件 :

类比光纤理论,归一化频率 VVV 参数决定了容纳的模式数量:

V=2πaλncore2−nclad2V = \frac{2\pi a}{\lambda} \sqrt{n_{core}^2 - n_{clad}^2}V=λ2πancore2−nclad2 -

单模 VCSEL :当氧化孔径 aaa 很小(通常 <4μm<4 \mu m<4μm)时,仅基模 (LP01LP_{01}LP01) 满足振荡条件,输出理想的高斯光束,适合 3D 传感的点阵投射。

-

多模 VCSEL :当孔径较大(>10μm>10 \mu m>10μm)时,高阶横模 (LP11,LP21...LP_{11}, LP_{21}...LP11,LP21...) 开始起振,光斑呈现甜甜圈状或复杂的散斑,但输出功率更高,适合 LiDAR 的泛光照明。通过精确控制氧化孔径的直径和氧化层的厚度,设计者可以在"高功率"与"高光束质量"之间进行权衡。

02. 阈值增益分析

理解 VCSEL 设计难点的关键在于激光器的阈值增益公式。对于法布里-珀罗激光器,阈值增益系数 gthg_{th}gth 满足:

Γgth=αi+12Lln(1R1R2)\Gamma g_{th} = \alpha_i + \frac{1}{2L} \ln\left(\frac{1}{R_1 R_2}\right)Γgth=αi+2L1ln(R1R21)

其中:

- Γ\GammaΓ 为光限制因子。

- αi\alpha_iαi 为内部损耗(如自由载流子吸收、散射损耗)。

- LLL 为谐振腔的有源区长度。

- R1,R2R_1, R_2R1,R2 为前后反射镜的反射率。

物理阐释 :

对于 EEL,腔长 LLL 通常在 200μm200 \mu m200μm 到 1mm1 mm1mm 之间,因此 12L\frac{1}{2L}2L1 项较小,对反射率 RRR 的要求不高(约 30%)。

而对于 VCSEL,有效腔长 LLL 仅为微米量级(∼1μm\sim 1 \mu m∼1μm)。为了使阈值增益 gthg_{th}gth 保持在材料可承受的范围内,必须使 ln(1/R1R2)\ln(1/R_1 R_2)ln(1/R1R2) 极小,这就从数学上解释了为什么 VCSEL 必须依赖反射率高达 99% 以上的 DBR 结构。

03. 性能对比:VCSEL, EEL 与 LED

从器件物理特性的角度,我们可以对三种主流光源进行如下对比分析:

| 性能指标 | VCSEL (面发射) | EEL (边发射) | LED (发光二极管) |

|---|---|---|---|

| 发光机理 | 受激辐射 (谐振腔) | 受激辐射 (谐振腔) | 自发辐射 (无腔) |

| 光束特性 | 圆形高斯光束,低发散角 (<15°) | 椭圆形光束,发散角大 | 朗伯光源,非相干光 |

| 光谱特性 | 窄线宽 (<1nm),波长稳定 | 较窄 | 宽光谱,色散大 |

| 测试性 | 晶圆级测试 (WLT) | 需切割、镀膜后测试 | 晶圆级测试 |

| 封装与耦合 | 易于与光纤/透镜耦合 | 需复杂的光学整形 | 简单 |

| 功率密度 | 中等 (阵列化可提高功率) | 高 | 低 |

| 调制带宽 | 高 (可达 25Gbps+) | 较高 | 低 (MHz 量级) |

工程意义 :

VCSEL 结合了 LED 的低制造成本(得益于晶圆级测试和筛选)和 EEL 的优良光学特性。这使其成为短距离高密度互连和消费级传感的首选方案。

04. 主要应用场景与技术演进深度解析

VCSEL 的应用史,是一部从"光互连"到"光感知"的宏大技术叙事。不同的应用场景对器件的物理特性提出了截然不同的极限挑战:数据通信追求极速的带宽 ,消费电子追求极致的精度与微型化 ,而车载雷达则追求极高的功率密度与可靠性。

4.1 数据通信 (Datacom):算力时代的流量动脉

数据中心是 VCSEL 的发源地。在 AI 算力和云计算爆发的今天,服务器与交换机之间 <100m<100m<100m 的短距互连(SR 场景),90% 以上由 850nm VCSEL + 多模光纤 (OM3/OM4) 承担。

-

物理瓶颈:带宽的"30GHz 天花板"

过去,光模块主要使用 NRZ (不归零码) 调制(亮=1,灭=0)。要提升速率,必须提高激光器的"开关速度"(弛豫振荡频率 frf_rfr)。

然而,受限于半导体材料的载流子复合寿命 和封装引入的寄生电容/电感 ,VCSEL 的 -3dB 物理带宽很难突破 30 GHz。这使得单通道 50 Gbps 成为了 NRZ 调制的物理极限。

-

演进方案:PAM4 高阶调制与 DSP

为了在不增加物理带宽的前提下翻倍速率,行业标准(IEEE 802.3bs/cd)转向了 PAM4 (四电平脉冲幅度调制) 。

- 原理:将光功率细分为 0, 1, 2, 3 四个台阶。一个符号 (Symbol) 携带 2 bit 信息。

- 新挑战:线性度与噪声 。NRZ 仅需区分"开/关",容错率高;但 PAM4 需要精准区分"33% 亮度"和"66% 亮度",眼图(Eye Diagram)中眼睛高度变成了原来的 1/3。这要求 VCSEL 具有极高的线性度 和极低的相对强度噪声 (RIN) 。

- DSP 引入 :现代光模块内部集成了 DSP 芯片,利用前馈均衡 (FFE) 和判决反馈均衡 (DFE) 算法,在电域上补偿 VCSEL 的非线性损伤。

4.2 三维传感 (3D Sensing):从 FaceID 到"光子尺"

2017 年 iPhone X 的发布标志着 VCSEL 走出机房,进入消费电子。在这里,VCSEL 不再是通信载体,而是高精度的测量尺。

-

结构光 (Structured Light):波长稳定性的极致考验

- 原理 :VCSEL 阵列发出的光经过 DOE (衍射光学元件) ,被"打散"成 3 万个具有特定编码的散斑点(特征光场)。摄像头通过捕捉光斑在物体表面的畸变来计算深度信息。

- 技术痛点 :DOE 的衍射角度 θ\thetaθ 与波长 λ\lambdaλ 严格相关。如果 VCSEL 工作发热导致波长漂移(红移),投射出的散斑位置就会偏移,可能导致刷脸失败。

- 解决方案 :

- 波长选择 :从 850nm 转向 940nm。因为太阳光在 940nm 处被大气水分吸收,背景噪声最低(Solar Blind Region)。

- 外延设计:通过调整量子阱的应变设计,降低波长的温漂系数。

-

飞行时间 (ToF):纳秒级脉冲的爆发力

- 原理 :dToF (Direct Time-of-Flight) 像雷达一样,测量光脉冲发射与返回的时间差。光速 c=3×108m/sc = 3 \times 10^8 m/sc=3×108m/s,意味着 1cm 的距离对应的时间差仅为 67 皮秒。

- 技术痛点 :要求 VCSEL 发射脉宽极窄 (<5ns) 且 上升沿极陡 (<500ps) 的光脉冲。

- 封装革命 :传统的金线键合 (Wire Bonding) 会引入数 nH 的寄生电感,阻碍电流的瞬间突变。现代 dToF 模组普遍采用 Flip-chip (倒装) 技术,将 VCSEL 芯片直接扣在驱动 IC 上,实现极低电感互连。

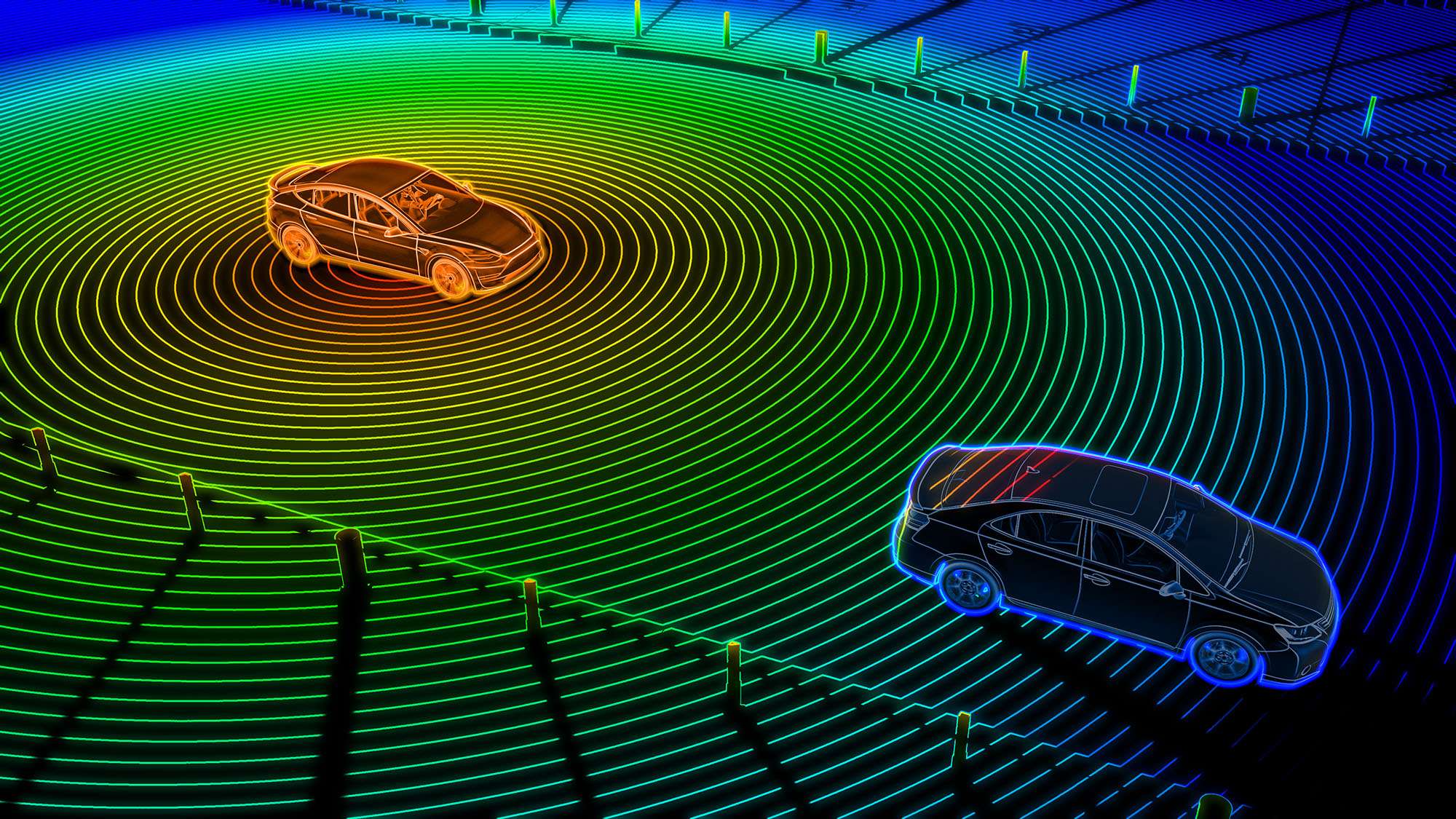

4.3 汽车激光雷达 (Automotive LiDAR):多结技术的功率革命

这是 VCSEL 目前最前沿的战场。为了探测 200 米处反射率仅 10% 的黑色物体,光源必须输出数百瓦的峰值功率,这远远超出了传统单层 VCSEL 的物理极限。

-

多结技术 (Multi-junction):摩天大楼式的堆叠

传统 VCSEL 只有一个有源区,量子效率 η<1\eta < 1η<1(一个电子最多产生一个光子)。

- 原理 :通过隧道结 (Tunnel Junction) ,在垂直方向上串联多个有源区(3结、5结甚至 9结)。隧道结利用重掺杂 (p++/n++p^{++}/n^{++}p++/n++) 实现电子的量子隧穿,使同一个电子穿过第一层发光后,能"满血复活"进入第二层再次发光。

- 优势 :

- 功率倍增:斜率效率 (Slope Efficiency) 从 1 W/A 提升至 >4 W/A。

- 驱动优化 :在产生相同光功率时,多结 VCSEL 所需电流是单结的 1/N1/N1/N。由于驱动电路的欧姆损耗 Ploss=I2RP_{loss} = I^2 RPloss=I2R,电流减小意味着系统发热量呈指数级下降。

-

全固态扫描 (Solid State Scanning):消灭机械部件

传统的机械旋转雷达笨重且昂贵。VCSEL 带来了可寻址阵列 (Addressable Array) 的可能性。

- 原理:将一颗 VCSEL 芯片分割成数千个独立的像素区域(分区点亮)。通过驱动电路控制,依次点亮不同区域,像控制屏幕像素一样,实现对空间的"电子扫描"。

- 终极形态 :纯固态激光雷达 (Solid-State LiDAR) 。结合 SPAD 面阵探测器,没有任何机械运动部件,尺寸仅有火柴盒大小,却能构建高分辨率的 3D 点云。

05. 总结与展望

作为一种高度集成的半导体光源,VCSEL 已经证明了其在光通信和消费电子领域的统治力。然而,面向未来,技术界仍需克服若干挑战:

- 长波长技术:InP 基长波长 (1300/1550nm) VCSEL 受限于 DBR 材料的折射率差,制作难度大。晶圆键合 (Wafer Bonding) 技术是目前的解决思路之一。

- 偏振控制:由于圆柱对称结构,VCSEL 的偏振态通常是不稳定的。引入非对称结构控制偏振是保偏应用的关键。

- 高功率密度散热:随着多结技术带来的热流密度增加,封装级的热管理设计变得至关重要。

综上所述,VCSEL 正处于从"消费级"向"工业/车规级"跨越的关键时期,其在光电集成系统中的核心地位将愈发稳固。