一 真题2009-44

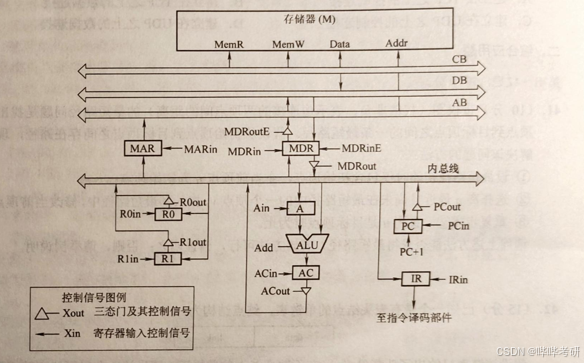

2009-44题. 某计算机字长为 16 位,采用 16 位定长指令字结构,部分数据通路结构如下图所示,图中所有控制信号为 1 时表示有效、为 0 时表示无效。例如,控制信号 MDRinE 为 1 表示允许数据从 DB 打入 MDR,MDRin 为 1 表示允许数据从内总线打入 MDR。假设 MAR 的输出一直处于使能状态。加法指令 "ADD (R1),R0 "的功能为 (R0)+((R1))→(R1),即将 R0 中的数据与 R1 的内容所指主存单元的数据相加,并将结果送入 R1 的内容所指主存单元中保存。下表给出了上述指令取指和译码阶段每个节拍(时钟周期)的功能和有效控制信号,请按表中描述方式用表格列出指令执行阶段每个节拍的功能和有效控制信号。

| 时钟 | 功能 | 有效控制信号 |

|---|---|---|

| C1 | MAR←(PC) | PCout,MARin |

| C2 | MDR←M(MAR) PC←(PC)+1 | MemR,MDRinE,PC+1 |

| C3 | IR←(MDR) | MDRout,IRin |

| C4 | 指令译码 | 无 |

二 题目要素解析

场景: 单周期 / 多周期 CPU 数据通路中,执行一条寄存器间接寻址的加法指令。

已知条件:

-

指令功能:

(R0) + ((R1)) → (R1)(R1):R1 寄存器中的内容是主存地址。((R1)):该地址指向的主存单元中的数据。- 相加:R0 的数据与该主存数据相加。

- 存储:结果写回

(R1)指向的主存单元。

-

数据通路结构:包含 MAR、MDR、通用寄存器 R0/R1、ALU、PC、IR 等模块。

-

控制信号定义:

Xin为寄存器输入使能,Xout为寄存器输出使能,三态门控制信号控制总线连接。

核心考点: 指令执行阶段的数据流推导、控制信号生成,多周期 CPU 的微操作序列设计。

三 哔哔详解

3.1 取指阶段

题目中C1-C4是取指阶段

| 时钟 | 功能 | 数据流详细说明 | 有效控制信号 |

|---|---|---|---|

| C1 | MAR ← (PC) | 程序计数器 PC 保存着下一条要执行指令的地址。为了从主存中取指令,首先要把这个地址送到地址寄存器 MAR。 数据流向:PC → 内总线 → MAR | PCout(PC 输出到内总线),MARin(内总线数据打入 MAR) |

| C2 | MDR ← M(MAR) PC ← (PC)+1 | 1. MAR 将地址输出到地址总线 AB,主存根据这个地址读出指令,通过数据总线 DB 送入 MDR。 2. 同时,PC 自动加 1,指向下一条指令的地址,为取下一条指令做准备。 数据流向:M(MAR) → DB 总线 → MDR;PC → PC+1 | MemR(主存读使能),MDRinE(从 DB 总线加载 MDR),PC+1(PC 自增) |

| C3 | IR ← (MDR) | MDR 中存放的是刚从主存读出的指令,需要把它送到指令寄存器 IR 中,以便后续译码。 数据流向:MDR → 内总线 → IR | MDRout(MDR 输出到内总线),IRin(内总线数据打入 IR) |

| C4 | 指令译码 | IR 中的指令被送到指令译码部件,识别出这是 ADD (R1), R0 指令,并确定其寻址方式和操作类型,为执行阶段生成控制信号做准备。 |

无(纯组合逻辑,不需要时钟触发) |

3.2 执行周期

指令功能拆解

ADD (R1), R0 执行过程可分为四步:

① 取 R1 中的地址 → 送 MAR

② 从 MAR 指向的主存单元取数 → 送 MDR,再到 ALU

③ 取 R0 中的数据 → 送 ALU,与 MDR 的数据相加

④ 将 ALU 的结果 → 送 MDR,再写回主存

数据流与控制信号对应

-

第一步(C5):MAR ← (R1)

R1 的内容是主存地址,需要放到 MAR 里去读内存。

控制信号:R1out(R1 输出到内总线),MARin(内总线数据打入 MAR)。

-

第二步(C6):MDR ← M (MAR)

从主存中读出(R1)指向的数据,放到 MDR 中。

控制信号:MemR(主存读有效),MDRinE(从 DB 总线加载 MDR)。

-

第三步(C7):A ← (R0)

将 R0 中的操作数加载到 ALU 的 A 输入端。

控制信号:R0out(R0 输出到内总线),Ain(内总线数据打入 A 寄存器)。

-

第四步(C8):AC ← (A) + (MDR)

ALU 执行加法,结果存入 AC 暂存器。

控制信号:MDRout(MDR 输出到内总线),Add(ALU 执行加法),ACin(ALU 结果打入 AC)。

-

第五步(C9):MDR ← (AC)

将加法结果从 AC 加载到 MDR,准备写回主存。

控制信号:ACout(AC 输出到内总线),MDRin(内总线数据打入 MDR)。

-

第六步(C10):M (MAR) ← (MDR)

将 MDR 中的结果写回(R1)指向的主存单元。

控制信号:MDRoutE(MDR 输出到 DB 总线),MemW(主存写有效)。

| 时钟 | 功能 | 数据流向 | 有效控制信号 |

|---|---|---|---|

| C5 | MAR ← (R1) | R1 输出 → 内总线 → MAR | R1out(R1 输出到内总线),MARin(内总线数据打入 MAR) |

| C6 | MDR ← M(MAR) | MAR 输出地址到主存 → 主存通过 DB 总线送数据到 MDR | MemR(主存读使能),MDRinE(从 DB 总线加载 MDR) |

| C7 | A ← (R0) | R0 输出 → 内总线 → ALU 的 A 输入端 | R0out(R0 输出到内总线),Ain(内总线数据打入 A 寄存器) |

| C8 | AC ← (A) + (MDR) | MDR 输出 → 内总线 → ALU 的另一输入端; ALU 执行加法,结果存入 AC | MDRout(MDR 输出到内总线),Add(ALU 执行加法),ACin(ALU 结果打入 AC) |

| C9 | MDR ← (AC) | AC 输出 → 内总线 → MDR | ACout(AC 输出到内总线),MDRin(内总线数据打入 MDR) |

| C10 | M(MAR) ← (MDR) | MDR 输出 → DB 总线 → 主存 | MDRoutE(MDR 输出到 DB 总线),MemW(主存写使能) |

四 参考答案

| 时钟 | 功能 | 有效控制信号 |

|---|---|---|

| C5 | MAR ← (R1) | R1out,MARin |

| C6 | MDR ← M(MAR) | MemR,MDRinE |

| C7 | A ← (R0) | R0out,Ain |

| C8 | AC ← (A) + (MDR) | MDRout,Add,ACin |

| C9 | MDR ← (AC) | ACout,MDRin |

| C10 | M(MAR) ← (MDR) | MDRoutE,MemW |

五 考点精析

5.1 数据通路介绍

5.1.1 基本概念

数据通路 (Data Path) 是指 CPU 内部用于传输、暂存和处理数据的硬件资源集合及其互连结构。它在控制器发出的控制信号驱动下,完成指令执行过程中所需的所有数据操作。

📌 核心关键词:

- CPU 内部(不包括主存、I/O 设备)

- 硬件资源(寄存器、ALU、总线等)

- 受控于控制信号

5.1.2 功能作用

| 维度 | 说明 |

|---|---|

| 主要功能 | 1. 在寄存器之间传输数据 2. 将操作数送入 ALU 进行运算 3. 暂存中间结果或访存数据 4. 与主存交互(通过 MAR/MDR) |

| 核心作用 | - 实现指令的执行逻辑 - 构成 CPU 的执行单元(Execution Unit) - 与控制器共同构成完整 CPU |

5.1.3 常见组成部件

数据通路由以下内部功能部件构成:

| 部件 | 功能说明 | 是否属于数据通路 |

|---|---|---|

| 程序计数器(PC) | 存放下一条指令地址 | ✅ 是 |

| 指令寄存器(IR) | 存放当前正在执行的指令 | ✅ 是 |

| 存储器地址寄存器(MAR) | 存放要访问的主存地址 | ✅ 是 |

| 存储器数据寄存器(MDR) | 缓冲 CPU 与主存之间的数据 | ✅ 是 |

| 通用寄存器(如 R0, R1) | 暂存操作数或地址 | ✅ 是 |

| 累加器(AC) | ALU 运算结果的默认暂存器 | ✅ 是 |

| 算术逻辑单元(ALU) | 执行加、减、与、或等运算 | ✅ 是 |

| 内部总线(单/多总线) | 连接各部件的数据通道 | ✅ 是 |

| 多路选择器(MUX) | 选择不同数据源输入 ALU 或寄存器 | ✅ 是 |

| 主存储器(Memory) | ❌ 不属于数据通路(属于外部存储系统) | |

| I/O 设备 | ❌ 不属于数据通路 |

⚠️ 重要澄清 :

"数据通路"仅指 CPU 芯片内部的结构 ,不包括主存、硬盘、键盘等外部设备。常有考生误将"内存"当作数据通路部件,这是错误的。

5.1.4 典型数据通路结构

1. 单总线结构

- 所有寄存器通过一条共享内总线连接

- 同一时刻只能有两个部件通信(一个输出,多个可输入)

- 优点:结构简单

- 缺点:速度慢,需多节拍完成复杂操作

- 408 默认模型(如 2009-44 题)

2. 双总线 / 多总线结构

- 分设专用总线(如 ALU 输入总线、结果总线)

- 提高并行性,减少节拍数

- 现代 CPU 常用,但 408 一般不要求设计

5.1.5 控制信号与数据通路部件的对应关系

- 必须掌握关键信号含义:

Xout:寄存器 X 输出到内总线Xin:内总线数据打入寄存器 XMDRinE:从外部数据总线 DB(主存)加载 MDRMDRoutE:MDR 输出到 DB 总线(写主存)MemR/MemW:主存读/写使能

5.1.6 数据通路易错点

| 错误认知 | 正确认知 |

|---|---|

| "内存是数据通路的一部分" | ❌ 内存是外部存储器,数据通路只含 MAR/MDR 等接口寄存器 |

| "数据通路包含 I/O 接口" | ❌ I/O 属于系统总线外设,不在 CPU 数据通路内 |

| "ALU 可直接读写内存" | ❌ 必须通过 MDR 中转 |

| "所有数据都走同一条总线" | ✅ 在单总线模型中成立,但需分时复用 |

5.2 控制信号

5.2.1 基本概念

控制信号 是由 CPU 中的 控制器 (Controller) 产生的二进制电信号 (通常为 0/1),用于激活或禁止数据通路中特定部件的操作,从而协调各硬件单元按指令要求完成微操作。

📌 核心关键词:

- 由 控制器生成

- 作用于 数据通路

- 决定 "何时做"和"怎么做"

5.2.2 功能与作用

| 维度 | 说明 |

|---|---|

| 主要功能 | 1. 控制寄存器的输入/输出(如 R0out, MARin) 2. 选择 ALU 运算类型(如 Add, Sub) 3. 启动主存读写(MemR, MemW) 4. 控制总线门电路的通断 |

| 核心作用 | - 驱动数据通路工作 - 实现指令的时序控制 - 确保数据在正确节拍流向正确位置 |

5.2.3 常见控制信号

| 控制信号 | 含义 | 作用对象 | 典型使用场景 |

|---|---|---|---|

PCout |

PC 输出到内总线 | PC 寄存器输出门 | 取指阶段 C1 |

MARin |

内总线数据打入 MAR | MAR 输入使能 | 地址加载 |

MDRin |

内总线数据打入 MDR | MDR 输入门(来自 CPU 内部) | 写内存前缓存数据 |

MDRinE |

外部 DB 总线 数据打入 MDR | MDR 输入门(来自主存) | 读内存 |

MDRout |

MDR 输出到内总线 | MDR 输出门 | 送数据到 ALU 或寄存器 |

MDRoutE |

MDR 输出到 外部 DB 总线 | MDR 输出门(对外) | 写内存 |

IRin |

内总线数据打入 IR | IR 输入使能 | 指令加载 |

R0out / R0in |

R0 输出/输入 | 通用寄存器 | 操作数传送 |

ACout / ACin |

累加器输出/输入 | AC 寄存器 | ALU 结果暂存 |

MemR |

主存读使能 | 存储器控制端 | 从内存读数据 |

MemW |

主存写使能 | 存储器控制端 | 向内存写数据 |

Add |

ALU 执行加法 | ALU 操作选择 | 加法运算 |

Sub |

ALU 执行减法 | ALU 操作选择 | 减法运算 |

PC+1 |

PC 自增 | PC 计数逻辑 | 取指后指向下一条指令 |

⚠️ 关键区分:

MDRinvsMDRinE:前者来自 CPU 内总线 ,后者来自 主存(DB 总线)MDRoutvsMDRoutE:前者送入 CPU 内部 ,后者送入 主存

5.2.4 控制信号的生成方式

| 控制器类型 | 控制信号生成方式 | 特点 |

|---|---|---|

| 硬布线控制器 | 由组合逻辑电路直接生成 | 速度快,但不易修改 |

| 微程序控制器 | 从控制存储器中读取微指令生成 | 灵活性高,速度较慢 |

5.2.5 易错点

| 错误认知 | 正确认知 |

|---|---|

| "控制信号是数据" | ❌ 控制信号是命令,不是被处理的数据 |

| "MDRinE 用于写内存" | ❌ MDRinE 用于读内存;写内存用 MDRin + MDRoutE |

| "PC+1 是一个独立节拍" | ❌ 通常与取指并行(如 C2 同时完成 MemR 和 PC+1) |

| "ALU 有独立控制信号 Add/Sub" | ✅ 正确!这是标准设计 |

六 考点跟踪

| 年份 | 题号 | 考查内容 | CSDN 参考链接 | VX参考链接 | |

|---|---|---|---|---|---|

| 2009 | 第44题 | 多周期 CPU 指令执行阶段的微操作与控制信号 | |||

| 2015 | 第43题 | CPU数据流、寄存器使用、ALU控制、数据通路 | |||

| 2015 | 第44题 | 数据通路 |

说明 :本文内容基于公开资料整理,参考了包括但不限于《数据结构》(严蔚敏)、《计算机操作系统》(汤小丹)、《计算机网络》(谢希仁)、《计算机组成原理》(唐朔飞)等国内高校经典教材,以及其他国际权威著作。同时,借鉴了王道、天勤、启航等机构出版的计算机专业考研辅导系列丛书 中的知识体系框架与典型题型分析思路。文中所有观点、例题解析及文字表述均为作者结合自身理解进行的归纳与重述,未直接复制任何出版物原文。内容仅用于学习交流,若有引用不当或疏漏之处,敬请指正。