一、时钟系统定义

定义:时钟系统是整个系统的心脏,它决定了处理器、外设以及总线的运行速度。

二、主要时钟源

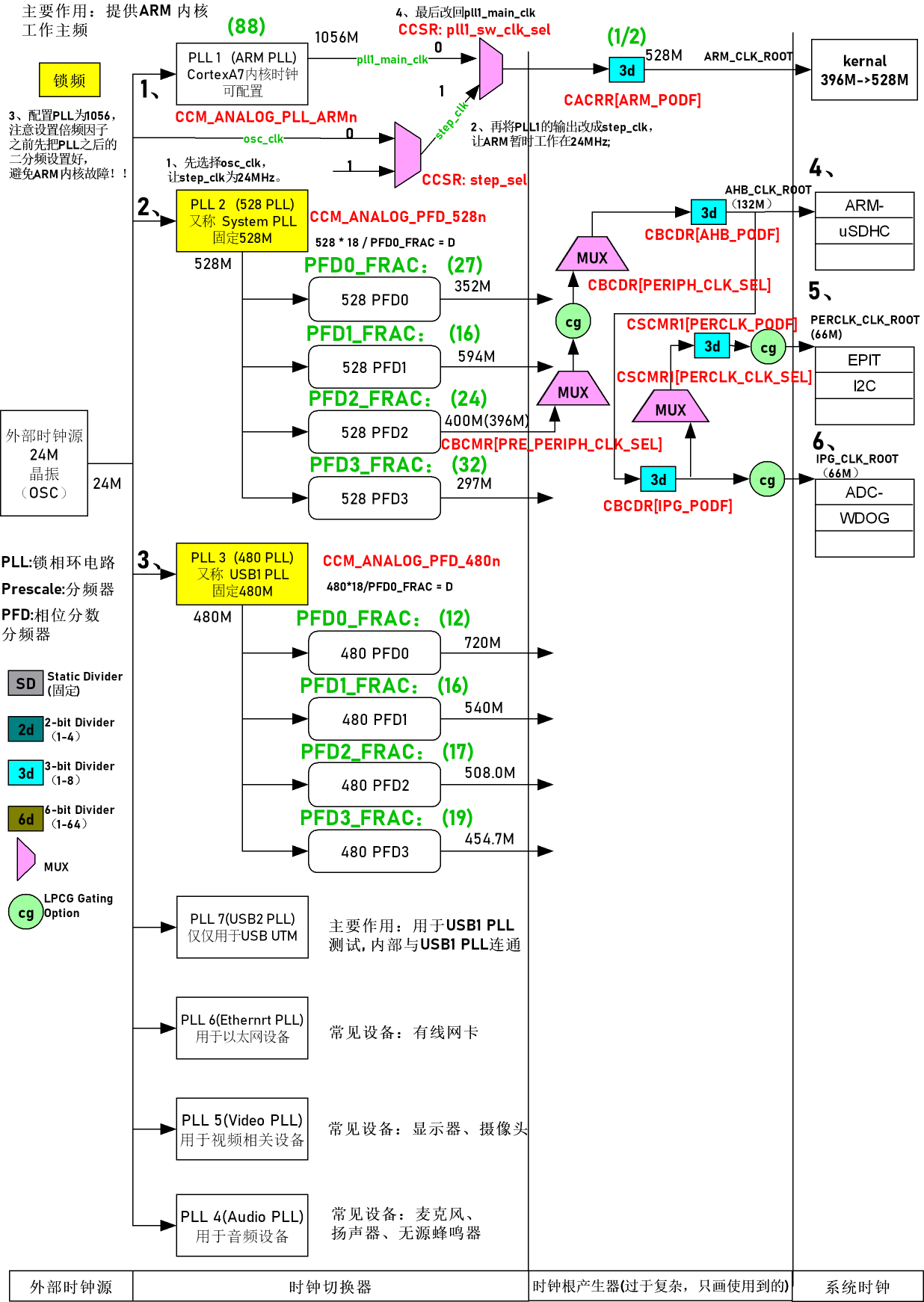

时钟源的概念:整个时钟系统的基础,提供基本的时钟信号。i.MX6ULL的主要时钟源包括外部晶振(XTAL)和内部锁相环(PLL)产生的高频时钟。

PLL(phase locked loop)锁相环电路: 倍频

Prescale 分频器: 分频

PFD(phase fractional Prescale)相位分数分频器: 输出频率可升可降

1.主要时钟源

- XTAL时钟:外部晶振提供基础时钟源

- PLL系统:包括ARM PLL、528MHz PLL、480MHz PLL等

- 时钟分频器:用于生成不同频率的时钟信号

2.时钟域的划分

- ARM Clock:CPU核心时钟

- AHB Clock:高级高性能总线时钟

- IPG Clock:外设接口时钟

- PERCLK Clock:外设时钟

三、时钟整体架构

四、时钟的工作流程

1.ARM内核时钟(Kernel Clock)配置

| 步骤 | 操作 | 寄存器 | 配置说明 | 目标时钟 |

|---|---|---|---|---|

| 1 | 选择osc_clk | CCM->CCSR | 让step_clk为24MHz | 24MHz |

| 2 | 临时切换 | CCM->CCSR | 将PLL1输出改为step_clk | 24MHz |

| 3 | 配置PLL | CCM_ANALOG->PLL_ARM | 设置输出为1056MHz,先配置二分频 | 1056MHz |

| 4 | 恢复主时钟 | CCM->CCSR | 改回pll1_main_clk | 1056MHz |

2.528MHz PLL配置

| 步骤 | 操作 | 寄存器 | 配置说明 | 目标时钟 |

|---|---|---|---|---|

| 1 | 配置PFD | CCM_ANALOG->PFD_528 | 设置528MHz时钟源 | 528MHz |

3.480MHz PLL配置

| 步骤 | 操作 | 寄存器 | 配置说明 | 目标时钟 |

|---|---|---|---|---|

| 1 | 配置PFD | CCM_ANALOG->PFD_480 | 设置480MHz时钟源 | 480MHz |

4.AHB_CLK_ROOT配置(132MHz)

| 步骤 | 操作 | 寄存器 | 位域 | 配置说明 | 目标时钟 |

|---|---|---|---|---|---|

| 1 | 设置预分频时钟源 | CCM->CBCMR | PRE_PERIPH_CLK_SEL | 选择预分频时钟源 | - |

| 2 | 选择外设时钟源 | CCM->CBCDR | PERIPH_CLK_SEL | 选择外设时钟源 | - |

| 3 | 设置AHB分频 | CCM->CBCDR | AHB_PODF | 设置AHB总线分频 | 132MHz |

5.IPG_CLK_ROOT配置(66MHz)

| 步骤 | 操作 | 寄存器 | 位域 | 配置说明 | 目标时钟 |

|---|---|---|---|---|---|

| 1 | 设置IPG分频 | CCM->CBCDR | IPG_PODF | 从AHB时钟分频 | 66MHz |

6.PERCLK_CLK_ROOT配置(66MHz)

| 步骤 | 操作 | 寄存器 | 位域 | 配置说明 | 目标时钟 |

|---|---|---|---|---|---|

| 1 | 选择外设时钟源 | CCM->CSCMR1 | PERCLK_CLK_SEL | 选择外设时钟源 | - |

| 2 | 设置外设分频 | CCM->CSCMR1 | PERCLK_PODF | 设置外设时钟分频 | 66MHz |