程序固化实验

MPSOC启动概述

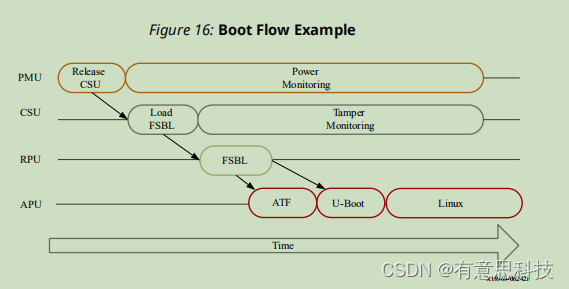

a)MPSOC的系统启动过程由平台管理单元(Platform Management Unit,PMU)和配置安全单元(Configuration Security Unit,CSU)管理和执行。启动过程包括三个功能阶段:预配置阶段、配置阶段、后配置阶段。

b)预配置阶段由平台管理单元PMU控制。

1)平台管理单元运行PMU ROM代码以设置系统。PMU处理所有复位和唤醒过程。这是启动的第一阶段,完全由PMU控制,从上电复位POR开始,到释放CSU复位结束。当芯片检测到稳定电源输入时,上电复位信号将PMU从复位状态唤醒,这是整个系统启动的起点。PMU立即开始执行内部固化的PMU ROM代码,此时PMU工作在SysOsc时钟(180MHz±15%) 下,这是芯片内部最基础的时钟源。

2)PMU ROM执行一系列关键操作,为后续系统启动建立基础环境:

①寄存器清零:复位LPD(低压域)、FPD(全电源域)所有寄存器、PMU RAM、PMU处理器TLB内存。消除上电前残留状态,确保初始化一致性;

②电压检测:通过SYSMON(系统监控器)检查LPD、AUX、专用IO等关键区域电压。确保电源稳定,防止硬件损坏;

③时钟初始化:启动必需的PLL,生成稳定的系统时钟。为后续模块提供可靠时钟源;

④内存复位:复位CSU、LPD、FPD的内存区域,初始化OCM(片上内存)。为引导程序准备干净的内存环境;

⑤模块初始化:初始化SYSMON、GPIO、必要的外设控制器;

⑥复位管理:保持CSU、APU、RPU等核心模块复位状态,仅初始化必要组件。确保按顺序启动,避免冲突。

3)预配置阶段的终点是PMU释放CSU复位信号,这标志着控制权从PMU向CSU的转移:

①PMU完成所有初始化后,通过特定寄存器操作解除CSU的复位状态;

②PMU进入PMU服务器模式 (PMU Server Mode),转为后台运行,负责监控系统电源状态、处理电源管理请求;

③CSU从复位中唤醒,开始执行自身的CSU BootROM代码,启动配置阶段。

c)配置阶段:CSU的引导与安全核心

1)在配置阶段,BootROM(CSU ROM代码的一部分)解释引导头以配置系统,并在安全或非安全引导模式下将处理系统(PS)的第一阶段引导加载程序(FSBL)代码加载到片上RAM(OCM)中。引导头定义了许多引导参数,包括安全模式和执行FSBL的处理器MPCore。在引导期间,CSU还将PMU用户固件PMU FW加载到PMU RAM中,以与PMU ROM一起提供平台管理服务。对于基于Xilinx的FSBL和系统软件,PMU FW必须存在于大多数系统中。配置阶段由CSU主导,核心任务是加载并验证启动镜像,并将控制权转移给FSBL(第一阶段引导加载程序)。2)CSU BootROM初始化与启动模式检测:

①CSU BootROM启动:CSU复位释放后,立即执行内部固化的CSU BootROM代码,这是系统的硬件信任根 (Root of Trust);

②启动模式识别:CSU读取芯片上的MODE引脚(通常为MODE[3:0]),确定系统的启动设备 (如SD卡、QSPI Flash、eMMC、USB等);

③黄金镜像搜索:激活Golden Image Search机制,在指定启动设备上查找有效的启动镜像 (通常为BOOT.BIN),支持镜像冗余和故障转移。

3)CSU BootROM解析启动镜像的引导头 (Boot Header),并根据启动模式 (安全 / 非安全) 执行不同操作。引导镜像解析与安全验证 (核心流程):

①非安全启动流程

i)从启动设备读取引导镜像到OCM;

ii)解析引导头,获取镜像分区信息 (FSBL、PMU 固件、ATF 等);

iii)提取并加载PMU固件 (PMUFW)到PMU RAM,PMU从ROM模式切换到固件模式,增强电源管理能力;

iv)提取FSBL到OCM,释放指定处理器 (通常为RPU或APU0) 复位,跳转到FSBL入口地址执行。

②安全启动流程 (核心安全保障):安全启动模式下,CSU BootROM执行严格的硬件级安全验证,这是Xilinx MPSoC安全架构的核心。

i)PPK完整性检查:验证主公共密钥 (Primary Public Key) 的完整性,确保密钥未被篡改。建立信任链起点,防止密钥注入攻击;

ii)密钥撤销检查:检查PPK/SPK (二级公共密钥)是否在撤销列表中,支持密钥更新和漏洞修复,应对密钥泄露风险;

iii)PUF使用:若启用PUF (物理不可克隆函数),验证PUF数据并生成设备唯一密钥,提供硬件级唯一身份标识,防止克隆和伪造;

iv)镜像认证:使用SPK验证引导镜像的数字签名,确保镜像完整性和来源合法性。防止恶意代码注入,保障启动代码可信;

v)分区解密:对加密的镜像分区使用设备唯一密钥进行解密。

4)CSU与PMU的二次交互:配置阶段中,CSU会将PMU固件加载到PMU RAM,这是关键的交互步骤:

①CSU从启动镜像中提取PMU固件分区;

②通过内部总线将固件传输到PMU RAM (地址范围:0xFFD00000-0xFFD0FFFF);

③发送信号通知PMU切换到固件模式,PMU开始执行PMU固件,获得更强大的电源管理和系统控制能力;

④PMU固件与CSU、FSBL建立通信通道,为后续系统组件上电和初始化提供支持。

d)后配置阶段:协同完成系统启动

1)FSBL执行开始后,CSU ROM代码进入后配置阶段,该阶段负责系统干预响应。CSU硬件提供持续的硬件支持,以验证文件,通过PCAP配置PL,存储和管理安全密钥,解密文件。后配置阶段是启动的最后阶段,由FSBL主导,PMU和CSU提供支持,完成整个系统的初始化。

2)FSBL的核心操作 (依赖PMU/CSU支持)

①硬件初始化:初始化DDR控制器、MIO/EMIO引脚、外设等,这些操作需要PMU提供电源管理支持;

②PL配置:若启动镜像包含PL比特流,FSBL将其加载到FPGA结构中,完成硬件配置;

③加载后续引导程序:加载ATF (ARM Trusted Firmware)、U-Boot等,建立完整的软件信任链;

④系统控制权转移:最终将控制权转移给操作系统 (如Linux) 或用户应用程序。

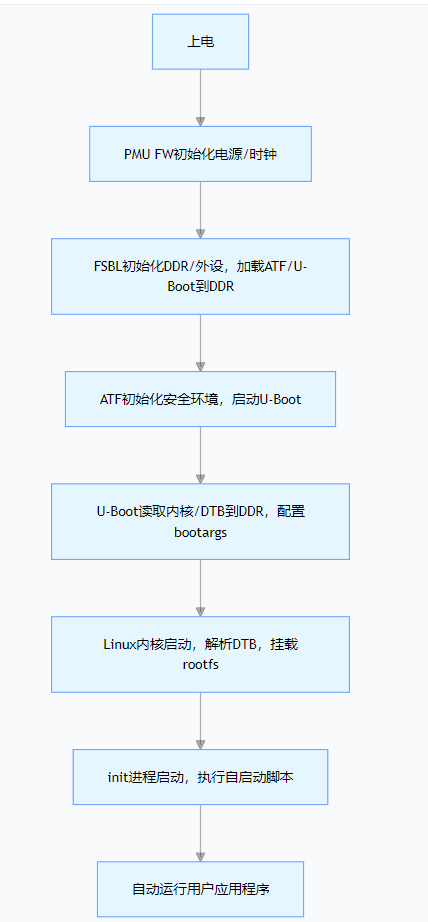

e)启动流程

1)PMU执行许多强制性和可选的安全操作,包括:

①可选功能:将低功耗域(LPD)寄存器归零。当LPD_SC eFUSEs编程时,PMU将LPD中所有寄存器归零;

②可选功能:将全功率域(FPD)寄存器归零。当FPD_SC eFUSEs编程时,PMU将FPD中所有寄存器归零;

③将PMU RAM归零:PMU RAM中写零并读回以确认写成功;

④将PMU处理器的TLB内存归零;

⑤电压检查:PMU检查LPD、AUX、专用IO的电源电压,以确认电压在规格范围内;

⑥将内存归零:PMU将位于LPD、FPD、CSU中的内存归零。

2)一旦这些安全操作完成,PMU通过SHA-3/384引擎发送CSU不可变ROM代码,并将计算出的加密校验和与存储在设备中的黄金拷贝(golden copy)进行比较,如果校验和匹配,则验证CSU ROM完整性并释放对CSU的复位。

3)PMU负责处理主要的预引导任务和PS的管理,以确保系统资源的可靠通电断电。启动PMU的上电复位(POR)操作,直接或间接的释放了预期上电模块的复位。在这种情况下,PMU需要ROM代码来保持初始化上电顺序。即使在启动过程之后,PMU仍在运行,并且负责处理各种系统复位。在更改系统电源状态时,也会使用它(例如上电、睡眠和唤醒)。

4)在初始化启动期间,POR将PMU从复位中释放,然后执行PMU ROM。下面描述了PMU处理器在POR复位后,通过运行PMU ROM预启动代码完成的操作序列:

①初始化PS SYSMON和引导单元所需的PLL;

②清除PMU RAM和CSU RAM(仅外部POR);

③验证PLL锁;

④通过PS SYSMON单元验证LPD、AUX、IO电源范围;

⑤清除低功耗和全功耗域;

⑥如果前面的步骤没有错,PMU将释放CSU复位并进入PMU服务模式。如果有错,将产生一个启动错误标志。

5)当CSU复位被释放,CSU将按照下面序列运行:

①初始化OCM;

②通过读取引导模式寄存器来确定启动模式;

③CSU继续在OCM中加载FSBL,以供RPU或APU执行。然后,CSU将PMU用户固件加载到PMU RAM中,以供PMU固件执行。

f)启动模式(Boot Modes)

1)BootROM可以通过Quad-SPI,SD,eMMC,USB2.0控制器0、NAND等外部设备启动系统。

2)MPSOC使用多个模式引脚来决定配置器件的类型,软件的存储位置以及其他的系统设置,这些引脚共享PS端的MIO引脚。总共有7个模式引脚,分别为MIO[8:2]。其中,前四个引脚定义启动模式,第五个引脚定义是否使用PLL,第六个和第七个引脚定义上电过程中MIO bank0和bank1的bank电压。

→

补充

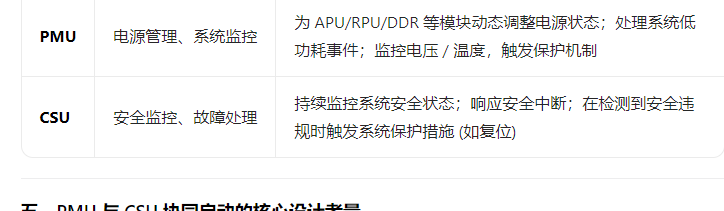

1.PMU负责电源管理、复位控制、系统初始化、释放CSU复位。其通过专用microblaze处理器、PMU ROM、PMU RAM实现。PMU最先上电运行、控制所有电源域、处理系统唤醒。

2.CSU负责启动模式检测、引导镜像加载、安全验证、加载FSBL/PMU固件。其通过专用处理器、CSU BootROM、硬件安全引擎实现。CSU是硬件信任根、负责安全启动所有验证、控制引导流程。

3.上电 → POR复位 → PMU唤醒 → PMU ROM执行 → 初始化系统 → 释放CSU复位 → CSU BootROM执行 → 检测启动模式 → 加载并验证启动镜像 → 加载PMU固件 → 加载FSBL → 释放处理器复位 → FSBL执行 → 初始化DDR/PL → 加载ATF/U-Boot → 启动OS

FPGA启动概述

a)Xilinx传统FPGA的启动流程与MPSoC有本质差异:传统FPGA没有独立的PMU和CSU专用处理器,启动过程由硬件配置逻辑 (Configuration Logic) 和启动序列控制器 (Start-up Controller) 主导,无需处理器参与即可完成配置;而MPSoC的启动则依赖PMU和CSU双核心单元协同,涉及复杂的处理器初始化与安全验证。

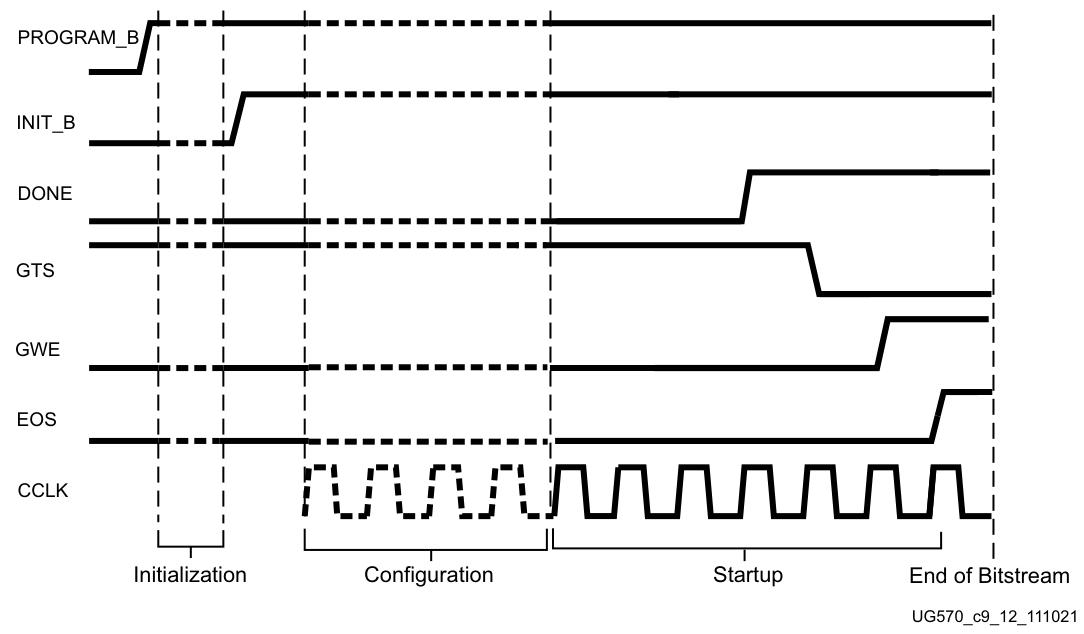

b)传统FPGA的启动流程分为上电复位 (POR)→配置初始化→比特流加载→全局校验与启动序列锁存→启动序列,全程由硬件自动执行,无需任何处理器介入。

c)阶段1:上电复位 (Power-On Reset) 与初始化准备:这是启动的起点,确保FPGA硬件处于安全初始状态。

1)电源上电时序:严格遵循VCCINT(核心电压)先于VCCO(I/O电压)的上电顺序,两者压差时间需控制在1秒内,防止I/O损坏;

2)POR信号生成:芯片内部电源监控电路检测到稳定电压后,生成上电复位POR信号,复位所有配置逻辑和用户逻辑;

3)PROG_B信号处理:若外部PROG_B引脚被拉低,FPGA会强制重启配置过程,清除所有配置SRAM;

4)INIT_B信号控制:INIT_B引脚被拉低表示FPGA正在初始化,拉高则表示准备就绪可接收配置数据。

d)阶段2:配置阶段(Configuration Phase)核心数据加载。

1)清除配置SRAM:①启动序列控制器自动发起全芯片配置SRAM清零操作,消除上电前的随机状态;②清零完成后,INIT_B引脚被拉高,向外部系统发出准备就绪信号。

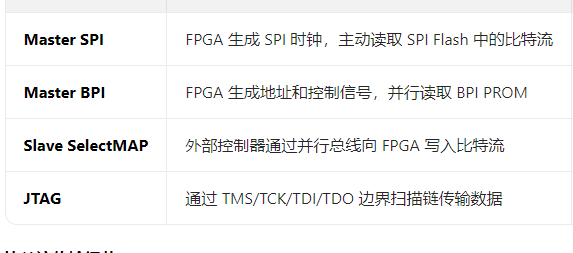

2)比特流加载与传输:根据选定的配置模式,FPGA执行不同的数据获取方式。

比特流传输细节:数据以帧格式传输,每帧包含CRC校验位;配置逻辑实时执行CRC校验,若出错则拉低INIT_B引脚,中断配置过程;高端器件(如UltraScale+)支持增量配置和部分重配置PR,仅更新指定区域逻辑。

3)配置数据校验:配置完成后,FPGA执行全局CRC校验,验证整个配置SRAM的数据完整性;校验通过则进入启动序列阶段,失败则保持INIT_B低电平,等待重新配置。

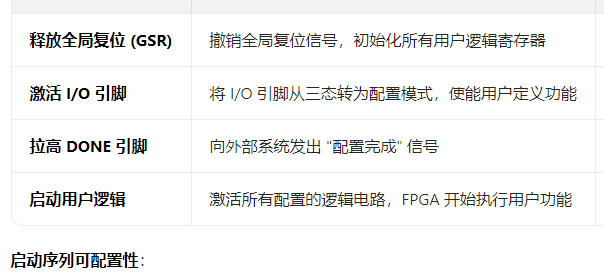

e)阶段3:启动序列 (Start-up Sequence)激活用户逻辑。

通过BitGen工具设置参数,可调整启动序列顺序,例如:先激活I/O再释放GSR;延迟DONE信号拉高时间;启用多启动Multiboot功能,支持故障转移和镜像冗余。配置逻辑从比特流中提取启动序列参数(如GSR释放延迟、I/O配置顺序、多启动镜像地址),写入启动序列控制器的专用寄存器。

→补充

上电 → 电源稳定 → POR复位 → 清除配置SRAM → INIT_B拉高 → 加载比特流(含CRC校验) → 全局CRC校验 → 启动序列(GSR释放→I/O激活→DONE拉高) → 用户逻辑运行

f)安全配置机制

1)Virtex UltraScale+、Kintex UltraScale +等高端FPGA支持比特流加密与认证,防止IP窃取与恶意篡改,其核心是硬件集成的AES-256引擎与ECC-384认证引擎,启动流程新增安全验证阶段:

①密钥加载:上电后,硬件从OTP(一次性可编程)存储器读取加密密钥(用户烧写),密钥不可读取,仅可在硬件内部使用;

②比特流解密:从Flash读取的加密.bin文件,由AES引擎实时解密为明文帧数据,再写入配置SRAM;

③比特流认证:解密完成后,ECC引擎验证比特流的数字签名,确保比特流由合法工具生成,未被篡改;

④安全失败处理:解密 / 认证失败时,FPGA不会激活用户逻辑,DONE引脚保持低电平,且无法通过PROG_B引脚复位,仅可通过JTAG重新烧写合法比特流。

2)多启动 (Multiboot) 机制:故障自动恢复。Multiboot是Xilinx FPGA的高可靠性特性,支持在Flash中存储多个配置镜像,启动失败时自动切换到备用镜像,流程如下:

①镜像存储结构:Flash中划分多个镜像分区,每个分区存储一个完整的.bin文件,分区地址由比特流参数配置;

②主镜像启动:FPGA优先加载主镜像分区的.bin文件,执行正常启动流程。若主镜像启动失败(如CRC校验错误、DONE引脚超时),启动序列控制器自动触发镜像切换;

③备用镜像加载:FPGA读取下一个备用镜像分区的.bin文件,重新执行启动流程,直至启动成功或所有镜像尝试完毕。

3)

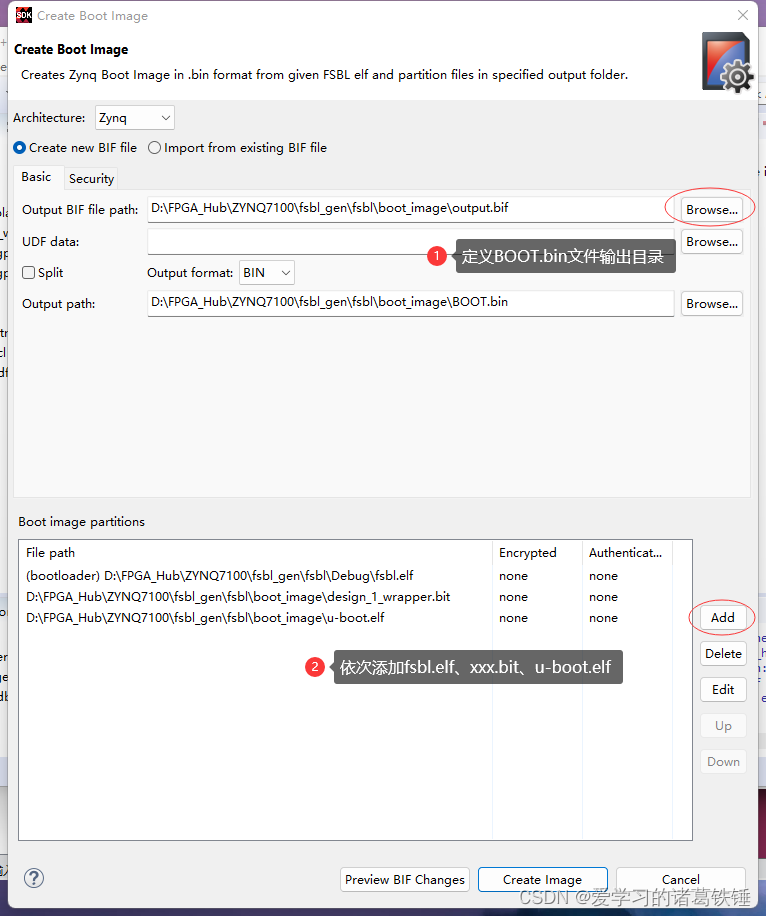

生成镜像

a)

1)首先是bootloader启动文件,即fsbl.elf文件;其次是FPGA的配置.bit文件;最后是应用程序。这三个文件的顺序不能出错。

b)核心启动文件列表

1)PMU Firmware(pmufw.elf)

①电源管理单元PMU初始化阶段(上电第一个执行的固件)。MPSoC的PMU是独立于PS/PL的微控制器,上电后首先执行PMU FW,是整个系统的电源管家。其主要功能有:

i)初始化PS的核心电源域(如CPU、DDR、IO的电源),配置电压和电源策略;

ii)初始化系统时钟(如PLL、时钟分频),确保硬件时钟稳定;

iii)管理复位逻辑,释放PS核心的复位信号,为后续FSBL执行提供基础硬件环境;

iv)支持低功耗模式配置(如休眠、唤醒),是系统稳定运行的前提。

②PMU FW由Xilinx官方提供,需匹配具体MPSoC型号,用户无需修改,只需在打包BOOT.BIN时集成。

2)FSBL(First Stage Boot Loader,fsbl.elf)

①第一阶段启动加载(PS端核心初始化)。FSBL是用户可定制的第一个启动程序,也是连接PMU和上层系统的关键。其主要功能有:

i)初始化PS的核心外设:DDR(关键!将后续镜像加载到内存)、UART(调试输出)、SPI/eMMC/SD(存储介质);

ii)加载并验证后续镜像(ATF、U-Boot,可选PL bitstream)到DDR指定地址;

iii)配置PL:如果包含PL比特流,FSBL会将其下载到PL并初始化;

iv)传递启动参数(如DDR大小、启动介质)给下一阶段(ATF);

v)处理启动模式:识别硬件配置的启动介质(QSPI、SD、eMMC、JTAG),并从对应介质读取镜像。

②FSBL通过Xilinx Vitis/SDK工具生成,基于官方模板,用户可修改初始化逻辑(如自定义DDR时序、添加硬件检测)。

3)ATF(ARM Trusted Firmware,bl31.elf)

①安全固件初始化(ARM TrustZone架构要求)。ATF运行在ARMv8架构的EL3(最高异常级别),是安全隔离层,负责安全世界与非安全世界的隔离。其主要功能有:

i)初始化ARMv8的异常级别(EL1/EL2/EL3),配置MMU(内存管理单元);

ii)管理GIC(通用中断控制器)的安全中断,处理安全监控调用(SMC);

iii)验证并启动下一阶段的U-Boot(运行在EL2/EL1);

iv)支持安全启动(Secure Boot):验证后续镜像的签名,防止恶意篡改;

v)提供基础安全服务(如加密、认证)。

②ATF由Xilinx定制适配MPSoC,用户一般无需修改,只需正确集成到BOOT.BIN中。

4)U-Boot(u-boot.elf / u-boot.ub)

①第二阶段启动加载(SSBL)。U-Boot是连接FSBL和Linux内核的桥梁,也是用户配置自启动逻辑的关键。其主要功能有:

i)进一步初始化外设:网络(Ethernet)、USB、存储设备(eMMC/SD)等;

ii)从存储介质读取Linux内核、DTB、根文件系统到DDR;

iii)配置启动参数(bootargs):向内核传递根文件系统路径、串口波特率、DDR大小等关键参数;

iv)支持命令行交互(调试用),也可配置为无交互自动启动;

v)核心自启动配置:通过bootcmd环境变量定义自动启动命令(如run bootcmd_mmc0表示从SD卡启动内核)。

②u-boot.ub是压缩后的U-Boot镜像(包含设备树片段),比u-boot.elf更常用。用户需修改U-Boot环境变量(如固化bootcmd)实现无人值守启动。

5)Device Tree Blob(DTB,system.dtb)

①Linux内核启动阶段。DTB是描述硬件拓扑的二进制文件,替代传统的硬编码硬件信息,是内核识别硬件的关键。其主要功能有:

i)向Linux内核提供硬件信息:CPU核数、DDR地址 / 大小、UART/I2C/SPI的基地址 / 中断号 / 时钟;

ii)描述PL自定义外设:如果PL中有用户逻辑(如FPGA IP),需在DTB中添加对应的节点(地址、中断、驱动匹配);

iii)传递硬件参数:如串口波特率、SD卡控制器型号、网络MAC地址;

iv)内核启动时动态解析DTB,无需修改内核源码即可适配不同硬件配置。

②DTB由设备树源文件(DTS)通过dtc工具编译生成,用户需根据实际硬件修改DTS(如PL外设节点)。

6)Linux Kernel(Image / zImage)

①Linux内核启动阶段。内核是操作系统的核心,负责管理所有系统资源,是应用运行的基础。其主要功能有:

i)初始化系统核心组件:进程调度器、内存管理、文件系统驱动、外设驱动;

ii)解析DTB并初始化硬件驱动(如SD卡、eMMC、网络、UART);

iii)挂载根文件系统(rootfs),启动用户空间的第一个进程(init进程);

iv)提供系统调用接口,为应用程序提供硬件访问能力(如读写文件、控制外设)。

②MPSoC(ARMv8)通常使用Image(未压缩内核),zImage是压缩版;用户需编译内核并启用所需驱动(如SD/eMMC、PL外设驱动)。

7)Root File System(rootfs,如 rootfs.img/initramfs.cpio.gz)

①用户空间启动阶段。rootfs是Linux用户空间的根目录,包含所有用户态程序和配置,是应用自启动的载体。其主要功能有:

i)提供内核挂载的根目录(/),包含系统库(libc、libstdc++)、工具(busybox)、配置文件;

ii)包含init进程(如systemd、busybox init):内核启动后第一个运行的用户态进程,负责启动其他服务;

iii)存储用户应用程序(如app.elf)及其依赖库;

iv)支持应用自启动配置:通过/etc/rc.local、systemd服务、/etc/inittab等脚本自动启动应用。

②常用格式:ext4(SD/eMMC等块设备)、cpio.gz(initramfs,内存中运行);静态链接的应用无需依赖外部库,更适合嵌入式自启动。

8)BOOT.BIN(启动镜像包)

①整合所有底层启动文件。BOOT.BIN是由bootgen工具打包生成的单一镜像文件,整合了PMU FW、FSBL、ATF、U-Boot(可选PL bitstream),是MPSoC启动的入口文件。其主要功能有:

i)简化启动流程:将多个底层固件整合为一个文件,便于从SD/QSPI/eMMC读取;

ii)包含镜像校验和:支持安全启动(Secure Boot),防止镜像被篡改;

iii)定义启动顺序:严格按照PMU FW → FSBL → ATF → U-Boot的顺序执行;

iv)适配启动介质:MPSoC上电后会从配置的启动介质(如SD卡)读取BOOT.BIN并执行。

②生成BOOT.BIN时需提供bootgen.bif文件(镜像描述文件),指定各文件的路径和执行顺序。

9)用户应用程序(如 app.elf/app.bin)

①应用自启动阶段。其主要功能有:

i)实现具体业务逻辑:如数据采集、外设控制、网络通信、PL逻辑交互;

ii)依赖rootfs中的库和配置,由init进程或启动脚本自动启动;

iii)可编译为静态链接(独立运行)或动态链接(依赖libc等库)。

②自启动配置示例:在/etc/rc.local中添加/usr/bin/app.elf &(后台运行应用)。

③

基于TCP协议的远程更新QSPI Flash实验

a)远程更新QSPI Flash就是将BOOT.bin文件通过网络协议如常用的TCP、UDP协议传给远端联网的文件接收端即MPSOC开发板。接收端将文件暂存在DDR中,当文件传输完成后,接收端接收到更新命令后将调用相关函数将文件数据写入到QSPI Flash中,写入完成后为了防止写入出错,需要将写入到Flash中的数据读出以进行校验。校验成功后就可以重新以QSPI Flash启动的方式启动,完成远程更新。

b)从上述可以看出,接收端的MPSOC开发板作为服务端,发送端作为客户端将BOOT.bin文件数据上传给服务端是一个较好的客户/服务器模型。有一个特别需要注意的地方是,当客户端上传完文件后,作为服务端的MPSOC开发板如何知道文件传输完成并启动更新呢。

→

有两种方式可以解决。一是客户端传输完成后,关闭连接,服务端知道客户端关闭连接后知道文件传输完成,更新QSPI Flash。此种方式弊端很多,如不能知道后续的更新情况,若发生写入到QSPI错误,不能及时修复,以及不能避免因环境问题导致的网络误关闭。另一种是当客户端传输文件完成后,向服务端发送更新命令,服务端接收到更新命令后启动更新。为了防止传错文件等意外情况,也可以添加清除命令,使之前传送的数据无效。

c)由于TCP协议的稳定可靠,本章我们选择TCP协议作为网络传输协议。MPSOC开发板利用lwip协议栈开启TCP服务作为服务端,可以写一个TCP客户端的上位机或使用网络调试助手开启TCP客户端传送BOOT.bin文件。

d)本章的实验任务是使用LWIP协议栈的tcp协议实现远程更新QSPI Flash的功能,当输入"update"命令时更新QSPI并反馈信息,当输入"clear"命令时之前传输的数据无效,当输入"erase"命令时对Flash进行擦除,如果此时Flash中有程序则会被擦除掉。

Xilinx 7系列高级配置主题

配置文件数据格式

a)在AMD ISE工具中,BitGen可将布局布线后的NCD文件转换为配置文件或比特流。PROM文件生成器PROMGen则可将一个或多个比特流文件转换为PROM文件。在AMD Vivado中,等效的Tcl命令为WRITE_BITSTREAM和WRITE_CFGMEM。PROM文件可生成多种格式,且不一定非要用于PROM器件;它们可存储在任何位置并通过任何方式传输。

b)文件区别

1)BIT:二进制,没有比特交换。设计工具默认输出,包含Xilinx/AMD工具可识别的头部信息(如器件型号、日期等)。用于直接通过JTAG电缆对FPGA进行配置、调试。用于Vivado/ISE中直接下载到FPGA,工程调试阶段。

2)RBT:ASCII文件,没有比特交换。BIT文件的ASCII文本形式。内容为可读的0和1。文件体积巨大(膨胀约8倍),主要用于极少数情况的调试或查看。需要肉眼查看或分析比特流内容的特殊调试场合。

3)BIN:二进制,没有比特交换。纯二进制数据流,无任何头部信息。是配置数据的原始镜像。用于嵌入式处理器(如MicroBlaze、ARM)通过SelectMAP或并行接口加载FPGA,或用于某些第三方编程工具。由微处理器控制FPGA配置的系统,自定义配置解决方案。

4)MCS:ASCII文件,通常比特交换。行业标准的PROM/Flash编程文件格式。包含地址、数据、校验和。专用于通过编程器烧录到外部非易失存储器(如SPI Flash、BPI NOR Flash)中。用于生产烧录,用于FPGA上电自动从Flash加载(Master模式)。

5)HEX:ASCII文件,用户指定比特交换。另一种常见的存储器编程格式,仅包含地址和数据,比MCS更简洁。也用于将配置数据嵌入到其他系统(如微控制器固件)中。需要将配置数据集成到其他固件或特定编程环境中的情况。

→

6)总结

①用Vivado/ISE通过JTAG下载调试 -> 直接用.bit文件;

②生成文件给嵌入式处理器加载 -> 生成.bin文件;

③要烧录到SPI Flash或并行NOR Flash让FPGA上电自加载 -> 生成.mcs文件(或相应格式);

④需要查看比特流内容 -> 生成.rbt文件(很少用);

⑤使用第三方或特定编程环境 -> 根据其要求选择.hex或其他格式。

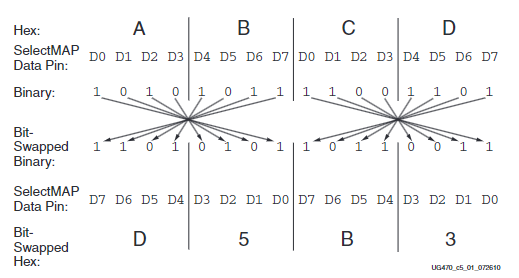

c)FPGA并行数据总线(如SelectMAP)的位序(D0为MSB)与常见微处理器/存储器的字节序可能不一致。比特交换功能可以反转每个字节内的比特顺序,以匹配目标系统的预期格式。MCS文件默认进行比特交换,因为它主要用于与Flash器件对接。而直接给FPGA的BIT/BIN文件不交换。

d)BIT文件有头部:包含让Vivado/iMPACT工具识别和验证的信息,下载前工具会检查头部中的器件ID是否与目标FPGA匹配。BIN文件无头部:是裸数据,因此由处理器加载时,需要确保加载逻辑与FPGA的配置时序严格匹配。

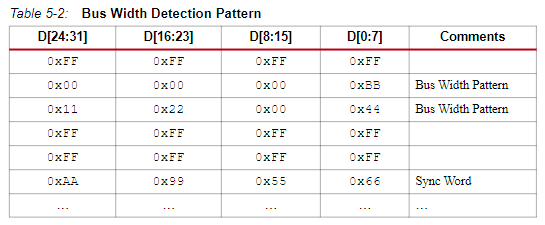

e)总线宽度自动检测

1)总线宽度自动检测模式被插入到每个比特流的起始位置。该模式用于并行配置模式中,以自动检测配置总线宽度。由于它出现在同步字之前,串行配置模式会忽略此模式。

2)对于并行配置模式(如SelectMAP、BPI),总线宽度由配置逻辑自动检测。一个总线宽度检测模式被放置在比特流的前端。配置逻辑仅检查并行总线的低8位(D[0:7])。根据接收到的字节序列,配置逻辑可以自动切换到相应的外部总线宽度。

f)同步字

1)一个特殊的同步字用于使配置逻辑在32位字边界上对齐。在找到同步字之前,FPGA不会处理任何数据包。对于并行配置模式,必须先成功检测到总线宽度,才能检测同步字。

生成存储器文件

a)PROM文件可通过ISE Design Suite中的PROMGen工具,或Vivado Design Suite中的Tcl命令WRITE_CFGMEM,由比特流文件生成。用户可直接从命令行访问PROMGen,或通过iMPACT的文件生成模式间接使用。PROM文件的作用是将比特流文件重新格式化以用于 PROM编程,并为串行菊花链组合多个比特流文件

b)用于串行菊花链的PROM文件

1)串行菊花链的配置数据需要特殊的格式化处理,因为独立的BIT文件不能简单地拼接在一起来对菊花链进行编程。这种特殊的格式化是在从多个比特流生成PROM文件时,由PROMGen(或iMPACT)完成的。要生成PROM文件,可使用PROMGen的-n、-u、-d选项或iMPACT的文件生成向导来指定多个比特流。对于WRITE_CFGMEM Tcl命令,使用参数-loadbit "up|down <bitfile1.bit> <bitfile2.bit>"。

2)PROMGen通过将下游器件的配置数据嵌套到上游器件的配置数据包中,来重新格式化配置比特流。若尝试通过向第一个器件发送多个独立的比特流来对菊花链编程,将导致第一个器件配置完成后忽略后续的数据。

c)用于SelectMAP配置的PROM文件

1)MCS文件格式最常用于对AMD配置PROM进行编程,这些PROM进而以SelectMAP模式对单个FPGA进行编程。对于定制的配置解决方案,BIN和HEX文件因其原始数据格式而成为最容易使用的PROM文件格式。某些情况下可能需要额外的格式化。

2)如果用于SelectMAP配置的多个配置比特流位于同一个存储器件中,则不能将这些比特流合并成一个用于串行菊花链的PROM文件。相反,应使用多个BIN或HEX文件对目标存储器件进行编程。如果需要生成一个包含多个独立数据流的单一PROM文件,可以在iMPACT中通过选择并行PROM为目标,然后选择适当数量的数据流来实现。这也可以通过PROMGen命令行完成。

d)用于SPI/BPI配置的PROM文件

1)PROMGen中的-d、-u选项、iMPACT文件生成向导或write_cfgmem -loadbit参数,可用于为第三方闪存器件创建PROM文件。应选择您的第三方编程器支持的输出格式。某些BPI器件在编程PROM文件时,需要启用字节序交换。请参考闪存供应商的文档。

e)比特交换

1)比特交换是指交换一个字节内的各个比特。除非使用用于SPI配置模式的PROMGen -spi选项或write_cfgmem -interface spi1|spi2|spi4选项,否则MCS格式的PROM文件总是进行比特交换的。HEX文件格式可以根据用户选项选择是否进行比特交换。而比特流文件(BIT、RBT、BIN)从不进行比特交换。

2)HEX文件格式仅包含配置数据。其他PROM文件格式则包含不应发送给FPGA的地址和校验和信息。这些地址和校验和信息被一些第三方器件编程器使用,但不会被编程到PROM本身中。

3)

f)并行总线位序

1)传统上,在SelectMAP x8模式中,每个CCLK时钟周期加载一个字节的配置数据,且每个字节的最高有效位MSB被送至D0引脚。尽管这一约定(D0 = MSB,D7 = LSB)与许多其他器件不同,但在所有AMD FPGA中是一致的。在7系列器件中,此比特交换规则被扩展到x16和x32总线宽度,即数据在每个字节内部进行比特交换。

g)延迟配置

1)要延迟配置,应在初始化期间将INIT_B引脚保持为低电平。当INIT_B变为高电平后,再试图将其拉低将无法延迟配置。

2)INIT_B:输入、输出、开漏。可通过INIT_B引脚外部访问。从上电复位或PROGRAM_B复位开始,INIT_B被驱动为低电平,表示FPGA正在初始化清除其配置存储器。在模式引脚被采样之前,INIT_B是一个输入引脚,可将其保持为低电平以延迟配置。在模式引脚被采样之后,INIT_B是一个低电平有效的开漏输出引脚,用于指示配置期间是否发生CRC错误,或配置后(当启用时)是否发生回读CRC错误。

3)INIT_COMPLETE:内部信号,可通过7系列FPGA状态寄存器访问,指示INIT_B信号是否已在内部释放。

配置序列

a)

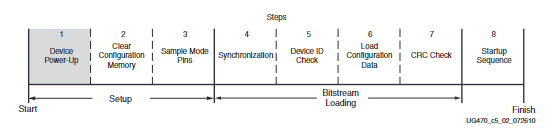

1)设置(步骤1-3)包括:设备上电、清除配置存储器和采样模式引脚。

①设备上电(步骤1):对于配置操作,7系列器件需要在VCCO_0、VCCAUX、VCCBRAM、VCCINT引脚上供电。电源时序要求在相应的i)7系列FPGA数据手册中有描述。所有JTAG配置引脚都位于一个独立的专用I/O组Bank0中,拥有专用的电源电压VCCO_0。多功能引脚位于Bank14、Bank15。所有专用输入引脚在VCCO_0的LVCMOS电平下工作。所有活动的专用输出引脚在VCCO_0电压下工作,输出标准设置为LVCMOS,驱动强度12mA,转换速率设置为快速。如果使用了Persist选项,所选配置模式下的双模式I/O在配置完成后将保持活动状态,其I/O标准设置为LVCMOS,驱动强度12mA,转换速率设置为慢速。

ii)对于所有使用多功能I/O的模式,必须将相关的VCCO_14或VCCO_15连接到合适的电压,以匹配配置器件的I/O标准。在配置期间,这些引脚也工作于LVCMOS,驱动强度12mA,转换速率快速。

iii)在上电时,必须为 VCCINT电源引脚提供1.0V或0.9V(适用于-2L等级)的电源。在JTAG模式下进行7系列FPGA配置时,除了VCCO_0之外,不需要为任何其他I/O电压电源供电。当选择使用多功能引脚的配置模式时(即串行、主BPI、SPI、SelectMAP模式),则必须同时为VCCO_14、VCCO_15或两者供电。

iv)

→辅助电压的辅助指不属于核心逻辑电压,也不属于通用IO电压,只给特殊功能模块供电。它们支持FPGA的高级特性和高性能模块,是现代FPGA采用混合工艺和电压域隔离设计思想的体现。VCCAUX主要为对电源噪声敏感或需要与核心逻辑不同电压的高性能数字模块供电,将其与核心逻辑电源VCCINT(1.0V/0.9V)隔离,可以防止数字开关噪声干扰这些敏感电路。其主要供电对象为:配置逻辑与比特流解密单元、时钟管理单元、高速串行收发器、BRAM的预充电电路、全局缓冲器和分布网络、专用配置引脚。VCCAUX_IO几乎专门为FPGA内部的模拟电路模块供电,最核心的就是XADC。XADC是7系列FPGA内部集成的模数转换器系统,它的模拟部分(采样保持、比较器、基准电压源等)对电源噪声的敏感度达到了极致,必须使用一个完全独立的、极其干净的模拟电源 VCCAUX_IO,以与数字电源 VCCAUX和 VCCINT上的开关噪声进行物理隔离,否则转换精度会严重下降。

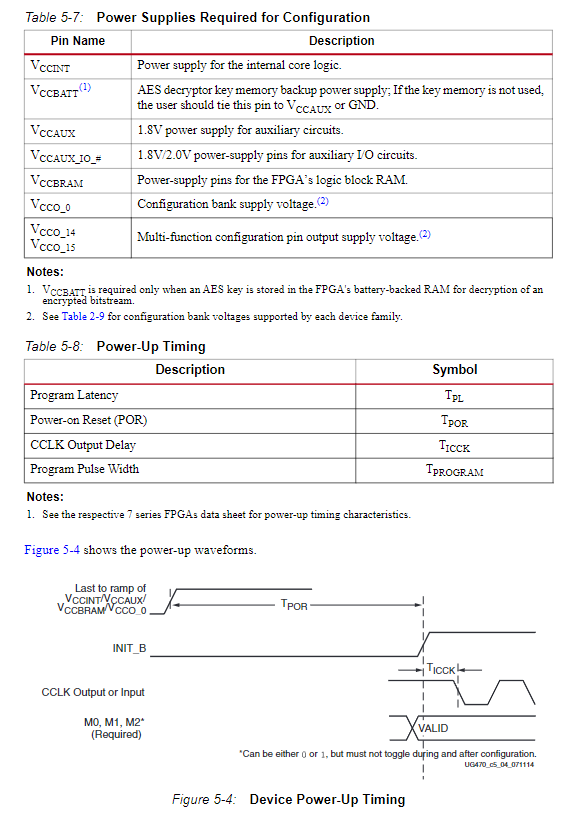

v)为确保器件上电后正常工作,必须遵循相应7系列FPGA数据手册中的指导规范。电源应在数据手册规定的电源上升时间范围内单调上升,所有供电电压需处于推荐工作范围内。若VCCINT电压低于VDRINT(核心逻辑最小供电电压)或VCCAUX电压低于VDRI(辅助电路最小供电电压)(具体数值见对应7系列FPGA数据手册),可能导致配置数据丢失。

→

若无法实现电源单调上升,可在系统电源达到VCC0、VCCAUX、VCCBRAM、VCCINT的最小推荐工作电压前,将INIT_B引脚保持低电平以延迟配置启动。部分配置模式会涉及bank14/15或两者皆涉及,当这些bank参与配置时,其对应的供电电压必须在INIT_B引脚释放为高电平前,达到最小推荐工作电压。

vi)

tPL:PROGRAM_B引脚恢复高电平后,INIT_B引脚开始从低电平释放为高电平的延迟时间;

TICCK:CCLK输出延迟。INIT_B引脚变为高电平后,CCLK开始输出或接收输入的延迟时间。

②清空配置存储器(步骤2)

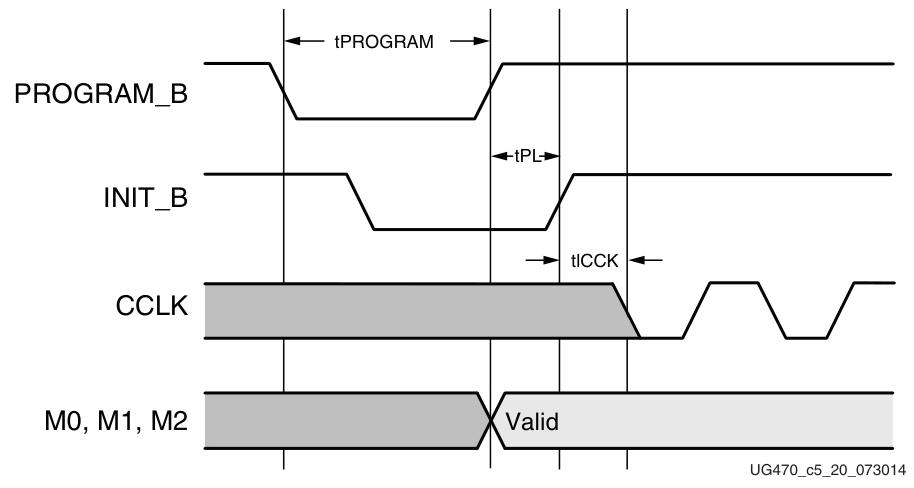

i)每当器件上电、PROGRAM_B引脚接收低电平脉冲、执行JTAG JPROGRAM指令或IPROG命令,或是在fallback重试配置序列期间,配置存储器都会被依次清空。BRAM会复位至初始状态,flip-flops则通过全局置位复位GSR信号的断言完成重新初始化。

ii)在此期间,除少数配置输出引脚外,所有I/O引脚会通过全局三态GTS机制置于高阻态High-Z。若PUDC_B引脚为低电平,这些I/O引脚还会启用内部上拉电阻。初始化过程中,INIT_B引脚会被器件内部驱动为低电平;对于上电场景,该引脚会在满足上电复位时间T_POR后释放为高电平;其他触发场景下,则会在满足编程延迟T_PL后释放。若INIT_B引脚被外部保持低电平,器件会在此初始化阶段暂停,直至该引脚被释放,且 T_POR 或 T_PL 延迟要求得到满足。

iii)PROGRAM_B引脚的最低低电平脉冲宽度由时序参数T_PROGRAM(编程脉冲宽度)定义。

③采用模式引脚(步骤3)

i)当INIT_B引脚跳转为高电平时,器件会对M[2:0]模式引脚进行采样;若处于主模式,器件还会开始驱动CCLK时钟。此时,器件会在配置时钟的上升沿对配置数据输入引脚进行采样。对于BPI模式和SelectMAP模式,总线宽度初始默认为x8,状态寄存器会反映这一初始状态;完成总线宽度检测序列后,状态寄存器将更新为实际检测到的总线宽度。仅当通过上电复位(电源循环)或触发PROGRAM_B引脚(断言PROGRAM_B信号)执行重新配置时,模式引脚才会被再次采样。

2)比特流加载(步骤4-7):所有配置模式的比特流加载流程基本一致,核心差异仅在于与配置逻辑的接口形式。

①同步(步骤4)

i)对于BPI模式、从模式SelectMAP、主模式SelectMAP,需先进行总线宽度检测;而从模式串行、主模式串行、SPI、JTAG模式会忽略总线宽度检测序列。之后,需向配置逻辑发送一个专用32位同步字(0xAA995566),该同步字用于告知器件后续将传输配置数据,并使配置数据与内部配置逻辑实现对齐。同步操作执行前,配置输入引脚上的所有数据都会被忽略,仅总线宽度自动检测序列除外。

②设备ID校验(步骤 5)

i)器件完成同步后,需先通过设备ID校验,才能加载配置数据帧。这一机制可避免使用为其他器件格式化的比特流进行配置。若配置过程中出现ID错误,器件会尝试执行fallback重新配置。

ii)设备ID校验已内置在比特流中,因此对大多数设计人员而言该步骤是透明的。需注意的是,此场景下的设备ID校验通过比特流中的命令向配置逻辑发起,而非通过JTAG IDCODE寄存器执行。

③加载配置数据帧(步骤6)

i)完成同步字加载和设备ID校验后,将开始加载配置数据帧。此过程对大多数用户而言是透明的。

④循环冗余校验(CRC校验,步骤7)

i)在配置数据帧加载过程中,器件会根据配置数据包计算循环冗余校验值。配置数据帧加载完成后,配置比特流会向器件发送校验CRC指令,并附带预期的CRC值。若器件计算的CRC值与比特流中的预期CRC值不匹配,器件会将INIT_B引脚拉低并中止配置。

ii)CRC校验默认已包含在配置比特流中,设计人员也可根据需要禁用。需注意,禁用CRC校验可能导致加载错误的配置数据帧,进而引发设计功能异常或器件损坏。

iii)对于加密比特流(当BITSTREAM.ENCRYPTION.ENCRYPT属性设为Yes时),CRC校验会被禁用,转而通过HMAC对加密比特流数据进行认证。比特流数据中的错误会以HMAC错误的形式记录在BOOTSTS寄存器中。HMAC验证同时验证数据完整性+身份认证,防止数据被篡改或伪造。

iv)若在FPGA作为配置主设备的模式下发生CRC错误,器件会尝试执行fallback重新配置:BPI和SPI模式下,若fallback重新配置再次失败,仅能通过拉低PROGRAM_B引脚并重新启动配置流程,才能使BPI/SPI接口重新同步,此时JTAG接口仍可响应,器件未失效,仅BPI/SPI接口无法工作;在SelectMAP模式下,可通过拉低PROGRAM_B引脚或启动ABORT序列恢复。

v)7系列器件采用32位CRC校验,其设计目的是检测配置比特流传输过程中的错误,但存在一种特殊情况可能导致CRC校验漏检:若发生特定时钟错误(如双倍时钟),会使32位比特流数据包与配置逻辑失去同步;同步丢失后,后续所有命令(包括CRC校验命令)都会被忽略,此时配置会失败,表现为DONE引脚低电平、INIT_B引脚高电平(因CRC校验未执行)。

vi)在BPI异步读取模式下,地址计数器最终会溢出或下溢导致地址回绕,进而触发fallback重新配置;BPI同步读取模式不支持该回绕错误触发机制。

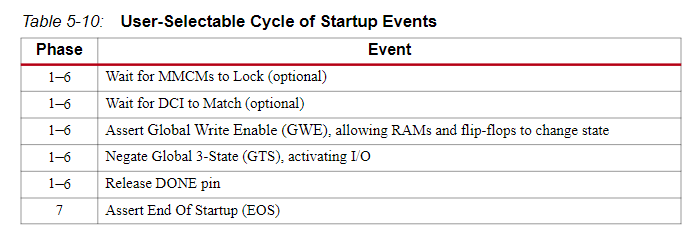

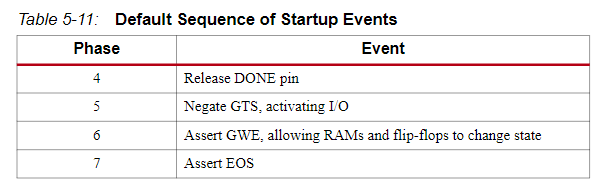

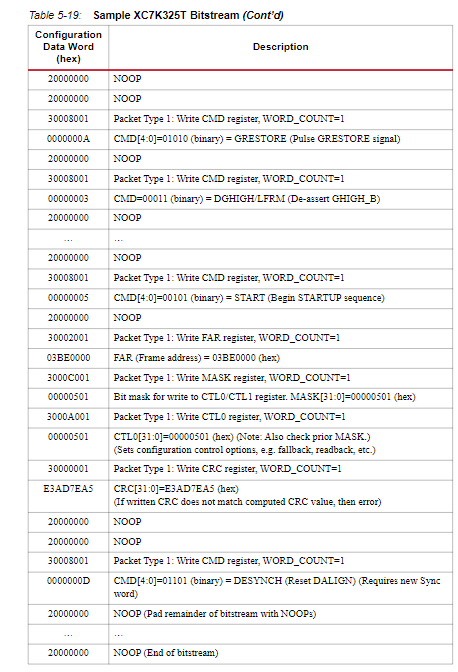

3)启动序列(步骤8)

①配置数据帧加载完成后,比特流会指令器件进入启动序列。启动序列由8个阶段(阶段0-7)的时序状态机控制。除启动结束EOS信号的断言时机固定外,其他启动事件的执行顺序可通过比特流选项编程设置。

②可通过相应选项强制启动序列等待MMCM锁定或DCI匹配,设置这些选项的核心目的是:避免在MMCM锁定或DCI匹配完成前,断言 DONE、GTS、GWE信号,防止器件提前工作。

③启动序列会在用户指定的时钟周期释放DONE信号,但需等待DONE引脚实际检测到高电平后,启动序列才会继续推进。DONE引脚为开漏双向信号,释放DONE信号即器件停止驱动其为低电平,此时该引脚会通过内部上拉电阻拉至高电平。默认情况下,DONE_PIPE功能已启用,用于在DONE引脚与配置逻辑之间增加一个寄存器(以优化信号稳定性)。

④GWE断言时,允许RAM和flip-flops改变状态,同时启用FPGA的其他同步逻辑单元。GTS断言时,禁用所有I/O驱动单元,仅保留少数配置引脚的功能。EOS标志配置与启动流程完全结束。DCI_MATCH指示所有数字控制阻抗DCI控制器是否已将内部电阻与外部参考电阻匹配完成。MMCM_LOCK指示所有MMCM是否已锁定,默认状态为断言,仅当MMCM启用了LOCK_WAIT选项,且比特流生成时配置了LockCycle选项时,该信号才会根据实际锁定状态变化。

⑤GWE信号的断言与配置时钟CCLK同步,但在整个器件上存在明显的时序偏差。因此,时序逻辑单元的释放与用户系统时钟并不同步,启动过程中可能出现时序违规。建议在启动完成后对设计进行复位,或采用其他同步技术规避风险。

4)启动阶段的时钟保障(直至启动结束)

①默认情况下,DONE引脚会在启动序列的第4阶段释放,且DONE_PIPE功能已启用(可增加一个时钟周期的延迟)。DONE信号的置位表明配置已完成、所有数据均已加载,但仍需施加额外的时钟周期,以确保启动序列能完整推进至第7阶段(启动结束,End of Startup)。保守起见,DONE置位后建议额外提供64个时钟周期,可覆盖绝大多数常见应用场景。若比特流配置了LCK_cycle(MMCM锁定等待周期)或 Match_cycle(DCI匹配等待周期)选项,则会额外增加不确定数量的时钟周期。

5)启动结束时的I/O过渡现象

①对于AMD Spartan-7、Artix-7、Kintex-7系列器件,其多功能配置引脚位于HR I/O banks。若该bank的VCCO供电电压为1.8V或更低,且bank内某引脚处于低电平或悬空状态,则在配置启动过程中,该引脚向互连逻辑传输的信号可能出现0-1-0的过渡波动。

②由于此过渡波动发生在GWE信号启用内部逻辑之后,可能会影响器件配置后的内部状态。该波动具体出现在EOS信号生效后的1个配置时钟CFGCLK周期。为避免此现象,可将VCCO_14和VCCO_15设置为2.5V或3.3V,或通过外部电路将相关引脚驱动为高电平;若无法采用上述方法,则需在设计中设置逻辑,使受影响的输入信号在EOS上升沿后的1个CFGCLK周期+200ns内被忽略。CFGCLK和EOS信号可通过STARTUPE2原语进行监控。

6)多功能配置引脚与DCI的配合使用

①若用户设计中,14号或15号I/O bank的任何配置引脚被分配了DCI I/O标准,则设计中必须同时包含并使用DCIRESET原语。具体操作要求:先向DCIRESET原语的RST输入引脚发送一个复位脉冲,待其LOCKED信号断言后,再使用这些多功能配置引脚上的用户输入/输出。

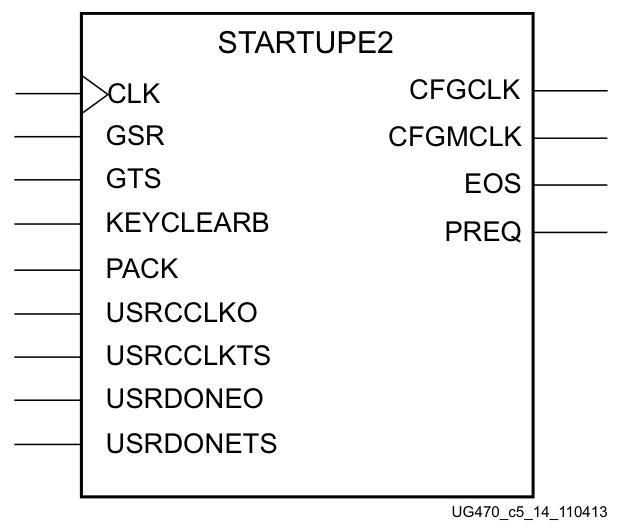

STARTUPE2

a)STARTUPE2原语是用户逻辑与配置逻辑的控制和状态信号之间的接口桥梁,其多数引脚与启动序列相关,包括CLK引脚(允许用户指定启动时钟)。在设计中实例化STARTUPE2原语后,用户可在器件运行期间对选定的配置信号进行控制。

b)

1)引脚解释

①CLK:自定义启动序列时钟,替代默认CCLK。实际应用在高速接口设计(如10G Ethernet),需高精度启动时序;MMCM/DCI匹配对时钟敏感的场景;多FPGA启动时钟同步需求。Spartan-7仅7S25/7S50及以上支持。需配置比特流属性STARTUPCLK=UserClk。时钟频率需≤60MHz。

②GSR:全局置位/复位,异步重新初始化CLB触发器。实际应用在特殊场景下的紧急复位(如系统故障时);需重新初始化触发器但不希望重新配置的场景。不建议默认使用,因为异步释放易导致亚稳态,且器件内时序偏差会使触发器释放不同步。必须使用时,先停止所有用户时钟,复位后重新同步逻辑。替代方案是使用IPROG命令重新配置,更安全。

③GTS:全局三态控制,将用户I/O(配置bank除外)置为高阻态。实际应用在调试时临时禁用I/O输出,避免干扰其他器件;系统故障时隔离故障FPGA的I/O;多FPGA共享总线时的总线仲裁。配置期间默认生效(I/O高阻),启动后需拉低禁用;高电平有效,需通过用户逻辑控制,不可悬空。

④KEYCLEARB:清除BBRAM中的AES解密密钥。实际应用在军工、金融等安全敏感场景;设备退役、固件升级时的密钥销毁;遭遇安全威胁时的应急处理。低电平有效,需保持时长≥T_PROGRAM(数据手册规定);仅在启用AES加密时有效;密钥清除后不可恢复,需谨慎操作。

⑤PACK:PROGRAM_B/JPROGRAM复位的应答信号。实际应用在自定义复位流程(如用户逻辑需完成数据保存后再响应复位);避免复位冲突(如同时收到多个复位请求)。需设置比特流属性PROG_USR=Yes才生效;高电平应答,用户逻辑完成准备后断言,复位流程才继续。

⑥PREQ:PROGRAM_B/JPROGRAM复位的请求信号。实际应用在自定义复位流程中,接收复位请求并准备;数据保存、状态备份(如工业控制中的工艺参数备份)。需设置PROG_USR=Yes才生效;高电平表示复位请求,用户逻辑需在收到后停止关键操作。

⑦USRCCLKO:配置后驱动CCLK引脚,输出自定义时钟。实际应用在配置后驱动外部SPI/BPI闪存;配置后提供辅助时钟(如低速外设时钟);回读CRC逻辑的时钟源(配合POST_CRC)。时钟频率需≤100 MHz(数据手册限制),前3个时钟周期无外部输出,需预留切换时间,配置后生效,配置期间无效。

⑧USRCCLKTS:CCLK引脚的三态使能。实际应用在禁用CCLK输出(如不需要驱动外部设备时);避免CCLK引脚干扰其他信号。高电平使能三态(CCLK悬空),低电平禁用三态(CCLK输出);多数场景下拉低,启用CCLK输出;不可悬空,需通过电阻拉低/高。

⑨USRDONEO:自定义DONE引脚的输出值。实际应用在多FPGA协同时,统一DONE电平;自定义DONE信号的输出时序(如延迟释放);系统状态指示。需配合USRDONETS使用;高电平/低电平可自定义,需与系统逻辑匹配;不可悬空,需通过用户逻辑驱动。

⑩USRDONETS:DONE引脚的三态使能。实际应用在禁用DONE输出(如多FPGA同步时,避免单个DONE提前拉高);隔离DONE引脚(如调试时)。高电平使能三态(DONE悬空),低电平禁用三态(DONE输出);默认拉低,启用DONE输出;多FPGA同步时,可先拉高,所有FPGA就绪后再拉低。

c)STARTUPE2原语的经典应用场景

1)自定义启动时钟(解决默认时钟精度不足问题):

默认启动时钟CCLK由内部振荡器生成,频率漂移较大(±50%),若需确保MMCM锁定、DCI匹配等关键步骤的时序稳定性(如高速接口设计),需自定义高精度启动时钟。可以将CLK引脚连接到用户逻辑生成的25MHz晶振时钟(精度±10ppm),在Vivado中设置比特流属性:set_property BITSTREAM.STARTUP.STARTUPCLK UserClk [current_design],启动序列将以25MHz精准推进,MMCM锁定等待时间和DCI匹配时间可精准计算,避免因时钟漂移导致的启动失败。

2)启动完成同步(确保用户逻辑安全启动):

用户逻辑(如DDR控制器、PCIe接口)需在FPGA完全启动后才释放复位,避免启动阶段I/O未激活、RAM未初始化导致的硬件故障。将STARTUPE2的EOS引脚连接到用户设计的复位控制器(如AXI复位IP);FPGA完成启动序列(第7阶段,EOS置高)后,复位控制器释放用户逻辑的复位信号;此时FPGA已完成:DONE释放、GTS撤销(I/O激活)、GWE断言(RAM/触发器可写),用户逻辑可安全工作。

3)配置后驱动外部 SPI 闪存(扩展配置后数据读取功能):

配置完成后需通过FPGA的CCLK引脚驱动外部SPI闪存,读取应用程序镜像或配置参数(如工业控制中的校准数据)。配置完成后,用户逻辑生成10MHz时钟(SPI闪存支持的最大SCLK频率),输入到USRCCLKO;将USRCCLKTS拉低(禁用CCLK三态,启用输出);CCLK 引脚输出10MHz时钟,连接到SPI闪存SCLK引脚,配合MOSI/MISO引脚完成数据读取。注意,USRCCLKO的前3个时钟周期用于时钟源切换(从内部振荡器到用户时钟),不会输出到外部,避免毛刺干扰SPI闪存。

4)多FPGA启动同步(解决多器件协同时序问题):

多FPGA组成的系统(如视频处理阵列)中,需所有FPGA同步完成启动后再联动工作,避免单个FPGA提前输出数据导致的同步错误。每片FPGA的USRDONETS拉低(启用DONE输出),USRDONEO引脚连接到系统同步总线;每片FPGA的EOS引脚连接到同步总线的与门输入;当所有FPGA的EOS均为高电平时(全部启动完成),与门输出高电平,触发所有FPGA的USRDONEO统一拉高,实现多器件启动同步。

比特流安全

基础安全防护方式是禁止回读:比特流的安全级别可设置为Level1(禁用回读)或Level2(同时禁用回读和重新配置)。

a)比特流加密(Bitstream Encryption)

1)7系列器件内置高级加密标准AES解密逻辑,可提供高等级的设计安全防护。若无加密密钥,攻击者即使截获外部传输的比特流,也无法对其进行分析以理解或克隆设计。加密后的7系列FPGA设计无法被复制或逆向工程破解。

2)7系列FPGA的AES系统由三部分组成:软件端比特流加密、芯片端比特流解密、专用密钥存储单元。用户可通过AMD工具生成加密密钥和加密比特流,密钥需存储在器件内部的专用RAM(需外接小型电池备份)或电子熔丝(eFUSE)中,且仅能通过JTAG端口写入器件。

3)配置过程中,7系列器件会执行反向操作,对传入的比特流进行解密。该AES加密逻辑采用256位加密密钥,且芯片内置的AES解密逻辑仅用于比特流解密,不可用于其他用途,即用户设计无法调用该解密逻辑,也不能用其解密配置比特流以外的任何数据。注:Spartan-7系列的7S6和7S15器件不支持AES加密功能。

b)AES概述

1)7系列FPGA的加密系统采用高级加密标准AES算法,该算法是美国国家标准与技术研究院NIST及美国商务部认可的官方标准。该AES系统仅支持256位加密密钥(NIST描述的128位和192位密钥长度未实现),每次加密或解密128位数据块。根据NIST测算,256位密钥的可能组合数量达1.1×10⁷⁷种,安全性极高。

2)AES属于对称加密算法,加密与解密使用同一密钥,因此数据安全性完全依赖密钥的保密性。

c)创建加密比特流

1)ISE软件附带的BitGen工具可生成加密或非加密比特流。生成AES加密比特流时,用户需启用Encrypt选项,并通过Keyfile选项向BitGen工具输入256位密钥;BitGen工具会据此生成加密比特流文件.BIT格式和加密密钥文件.NKY格式。

d)加载加密密钥

1)加密密钥仅能通过JTAG接口写入7系列器件:可将.NKY密钥文件导入iMPACT工具或Vivado器件编程器,通过兼容的AMD编程电缆,经JTAG接口将密钥编程至器件。

2)密钥编程流程如下:器件通过XSC_PROGRAM_KEY指令进入特殊的密钥访问模式,此时器件内所有存储器(包括加密密钥存储区和配置存储器)会被清空;密钥编程完成并退出该模式后,密钥无法通过任何方式读出,且需清空整个器件才能重新编程密钥(该密钥访问模式对多数用户而言是透明的)。

3)若将密钥存储在eFUSE中,用户可先回读密钥进行验证,验证完成后必须通过编程FUSE_CNTL寄存器的read_en_b_key位,禁用AES密钥的读写功能

e)加载加密比特流

1)器件写入正确的加密密钥后,即可使用加密比特流进行配置。使用加密比特流完成配置后,无论比特流安全级别如何设置,均无法通过 JTAG或SelectMAP接口回读配置存储器。

2)若器件已存储加密密钥,仅当执行上电复位POR或断言PROGRAM_B引脚后,才能使用非加密比特流进行配置。非加密比特流配置完成后,若比特流安全级别允许,可执行回读操作,但密钥仍无法读出。

3)加密比特流的配置方式基本不受限制:支持同时启用压缩和加密功能,且可通过任意配置接口传输(JTAG、串行、SPI(含x1/x2/x4模式)、BPI、SelectMAP、ICAPE2),但部分配置方式存在限制或时序差异:

①从模式SelectMAP和ICAPE2接口仅支持通过x8总线接收加密比特流;

②主模式SelectMAP和主模式BPI接口支持x8或x16总线接收加密比特流,但x16总线宽度下,主模式CCLK频率会降至ConfigRate设定值的一半(若启用ExtMasterCCLK_en选项,则降至EMCCLK频率的一半);

③低速CCLK从比特流中DEC(AES加密使能)位被读取时开始生效,早于基于ConfigRate或外部EMCCLK更新CCLK频率的时机。

4)加密比特流必须对器件进行全配置,外部配置接口不支持加密比特流的部分重配置。配置完成后,需通过拉低 PROGRAM_B 引脚、上电复位或执行 JPROGRAM 指令,才能重新配置器件。即使启用加密功能,7 系列 FPGA 仍支持 fallback 重新配置和 IPROG 重新配置;若保持 VCCBATT 或 VCCAUX 供电,上述操作均不会重置密钥。

f)比特流加密与内部配置访问端口ICAPE2

1)内部配置访问端口ICAPE2原语为用户逻辑提供了对7系列FPGA配置接口的访问权限。

2)ICAPE2接口与SelectMAP接口类似,均涉及位交换操作。该接口拥有独立的输入和输出总线,CSIB输入会忽略输入总线,但输出总线仍可继续切换状态。其时序特性与SelectMAP接口相近,7系列FPGA数据手册中提供了其最大频率FICAPCK参数。

3)与SelectMAP接口的回读限制不同,配置完成后,ICAPE2接口不受该限制约束。即便启用了比特流加密功能,用户仍可通过ICAPE2接口发送部分比特流(无论加密与否)或执行回读操作。

4)除非设计人员将ICAPE2接口连接至用户I/O,否则该接口不会为攻击者提供破解7系列FPGA AES加密机制的途径。因此,关注设计安全性的用户不应将ICAPE2接口与用户I/O相连,而连接ICAPE2时钟则不会对安全性产生影响。

5)当同时启用回读CRC和比特流加密功能时,若未实例化ICAPE2原语并提供时钟信号,回读CRC功能将无法正常工作。与其他配置接口相同,ICAPE2接口同样无法访问密钥寄存器。

g)高级加密标准AES

1)7系列FPGA支持的高级加密标准AES与Virtex-6器件完全一致。用户需将256位加密密钥加载到eFUSE位或电池供电的RAM中,AMD比特流生成工具会采用AES算法对比特流进行加密处理。

2)该功能支持用户采用256位AES加密算法的密码块链接CBC模式对其比特流进行加密。用户可自行提供128位初始向量和256位密钥,也可由软件随机生成密钥。部分安全功能(例如通过FPGA逻辑清除电池供电RAM中AES密钥)需将器件配置为加密比特流才能正常工作。

3)当加密密钥存储在FPGA的电池供电RAM中时,密钥存储单元为易失性,需持续供电以保留密钥内容。正常工作时,这些存储单元由辅助电压输入VCCAUX供电;若需在VCCAUX断电后保留密钥,需通过专用的VCCBATT电源输入接口连接电源。由于VCCBATT的功耗极低(纳安级),小型纽扣电池即可满足供电需求(电池寿命估算可参考对应7系列FPGA数据手册中的VCCBATT直流特性及电池规格说明)。

4)VCCBATT仅在VCCAUX断电时用于保留加密密钥,无其他用途;当VCCAUX正常供电时,VCCBATT可断开连接,且不会产生功耗。

比特流认证

a)概述

1)7系列FPGA片上集成了硬件实现的比特流密钥哈希消息认证码HMAC算法,提供了超越AES加密本身的额外安全性。若未掌握AES密钥和HMAC密钥,比特流无法被加载、修改、拦截或克隆。

2)AES加密为设计提供基础安全保障,防止设计被复制或逆向工程;而HMAC则能确保用于FPGA配置的比特流是未经篡改的授权版本,可检测包括单比特翻转在内的任何比特流篡改行为。

3)HMAC算法使用的密钥可由用户提供给AMD软件,也可由软件自动生成随机密钥。该HMAC密钥与AES密钥相互独立且不同。AMD软件会利用该密钥和SHA算法生成一个256位的消息认证码MAC,该MAC作为AES加密比特流的一部分传输,用于验证比特流的数据完整性和真实性,认证范围覆盖比特流中所有类型的控制信息和数据。使用时,7系列FPGA的安全解决方案必然同时包含HMAC和AES功能,Vivado实验室工具也提供类似功能。

b)实现原理

1)7系列FPGA的HMAC认证系统由两部分组成:AMD软件中的HMAC组件、集成在每款7系列FPGA中的硬件组件。两部分均基于密钥和安全哈希算法SHA256生成256位MAC。

2)MAC验证数据完整性和真实性的流程

①密钥与MAC生成:HMAC算法使用独立于AES密钥的专属密钥(可由用户提供或软件随机生成),AMD软件结合该密钥与SHA256算法,对整个比特流(含所有控制信息和数据)计算生成256位消息认证码MAC,并将其嵌入AES加密比特流中一同传输。

②配置阶段的验证:FPGA配置时,片上HMAC/SHA256硬件引擎先通过AES解密比特流数据,再基于解密后的原始数据重新计算MAC,最后将新计算的MAC与比特流中嵌入的原始MAC进行比对。

③验证结果处理:若两者一致,配置正常完成并进入启动流程;若不一致且启用降级fallback功能,会清空器件配置后加载降级比特流;若未启用降级功能,配置接口会被禁用,需通过PROGRAM_B引脚脉冲或上电复位重置接口。

3)验证完整性和真实性的原因

①保障数据完整性:比特流在传输、存储过程中可能因干扰、硬件故障等出现比特翻转、数据丢失等问题,验证完整性可精准检测这类篡改,避免因错误比特流导致FPGA配置失败、功能异常甚至硬件损坏。

②确保数据真实性:防止恶意第三方替换合法比特流(如植入恶意逻辑的特洛伊木马比特流),确保加载到FPGA的是授权且未被篡改的原始设计,保护知识产权不被非法篡改和滥用。

③强化整体安全体系:AES加密主要防止比特流被非法复制和逆向工程,而HMAC验证是对加密功能的补充,两者结合形成加密 + 认证的双重安全机制,全面抵御复制、篡改、替换等多种安全威胁,适用于对安全性要求较高的工业控制、通信等场景。

c)无需片上存储HMAC密钥

1)AES加密认证比特流可通过所有外部标准配置接口加载,但不支持x16或x32总线宽度的从模式SelectMAP接口。若器件已通过加密比特流完成配置,需先触发PROGRAM_B引脚、执行JTAG JPROGRAM指令或进行上电复位,清空当前所有配置存储器后,才能加载另一个非加密比特流。

eFUSE

a)电子熔丝eFUSE是一种非易失性一次性可编程技术,适用于特定的配置设置。通过在特定时间内施加大电流,可对熔丝链路进行编程。用户可编程的eFUSE可通过AMD配置工具完成编程,且编程过程中器件需处于未配置状态。编程后的熔丝链路,其电阻通常比未编程的原始熔丝高出几个数量级。已编程熔丝的逻辑值为1,未编程熔丝的逻辑值为0。

b)eFUSE控制寄存器FUSE_CNTL

1)该寄存器包含用户可编程位,这些位用于选择AES密钥的使用方式,并为eFUSE寄存器设置读写保护,其中bit0优先移入或移出。

2)eFUSE位为一次性可编程OTP,编程后无法撤销。例如,若某寄存器的访问权限被禁用,将无法重新启用。

3)当FUSE_CNTL[0]未编程时:可通过比特流选项启用或禁用加密功能;可通过比特流选项选择存储在eFUSE或电池供电静态随机存取存储器BBRAM中的AES密钥。

4)警告!当FUSE_CNTL[0]编程后,仅能通过外部配置端口使用经eFUSE密钥加密的比特流对FPGA进行配置。这将导致无法使用AMD测试比特流和预构建比特流对器件进行配置,因此AMD不支持对已编程FUSE_CNTL[0]位的器件提供退货授权RMA服务,也不支持通过iMPACT工具进行间接SPI/BPI闪存编程。

5)若FUSE_CNTL[1]已编程,初始配置完成后,外部配置端口将被禁止访问配置存储器。重新配置器件的唯一方式为:电源循环、下发 JPROGRAM或IPROG指令,或触发PROGRAM_B引脚脉冲。

6)位解释

①CFG_AES_Only:强制使用存储在eFUSE中的AES密钥。编程该位前,FPGA可使用未加密比特流,或使用经电池供电静态随机存取存储器BBRAM中密钥加密的比特流进行配置。警告!切勿在7S6或7S15器件上设置该位。7S6和7S15不支持AES加密,设置该位将永久禁用器件配置功能。对于其他7系列FPGA,编程该位后,若未知晓对应的AES密钥,器件将无法使用,且AMD不接受已编程该位器件的退货授权RMA申请。

②AES_Exclusive:禁止通过外部配置接口进行部分重配置,但允许通过ICAPE2接口执行部分重配置。警告!编程该位后,AMD对器件的分析和调试能力将受限,退货授权RMA服务也会受到限制。如需防止回读和重配置,可选择安全级别2(Security Level2)。

③W_EN_B_Key_User:禁用AES密钥和FUSE_USER寄存器的编程功能。

④R_EN_B_Key:禁用AES密钥的读取功能,同时禁用AES密钥和用户代码的编程功能。该位不会禁用通过EFUSE_USR原语读取用户代码,但会禁用通过JTAG端口读取用户代码。

⑤R_EN_B_User:禁用用户代码的读取功能,同时禁用AES密钥和用户代码的编程功能。

⑥W_EN_B_Cntl:禁用控制位的编程功能。

c)JTAG指令

1)eFUSE寄存器可通过JTAG端口读取,而eFUSE编程仅能通过JTAG执行。JTAG指令寄存器长度为6位,除非是采用堆叠硅互连SSI技术且含超级逻辑区域SLR的器件。

比特流构成

a)

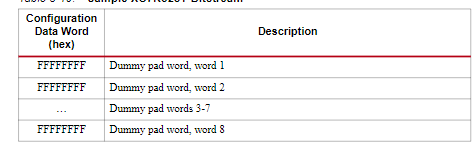

1)器件上电且初始化完成(以INIT_B引脚释放为标志)后,配置即可启动。初始化完成后,包处理器会忽略配置接口上的所有数据,直至识别到特定的数据模式(通常为同步字)。

2)对于外部并行接口(BPI或SelectMAP模式),会先通过总线宽度自动检测模式设定配置接口的总线宽度。总线宽度设定完成后,以及对于其他所有配置接口,包处理器会继续忽略配置接口上的所有数据,直至识别到同步字。

3)识别到同步字后,配置逻辑会将每个32位数据字作为一个配置包,或多字配置包的组成部分进行处理。

b)

c)配置存储帧与配置包

1)配置存储帧:7系列FPGA的配置存储器以帧为单位在器件内呈平铺式排列。这些帧是7系列FPGA配置存储空间中最小的可寻址单元,因此所有操作都必须对完整的配置帧执行。每个配置帧包含101个32位字。根据比特流选项的不同,配置比特流中会存在额外开销。比特流的精确长度可通过以下方式获取:使用BitGen工具的-b选项生成原始比特文件(RBT格式)、在ISE软件的生成编程文件选项弹窗中勾选创建ASCII配置文件。比特流长度(以字为单位)大致等于配置阵列大小(字)加上配置开销(字);比特流长度(以比特为单位)大致等于比特流的字长度乘以32。

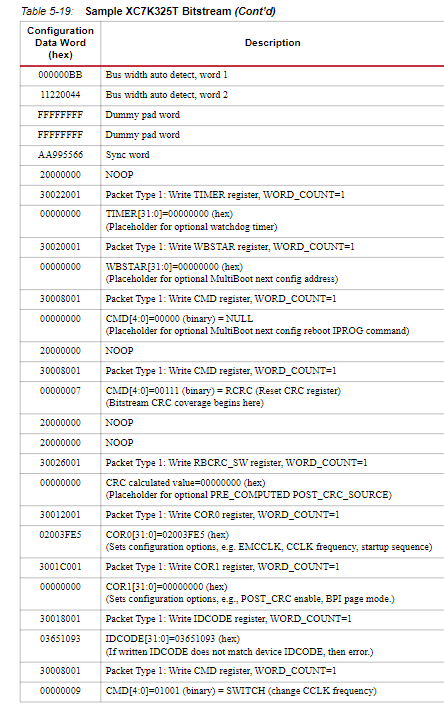

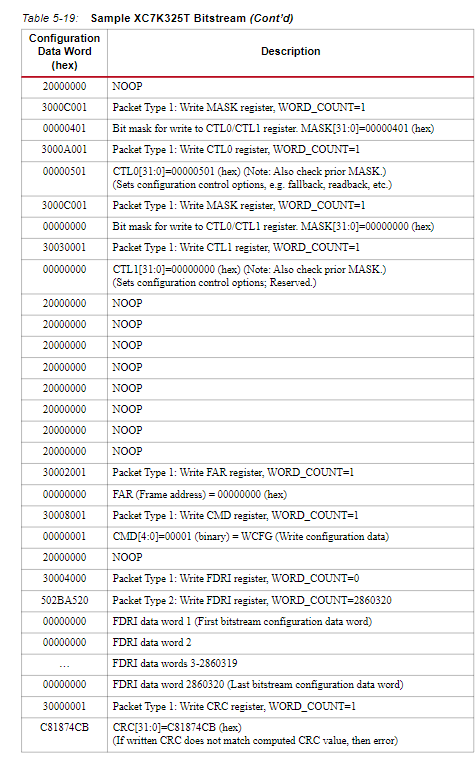

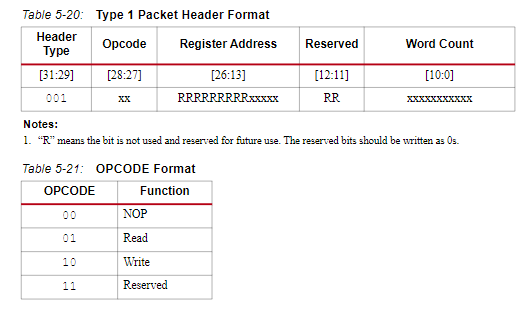

2)配置包:7系列FPGA的所有比特流命令,均通过对配置寄存器执行读写操作来实现。FPGA比特流包含两种包类型:Type 1和Type 2,其具体类型及用途如下。

①1类包用于执行寄存器读写操作。7系列FPGA仅使用14个寄存器地址位中的5个,包头部分固定为32位字长。1类包头之后是1类包数据段,其中包含的32位字数量由包头中的字计数字段指定。

②2 类包必须紧跟在1类包之后,用于写入长数据块。由于其沿用前一个1类包指定的地址,因此无需在此单独指定地址。包头部分固定为32位字长。2类包头之后是2类包数据段,其中包含的32位字数量由包头中的字计数字段指定。

d)配置寄存器

1)CRC寄存器(00000):向该寄存器写入数据,可对比特流数据执行CRC校验;若写入值与当前计算的CRC值一致,CRC_ERROR标志会被清除,器件允许启动。

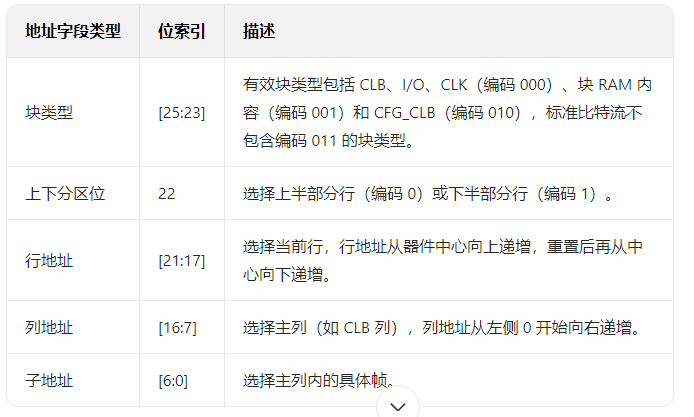

2)帧地址寄存器(FAR,00001)

①7系列器件分为上下两个部分,所有帧的长度固定一致,均为3232比特(即101个32位字)。帧地址寄存器FAR分为五个字段:块类型、上下分区位、行地址、列地址、子地址。地址既可直接写入,也可在每帧结束后自动递增。标准比特流通常从地址0开始,按顺序自动递增至最终地址。

3)帧数据输入寄存器(FDRI,00010):向该寄存器写入数据,可配置帧地址寄存器FAR指定地址对应的帧数据。

4)帧数据输出寄存器(FDRO,00011):该寄存器为只读,用于输出帧地址寄存器FAR指定起始地址的配置帧回读数据。

5)命令寄存器(CMD,00100):命令寄存器CMD用于向配置控制逻辑下发指令,以触发全局信号或执行其他配置功能。每次向帧地址寄存器FAR加载新值时,命令寄存器中存储的命令都会被执行。

NULL:空命令,无任何操作。

WCFG:写入配置数据,向FDRI写入配置数据前需执行此命令。

MFW:多帧写入,将单个帧数据写入多个帧地址。

DGHIGH/LFRM:最后一帧:撤销GHIGH_B信号,激活所有互连资源;GHIGH_B信号可通过AGHIGH命令置位。

RCFG:读取配置数据:从FDRO读取配置数据前需执行此命令。

START:启动流程,CRC校验成功且执行DESYNC命令后,启动器件启动序列。

RCAP:重置捕获信号,在单触发模式下执行回读捕获后,重置CAPTURE信号。

RCRC:重置CRC,重置CRC寄存器。

AGHIGH:置位GHIGH_B信号,将所有互连资源置于高阻态,避免写入新配置数据时产生冲突;此命令仅用于关闭重配置,互连资源可通过LFRM命令重新激活。

SWITCH:切换CCLK频率,将主配置时钟CCLK频率更新为COR0寄存器中OSCFSEL位指定的值。

GRESTORE:触发GRESTORE信号脉冲,根据用户配置,置位或复位IOB和CLB触发器。

SHUTDOWN:启动关闭序列,触发器件关闭流程,流程结束后器件禁用;关闭功能会在下次CRC校验成功或执行RCRC指令(通常为RCRC指令)后激活。

GCAPTURE:触发GCAPTUR 信号脉冲,将当前寄存器状态加载至捕获单元。

DESYNC:重置DALIGN信号,配置结束时用于解除器件同步,此后配置数据引脚的所有值都会被忽略。

IPROG:内部编程,触发热启动。

CRCC:读CRC重计算,选择回读CRC功能后,重配置完成时配置逻辑会重新计算首个回读CRC值;触发GHIGH信号也可实现相同效果,此命令适用于重配置过程中未触发GHIGH信号的场景。

LTIMER:重新加载看门狗定时器。

BSPI_READ:BPI/SPI 比特流重读:重新启动BPI/SPI比特流读取流程。

FALL_EDGE:切换至负边沿时钟:配置数据在CCLK负边沿捕获。

6)控制寄存器0(CTL0,00101):控制寄存器0用于配置7系列器件,对该寄存器的写入操作会受到MASK寄存器的位掩码限制。这一设计允许在不重新指定SBITS位和PERSIST位的情况下,切换GTS_USR_B信号状态。

EFUSE_KEY:选择AES密钥来源:0电池供电RAM(默认);1eFUSE。当DEC位被置位时,该位会被内部重新锁存,此后无法更改,以防止密钥来源切换,即便该位仍支持读写操作。

ICAP_SELECT:ICAPE2端口选择:0启用顶部ICAPE2端口(默认);1启用底部ICAPE2端口。

OverTempPowerDown:启用XADC过温掉电功能:0禁用过温掉电(默认);1启用过温掉电。

ConfigFallback:配置失败时停止流程并禁用默认比特流降级功能,比特流选项为ConfigFallback:Enable/Disable:0启用降级功能

1禁用降级功能(默认)。

GLUTMASK_B:全局LUT掩码信号,用于屏蔽可更改存储单元的回读值。1不屏蔽可更改存储单元的回读值;0屏蔽可更改存储单元的回读值(如分布式RAM或SRL,默认)。

FARSRC:确定FAR[23:0]配置寄存器的输出源:0EFAR(ECC错误帧的地址);1FAR(RBCRC的地址,默认)。

DEC:AES解密器使能位。0解密器禁用(默认);1解密器启用。

SBITS:安全级别,7系列FPGA的安全级别扩展至加密比特流,仅适用于配置端口(不适用于ICAPE2);安全级别在加密比特流末尾或非加密比特流的EOS信号后生效:00读写正常(默认);01禁用回读;1x禁用读写;仅FAR和FDRI寄存器允许在安全级别00和01下执行加密写入操作。

PERSIST :配置结束后保留M2:M0指定的配置接口,通常仅用于SelectMAP接口以支持重配置和回读。

GTS_USR_B:低有效全局三态I/O控制信号,若GTS_CFG_B信号同时置位,会关闭上拉电阻。

6)状态寄存器(STAT,00111):用于指示多个全局信号的状态,可通过SelectMAP或JTAG接口读取。

BUS_WIDTH:配置总线宽度自动检测结果。对于BPI和SelectMAP模式,模式引脚采样后、总线宽度检测前,该字段值为01(x8);若启用ICAPE2,配置完成后该字段反映ICAPE2的总线宽度。

STARTUP_STATE:配置启动状态机(0至7阶段),对应编码:

阶段 0 = 000

阶段 1 = 001

阶段 2 = 011

阶段 3 = 010

阶段 4 = 110

阶段 5 = 111

阶段 6 = 101

阶段 7 = 100。

XADC_OVER_TEMP:XADC过温报警。

DEC_ERROR:解密错误标志,在解密操作之前或之后尝试向FDRI写入数据时触发。0无解密错误,1存在解密错误。

ID_ERROR:器件ID错误标志,未通过器件ID校验就尝试向FDRI写入数据时触发。

DONE:DONE引脚的当前状态。

RELEASE_DONE:内部DONE信号的释放状态。

INIT_B:INIT_B引脚的当前状态。

INIT_COMPLETE:指示初始化是否完成的内部信号。

MODE:模式引脚M[2:0]的当前状态。

GHIGH_B:GHIGH_B信号的状态。0GHIGH_B信号置位,1GHIGH_B信号撤销。

GWE:全局写使能GWE的状态,0触发器FFs和块RAM写禁用;1触发器FFs和块RAM写使能。

GTS_CFG_B:全局三态配置信号GTS_CFG_B的状态,0所有用户I/O置于高阻态;1所有I/O按配置正常工作。

EOS:来自启动模块的启动结束EOS信号。

DCI_MATCH:数字控制阻抗DCI匹配状态。该位是所有bank的MATCH信号的逻辑与结果;若某bank无DCI I/O,该bank的MATCH信号默认为1。

MMCM_LOCK锁定状态。该位是所有MMCM的LOCKED信号的逻辑与结果;未使用的MMCM的LOCKED信号默认为1。

PART_SECURED:器件安全状态(解密器安全设置)。

CRC_ERROR:CRC错误标志。

7)LOUT寄存器(01000):软件在串行菊花链配置过程中,通过该寄存器向DOUT引脚驱动数据。

8)配置选项寄存器0(COR0,01001):用于设置器件的特定配置选项。

PWRDWN_STAT:切换DONE引脚功能为掉电状态指示,0DONE引脚保持原有功能;1DONE引脚作为掉电状态指示引脚。

DONE_PIPE:DONE输入信号DONEIN的流水线使能。该选项会在DONE信号被配置逻辑读取前添加一个寄存器,FPGA会等待被延迟一个启动时钟周期的DONE信号。

DRIVE_DONE:DONE信号的驱动模式。0DONE引脚为开漏输出(默认);1DONE引脚主动驱动高电平(不推荐)。

SINGLE:单触发回读使能。0非单触发回读(默认),每次CAPTUREE2原语的CAP信号置位时,都会加载新的捕获值;也可通过CMD寄存器的GCAPTURE指令执行捕获。1单触发回读,连续回读之间需向CMD寄存器加载RCAP指令。

OSCFSEL:主模式下的CCLK频率选择(范围:2MHz -- 60MHz)。

SSCLKSRC:启动序列的时钟源选择:CCLK、用户时钟(通过CAPTUREE2模块连接)、JTAG时钟(JTAGClk)。

DONE_CYCLE:启动序列中释放DONE引脚的阶段:

000:启动阶段 1

001:启动阶段 2

010:启动阶段 3

011:启动阶段 4

100:启动阶段 5

101:启动阶段 6

111:保持(不推荐)。

MATCH_CYCLE:启动序列中等待DCI匹配的阶段:

000:启动阶段 0

001:启动阶段 1

010:启动阶段 2

011:启动阶段 3

100:启动阶段 4

101:启动阶段 5

110:启动阶段 6

111:不等待。

LOCK_CYCLE:启动序列中等待MMCM锁定的阶段:

000:启动阶段 0

001:启动阶段 1

010:启动阶段 2

011:启动阶段 3

100:启动阶段 4

101:启动阶段 5

110:启动阶段 6

111:不等待。

GTS_CYCLE:启动序列中撤销全局三态GTS信号的阶段:

000:启动阶段 1

001:启动阶段 2

010:启动阶段 3

011:启动阶段 4

100:启动阶段 5

101:启动阶段 6

110:GTS信号跟随DONE引脚(比特流选项:-g GTS_cycle:Done)

111:保持(不推荐)。

GWE_CYCLE:启动序列中置位全局写使能GWE信号的阶段:

000:启动阶段 1

001:启动阶段 2

010:启动阶段 3

011:启动阶段 4

100:启动阶段 5

101:启动阶段 6

110:GWE信号跟随DONE引脚(比特流选项:-g GWE_cycle:Done)

111:保持(不推荐)。

9)AXSS寄存器(01101):该寄存器支持USR_ACCESSE2原语,该原语为FPGA逻辑提供直接访问权限,可访问由FPGA比特流存储的32位值,或通过外部 / 内部配置端口重写该32位值(作为配置寄存器)。USR_ACCESS可配置为用户指定的32位值,也可由比特流生成程序自动加载时间戳。用户指定值可用于版本跟踪、设计追溯或序列号管理;当设计源文件未变但执行了多次实现流程时,时间戳功能尤为实用。

→

①USR_ACCESSE2原语的作用:核心作用是为FPGA用户逻辑提供对AXSS配置寄存器的直接访问接口,实现32位数据的读写与管理。支持用户向AXSS寄存器写入32位自定义值(如8位十六进制数据 xxxxxxxx),或设置为NONE(默认值为0,寄存器暂不生效),满足用户对特定标识信息的存储需求。若在生成比特流时配置参数USR_ACCESS: TIMESTAMP,原语会自动将当前系统时间以固定格式(ddddd_MMMM_yyyyyy_hhhhh_mmmmmm_ssssss)嵌入AXSS寄存器,其中:日(5bit)、月(4bit)、年(6bit,最大支持2063年)、时(5bit)、分(6bit)、秒(6bit),精准记录比特流编译时间。除用户逻辑直接访问外,还可通过FPGA配置接口(如 SelectMAP)、JTAG接口、内部配置访问端口ICAP动态修改AXSS寄存器的值,且修改时会触发DATAVALID信号,便于同步状态。

②AXSS寄存器是USR_ACCESSE2原语的直接操作对象,用户通过原语写入的自定义值(如版本号、序列号)或自动加载的时间戳,最终存储在AXSS寄存器中,可通过JTAG、ILA、用户逻辑读取,实现寄存器值 - 比特流 - 设计源的关联。

10)配置选项寄存器1(COR1,01110)

PERSIST_DEASSERT_AT_DESYNC:控制DESYNC命令触发时PERSIST信号的撤销。0禁用DESYNC命令时的PERSIST撤销(默认);

1启用DESYNC命令时的PERSIST撤销。

RBCRC_ACTION:回读CRC错误处理动作:00继续执行;01暂停;11修正并暂停;10修正并继续。

RBCRC_NO_PIN:控制INIT_B引脚是否作为回读CRC错误状态输出引脚。

RBCRC_EN:控制连续回读CRC功能的使能。

BPI_1ST_READ_CYCLE:BPI闪存首次字节读取时序。

BPI_PAGE_SIZE:BPI闪存页大小。

11)热启动起始地址寄存器(WBSTAR,10000):用于指定执行IPROG命令时,MultiBoot功能所使用的地址位置。

RS[1:0]:下次热启动时RS[1:0]引脚的输出值,默认值为00。

RS_TS_B:RS[1:0]引脚的三态使能控制:0三态使能(RS[1:0]禁用,默认);1三态禁用(RS[1:0]启用)。

START_ADDR:下一个比特流的起始地址,默认起始地址为0。

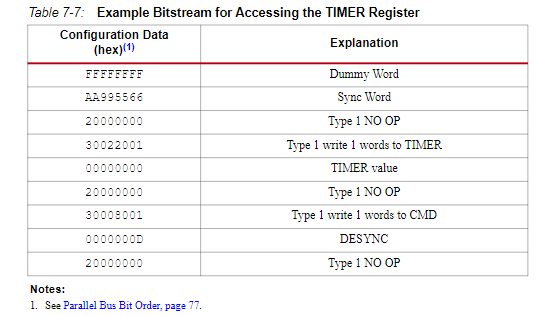

12)看门狗定时器寄存器(TIMER,10001):降级(fallback)比特流会自动禁用看门狗定时器。看门狗超时值,看门狗时钟频率约为125KHz至380KHz,默认值为0。

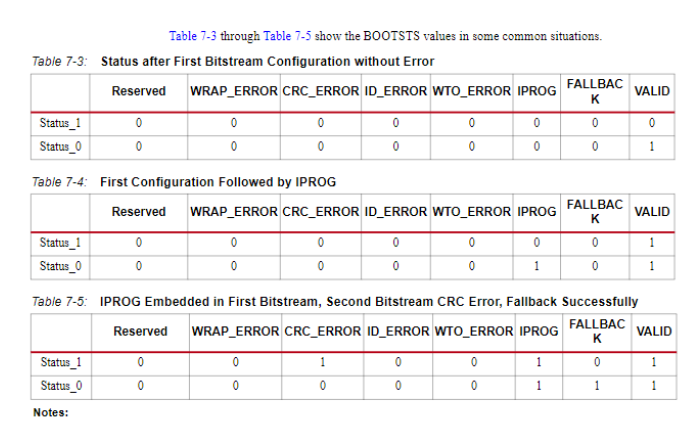

13)启动历史状态寄存器(BOOTSTS,10110):启动历史状态寄存器BOOTSTS仅能通过上电复位POR、置位PROGRAM_B引脚、下发JPROGRAM指令进行复位。当启动序列结束EOS或出现错误时,状态0会移位至状态1,同时状态0会更新为当前状态。该寄存器所有字段的上电默认状态均为0,表示未检测到错误、降级启动、有效配置;配置后,任何bit位为1均表示检测到错误、降级启动、已完成配置。

HMAC_ERROR_1:历史HMAC错误标志;

WRAP_ERROR_1:历史BPI地址计数器环绕错误(仅支持异步读取模式);

CRC_ERROR_1:历史CRC错误标志;

ID_ERROR_1:历史ID_CODE错误标志;

WTO_ERROR_1:历史看门狗超时错误标志;

IPROG_1:历史由内部PROG触发的配置;

FALLBACK_1:历史降级启动状态:1降级至默认重配置,RS[1:0]主动输出2'b00;0正常配置。

VALID_1:历史状态1有效标志;

HMAC_ERROR_0:当前HMAC错误标志;

WRAP_ERROR_0:当前BPI地址计数器环绕错误(仅支持异步读取模式);

CRC_ERROR_0:当前CRC错误标志;

ID_ERROR_0:当前ID_CODE错误标志;

WTO_ERROR_0:当前看门狗超时错误标志;

IPROG_0:当前由内部PROG触发的配置;

FALLBACK_0:当前降级启动状态。1降级至默认重配置,RS[1:0]主动输出2'b00;0正常配置。

VALID_0:当前状态0有效标志。

器件标识符与器件DNA

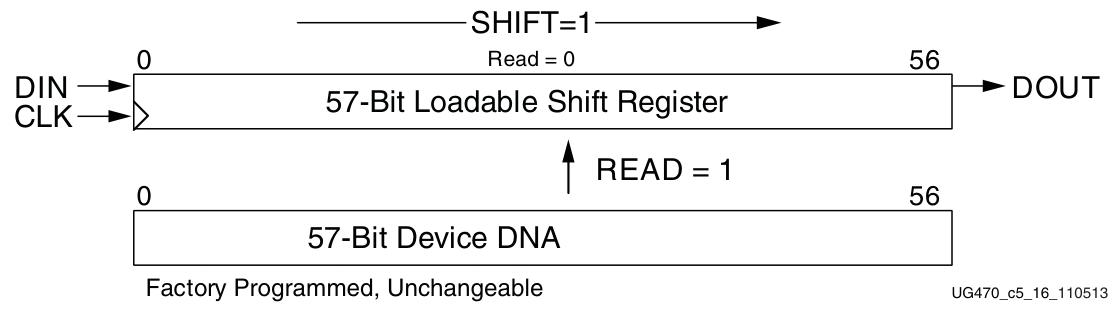

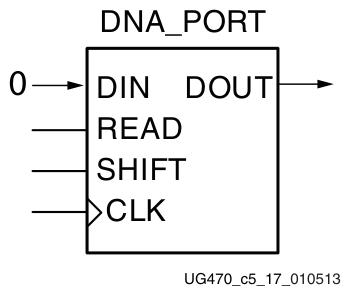

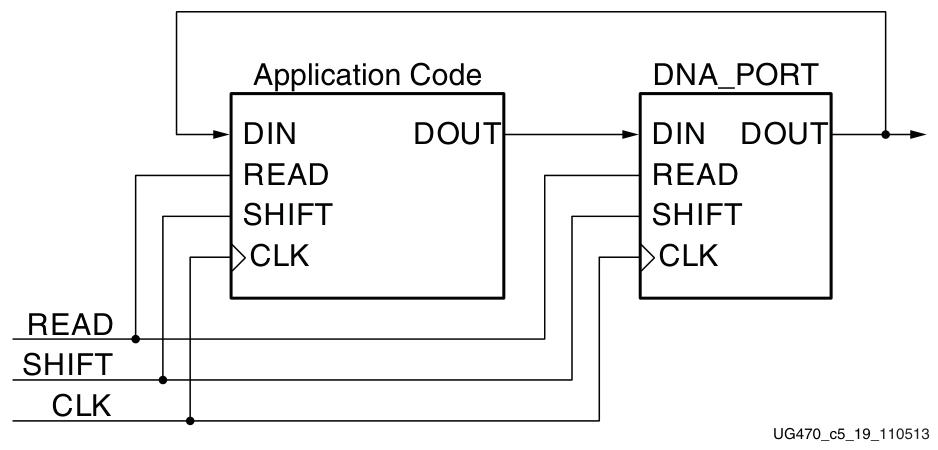

a)7系列FPGA内置一个64位非易失性器件标识符,用于提供57位的器件DNA值。该标识符由AMD在出厂时永久编程到FPGA中,不可修改,具备防篡改特性。每个器件的57位DNA值大多是唯一的,但同一产品系列中最多可能有32个器件共享相同的DNA值。通过JTAG的 FUSE_DNA命令可读取完整的64位标识符(该值始终唯一),而器件DNA由64位FUSE_DNA值的第63至第7位组成。外部应用可通过 JTAG端口访问器件DNA或FUSE_DNA值;FPGA设计仅能通过器件DNA访问端口(DNA_PORT)设计原语访问DNA值,

b)DNA端口原语DNA_PORT操作

1)要读取器件DNA,需先将DNA值传输至DNA_PORT的输出移位寄存器:在时钟CLK上升沿时置位READ输入,该操作会将57位DNA并行加载到输出移位寄存器中,且读取操作会覆盖移位操作;

2)如需连续读取DNA比特,需置位SHIFT输入,随后在CLK上升沿触发移位:输出移位寄存器的内容会向DOUT输出端移位,同时DIN输入上的值会移入移位寄存器;

3)若READ和SHIFT均为低电平,输出移位寄存器会保持当前值,DOUT状态不变。D

→

并行加载:57位DNA 一次性从固化存储区加载到移位寄存器(CLK上升沿完成),避免逐位读取的耗时,保证读取启动的快速性;

串行移位:仅通过1个DOUT引脚逐位输出,无需57位并行输出接口,大幅简化FPGA引脚占用(尤其7系列FPGA引脚资源宝贵)。

DNA_PORT是FPGA内置原语,移位寄存器为硬件固化电路,无需占用CLB等用户资源;仅需4个控制/数据引脚DIN/DOUT/READ/SHIFT+1 个时钟,几乎无额外资源消耗。

c)DNA长度扩展方式

1)多数应用会将DNA_PORT的DIN数据输入接至静态值,实现基础长度的DNA输出。

2)可将DOUT串行输出端口反馈至DIN串行输入端口,使DNA长度扩展至任意所需长度。

3)还可利用FPGA逻辑资源为DNA添加额外比特:通过DNA_PORT的DIN串行输入插入额外数据,这些数据可为固定值,也可基于器件DNA计算得到的变量值。

d)JTAG访问器件DNA与标识符

1)读取器件DNA(57位):通过JTAG端口读取FPGA内部器件DNA时,需使用私有XSC_DNA命令,且需先加载ISC_ENABLE指令(该指令会暂停FPGA设计)。读取完成后,需加载ISC_DISABLE指令重启FPGA设计。当器件进入移位数据寄存器(Shift-DR)状态后,标识符的第56位会出现在JTAG的TDO输出端;后续器件DNA的其余比特及寄存器输入上的所有数据会依次移位输出,此时JTAG控制器保持在Shift-DR状态。

2)通过JTAG端口的私有FUSE_DNA命令可读取完整的64位唯一标识符,其功能与XSC_DNA命令类似,区别在于:FUSE_DNA命令执行后,标识符的第0位会出现在JTAG的TDO输出端。

3)iMPACT软件也可读取57位器件DNA值,对应的批处理命令为readDna -p (为器件在JTAG链中的位置)。Vivado 器件编程器同样支持读取器件DNA值。

e)DNA应用例子

1)开发阶段:将DNA值作为加密密钥的一部分,对FPGA比特流进行加密,仅DNA匹配的器件能解密运行;

2)运行阶段:FPGA读取自身DNA,与上位机下发的授权码(基于DNA计算)比对,匹配则开放高级功能,否则仅保留基础功能。

3)在FPGA逻辑中嵌入DNA校验逻辑,上电后读取DNA值,与比特流中预存的目标DNA比对,不一致则停止核心功能运行;仅DNA匹配时,IP核才正常工作。

回读与配置验证

a)概述

1)AMD7系列器件支持用户通过SelectMAP、ICAPE2、JTAG接口读取配置存储器数据。回读功能分为两种模式:回读校验、回读捕获。

2)在回读校验模式下,用户可读取所有配置存储单元的数据,包括用户侧所有存储单元(查找表随机存储器、移位寄存器查找表、块随机存储器)的当前值。回读捕获功能是回读校验的超集,除读取所有配置存储单元数据外,还能读取内部可配置逻辑块与输入输出块寄存器的当前状态,适用于设计调试场景。

3)执行配置存储器读取操作时,用户需向器件发送特定命令序列以启动回读流程;流程启动后,器件会将配置存储器中的数据导出至 SelectMAP或JTAG接口。

4)用户可通过自定义微处理器、复杂可编程逻辑器件、基于FPGA的系统下发回读命令序列,也可借助工具执行基于JTAG的回读校验操作。AMD ISE软件配套的器件编程软件iMPACT,可对7系列器件执行全部回读与数据比对功能,并向用户反馈是否存在配置错误。需要注意的是,iMPACT不支持回读捕获操作;且在实际设计调试中,回读捕获的使用频率较低,因为ChipScope™ Pro工具凭借更友好的交互界面,可提供更优质的调试功能,Vivado工具也具备类似功能。

5)从器件中读取配置存储器数据后,需将回读比特流与原始配置比特流进行比对,以此判断配置是否存在错误。

b)回读功能的设计准备

1)启用回读功能需满足两项必选比特流设置:一是安全配置不得限制回读操作(需配置为security:none),二是禁止启用比特流加密功能。此外,若需通过SelectMAP接口执行回读操作,必须启用持久化选项(配置为Persist:Yes),确保该接口在配置完成后仍保持功能可用;否则SelectMAP数据引脚会恢复为用户侧I/O引脚,无法继续执行配置相关操作。而通过边界扫描端口执行回读操作时,除满足上述安全与加密相关要求外,无需额外配置。

2)若需启用回读捕获功能,可在用户设计中实例化CAPTUREE2原语,也可通过向命令寄存器写入GCAPTURE命令实现。捕获用户侧寄存器状态时,用户设计需触发该原语的CAP输入信号,将寄存器当前值存入配置存储器;后续执行回读操作时,寄存器值会随其他配置存储器数据一同导出至器件外部。

3)持久化比特流选项的作用是,在器件配置完成后,使多功能配置引脚仍保持配置逻辑的访问权限。该选项主要用于配置完成后保留 SelectMAP接口功能,以便执行回读操作。对于JTAG配置模式,因JTAG端口为专用接口且始终处于可用状态,无需启用持久化选项。需要注意的是,持久化选项与ICAPE2接口功能不可同时启用;在标准主模式SPI/BPI配置方案中,同样不建议启用该选项。若需在进阶级联主模式SPI/BPI配置方案中使用持久化选项,可参考应用笔记XAPP1179。启用持久化选项后,无需触发PROGRAM_B引脚脉冲或使用JTAG端口,即可通过外部控制器对器件执行重配置操作。所有启用持久化功能的I/O引脚,均无法在用户设计中作为普通I/O引脚使用。在设计实现阶段,需通过CONFIG_MODE约束语句预留对应引脚资源。启用持久化功能的I/O引脚默认采用通用I/O标准,具体参数为:LVCMOS、12毫安驱动能力、低速转换速率。

c)CAPTUREE2

1)CAPTUREE2是AMD 7系列FPGA专为回读捕获(Readback Capture) 设计的内置专用原语,是实现FPGA内部寄存器运行状态快照采集的核心硬件单元,其核心作用可概括为以下3点:

①实时捕获寄存器状态:触发后可精准采集FPGA内部各类寄存器的实时运行状态,覆盖范围包括:CLB内的触发器、移位寄存器查找表SRL、IOB的控制寄存器与数据寄存器、用户自定义逻辑中的核心寄存器(如状态机寄存器、数据缓存寄存器、计数寄存器等)。

②状态数据写入配置存储器:捕获到的寄存器状态不会直接对外输出,而是被并行写入FPGA的配置存储器(与配置比特流数据共存),成为配置存储器的一部分,后续可通过回读接口(JTAG/SelectMAP/ICAPE2)读取这些状态数据。

③灵活的硬件触发控制:原语通过CAP输入引脚触发捕获动作。当CAP输入检测到有效边沿(通常为上升沿)时,会立即执行一次寄存器状态的快照式捕获;触发时机可由用户逻辑精准控制(如故障触发信号、定时信号、关键操作完成信号到来时触发)。

2)应用方式

①在设计中实例化CAPTUREE2原语,将CAP输入引脚连接到调试触发信号(如定时信号、错误标志信号、手动触发按钮信号)。触发信号到来时,原语捕获目标寄存器的实时状态并写入配置存储器。通过JTAG/SelectMAP接口回读配置存储器数据,提取捕获的寄存器状态,对比预期值分析错误根源(如状态机跳变异常、数据缓存错位、IO寄存器采样错误)。无需外接调试硬件,利用FPGA内置资源实现无侵入式调试(仅占用少量配置存储器资源,不影响核心逻辑运行)。

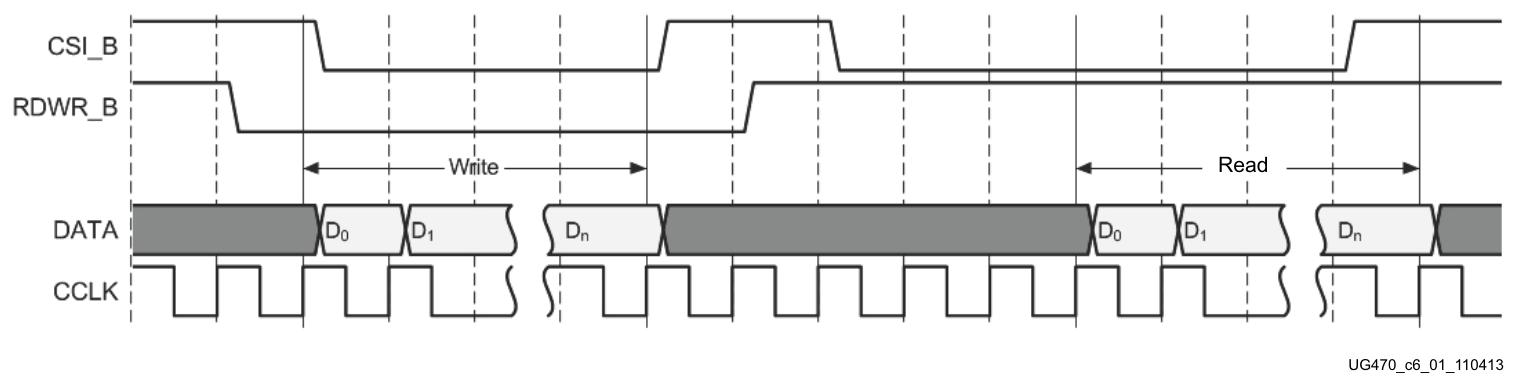

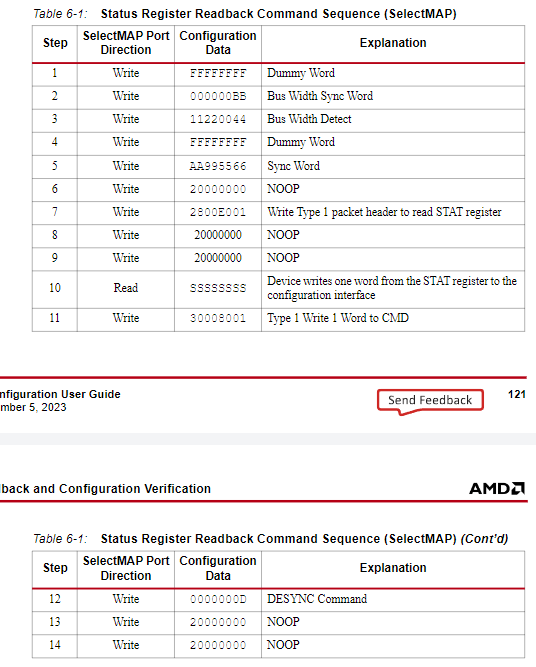

d)回读命令序列

1)通过SelectMAP接口访问配置寄存器:若要通过SelectMAP接口读取配置存储器,需先将接口设置为写控制模式,向FPGA下发命令;随后切换至读控制模式,从器件中读取数据。SelectMAP接口的读写控制由RDWR_B输入引脚决定:当接口为写控制模式时(RDWR_B = 0),SelectMAP数据引脚为输入状态;当接口为读控制模式时(RDWR_B = 1),数据引脚为输出状态。注意:在切换RDWR_B信号状态前,必须先撤销CSI_B信号(CSI_B = 1),避免触发中止操作。SelectMAP接口在写控制与读控制模式间切换的流程如下:

撤销CSI_B信号→切换RDWR_B信号状态→置位CSI_B信号(CSI_B与RDWR_B信号均需与配置时钟CCLK同步。回读过程中,CSI_B信号置位后,回读数据会经过3个时钟周期的确定性延迟后输出有效。)

2)配置寄存器读取流程(SelectMAP接口):最简单的读取操作针对COR0、STAT等支持读访问的配置寄存器(并非所有配置寄存器都开放读权限)。具体流程:向器件写入总线宽度检测序列与同步字,之后至少写入1个空操作指令(NOOP)→向器件写入读取STAT寄存器的1类包包头→向器件写入2个空操作指令,刷新包缓冲区→从SelectMAP接口读取1个32位字,该数据即为STAT寄存器的当前值→向器件写入解除同步DESYNC命令→向器件写入2个虚拟字,刷新包缓冲区。

需在步骤8与步骤9之间,将SelectMAP接口从写控制模式切换为读控制模式;步骤9完成后,需将接口切回写控制模式。

3)配置存储器读取流程(SelectMAP接口):从FDRO寄存器(Frame Data Register, Output,帧数据输出寄存器)读取配置存储器数据的流程,与读取其他寄存器的流程类似,但需增加额外步骤以适配配置逻辑的要求。从FDRO寄存器输出的配置数据会经过帧缓冲区,因此回读得到的第一帧数据需丢弃。具体流程如下:向器件写入总线宽度检测序列与同步字→向器件写入至少1个空操作指令(NOOP)→向器件写入关闭SHUTDOWN命令,之后写入1个空操作指令→向命令寄存器CMD写入重置CRC命令,之后写入1个空操作指令→向器件写入5个空操作指令,确保关闭序列执行完成(关闭序列执行期间,DONE引脚会拉低)→向命令寄存器CMD写入读取配置数据RCFG命令,之后写入1个空操作指令→向帧地址寄存器FAR写入起始帧地址(通常为0x00000000)→向器件写入读取FDRO寄存器的1类包包头→向器件写入32个虚拟字,刷新包缓冲区→从SelectMAP接口读取FDRO寄存器数据,读取长度与步骤8的计算值一致(回读过程中,CSI_B信号置位后,数据会经过3个时钟周期的确定性延迟后输出有效)→向器件写入1个空操作指令NOOP→向器件写入启动START命令,之后写入1个空操作指令→向器件写入重置CRC命令,之后写入1个空操作指令→向器件写入解除同步DESYNC命令→向器件写入至少64比特的空操作指令,刷新包缓冲区;持续发送CCLK时钟脉冲,直至DONE引脚拉高。

4)通过JTAG接口访问配置寄存器:7系列FPGA的配置逻辑支持通过JTAG接口访问,对应的交互载体为JTAG CFG_IN与CFG_OUT寄存器。这两个寄存器并非配置寄存器,而是与旁路寄存器Bypass、边界扫描寄存器Boundary同类的JTAG专用寄存器。移入CFG_IN寄存器的数据会被发送至配置包处理器,其处理方式与来自SelectMAP接口的命令完全一致。向配置逻辑下发回读命令时,需通过CFG_IN寄存器传输;读取配置存储器数据时,则需从CFG_OUT寄存器移出。

e)FDRO(Frame Data Register, Output,帧数据输出寄存器)

1)FDRO是7系列FPGA中只读的配置存储器读取专用寄存器,是配置存储器数据输出的唯一通道,核心功能可概括为2点:

①关联帧地址,读取整帧数据:FDRO需与FAR(帧地址寄存器) 配合使用,FAR用于指定待读取配置帧的地址,FDRO则输出该地址对应配置帧的全部数据(每帧固定为101个32位字)。

②适配多接口输出:通过SelectMAP、JTAG、ICAPE2接口读取配置存储器时,所有配置帧数据均需通过FDRO输出,是配置存储器与外部读取接口的桥梁。

2)帧缓冲区是FDRO与配置存储器之间的帧级数据暂存与同步单元,其作用可拆解为3点:

①适配配置存储器的帧结构:7系列FPGA配置存储器的最小可寻址单元是帧(每帧101个32位字),而非单个字节或字。帧缓冲区的作用是暂存整帧配置数据,确保每次读取的是完整的帧数据,避免出现半帧读取的情况。

②时序同步与帧边界对齐:配置存储器的读取操作需严格对齐帧边界,帧缓冲区可缓冲一帧数据,抵消配置存储器读取与外部接口传输的时序差异,保证输出数据的帧边界准确(比如避免跨帧数据混淆)。

③过滤初始无效数据:读取FDRO时需丢弃第一帧数据,这是因为器件上电或回读启动时,帧缓冲区会先输出一帧虚拟数据,用于初始化缓冲区状态,确保后续输出的是有效配置帧数据。

3)包缓冲区是FPGA配置包处理器(Configuration Packet Processor) 内部的专用数据缓冲单元,用于暂存配置包(Type1包、Type2包)的头部与数据段,核心作用与细节如下:

①保障配置包的完整接收与解析:7系列FPGA的所有配置命令(如读写寄存器、读写配置帧)均以配置包的形式传输,包缓冲区用于暂存包的包头(如操作码、地址、字计数)和数据段,确保包处理器能完整读取包的所有内容,避免因接口传输速率波动导致的包数据丢失或乱序。

②实现命令的流水线式处理:包缓冲区可缓存多个配置包,使包处理器能并行化处理命令。比如在上一个包未完全执行时,即可接收下一个包的内容,提升配置命令的执行效率。

③通过刷新确保命令执行完毕:文档中多次提到写入NOOP命令刷新包缓冲区,其本质是NOOP命令会触发包处理器清空缓冲区,确保之前下发的配置包被完全解析和执行,避免缓冲区残留数据干扰后续命令。

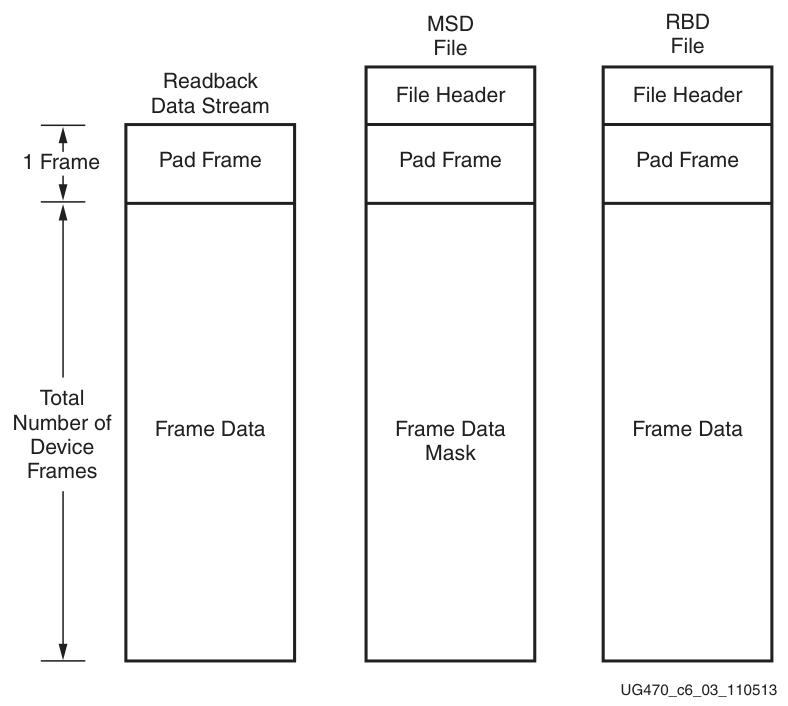

验证回读数据

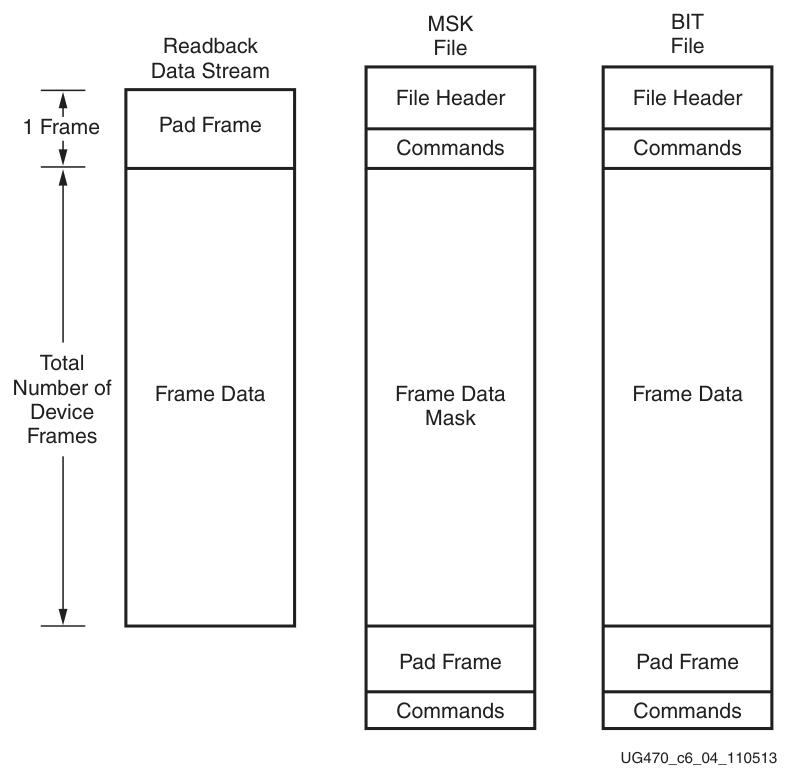

a)回读数据流包含配置帧数据,其开头会附带一帧填充数据,这一点与《配置存储器读取流程(SelectMAP接口)》中的描述一致。回读数据流不包含配置比特流中的任何命令或包信息,且回读过程中不会执行CRC校验操作。

b)回读数据的验证方式为:将回读数据流与烧录到器件中的原始配置帧数据进行比对。需要注意的是,回读数据流中的部分比特无需参与比对,这些比特通常对应用户侧存储单元,例如块随机存储器、分布式随机存储器、移位寄存器查找表、动态可重配置端口存储器、空存储单元。回读数据流中无关位的位置信息由掩码文件(MSK格式与MSD格式)提供。这两种文件的格式不同,但包含的核心信息完全一致。文件中值为1的比特位,即代表回读数据流中无需参与比对的无关位。

c)从器件获取回读数据后,可通过以下两种方式完成验证:

1)与黄金回读文件RBD比对,结合MSD掩码文件使用:验证回读数据流最简便的方法,是将其与黄金回读文件RBD进行比对,并通过MSD文件对回读比特进行掩码处理。这种方法的便捷性体现在:回读数据流的起始位置,与RBD文件、MSD文件的起始位置完全一一对应,大幅降低了回读数据、掩码数据与预期数据的对齐难度。RBD文件与MSD文件均为ASCII格式,包含回读数据、掩码数据的文本化表示,同时附带文件头信息(如文件名等)。验证时需忽略或删除这些文件头内容,文件中的 ASCII 字符 "1" 和 "0",分别对应器件输出的二进制回读数据。

2)与配置比特流文件BIT比对,结合MSK掩码文件使用:另一种验证方法为将回读数据流,与原始配置比特流中FDRI写操作对应的帧数据进行比对,并通过MSK文件对回读比特进行掩码处理。向器件下发回读命令后,验证流程的执行步骤如下:将回读帧数据的起始位置,与 BIT文件、MSK文件中FDRI写操作的起始位置进行对齐;持续比对,直至覆盖BIT文件中FDRI写操作的全部数据范围后停止。

重配置及多启动功能

a)概述

1)7系列FPGA的多启动与降级功能支持对现场系统进行更新,可实现比特流镜像的动态现场升级。其中,多启动功能允许在多个镜像之间实时切换;当多启动配置过程中检测到错误时,FPGA可触发降级功能,确保将经过验证的可靠设计加载到器件中。

2)当降级功能触发时,器件会执行以下操作:

①生成一个内部脉冲,重置整个配置逻辑(专用多启动逻辑、热启动起始地址寄存器WBSTAR、启动历史状态寄存器BOOTSTS除外);

②拉低INIT_B与DONE引脚;

③清空配置存储器;

④将版本选择引脚RS置为00,并从地址0重启配置流程;

⑤完成重置后,新加载的比特流会覆盖WBSTAR寄存器中的起始地址。

3)降级触发条件:IDCODE错误、CRC错误、看门狗定时器超时错误、BPI地址计数器环绕错误。此外,用户也可通过设置比特流选项ConfigFallback手动启用降级功能。需要注意的是,在降级配置过程中,嵌入式IPROG命令会被忽略,看门狗定时器也会被禁用;若降级配置仍失败,配置流程将直接终止,INIT_B与DONE引脚会持续保持低电平。

4)要实现一套可靠的在系统更新方案,需依次完成以下决策与操作:

①确定系统部署的实现方式;

②针对目标配置模式,添加对应的设计考量;

③综合考虑HDL设计的相关约束,并正确生成所需文件。

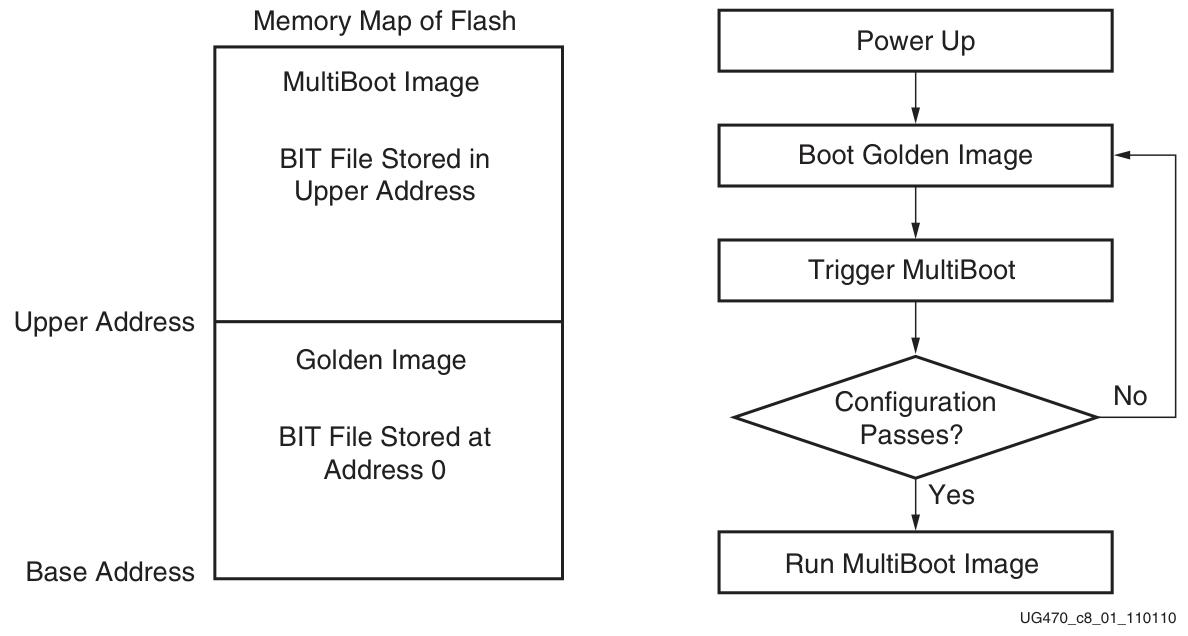

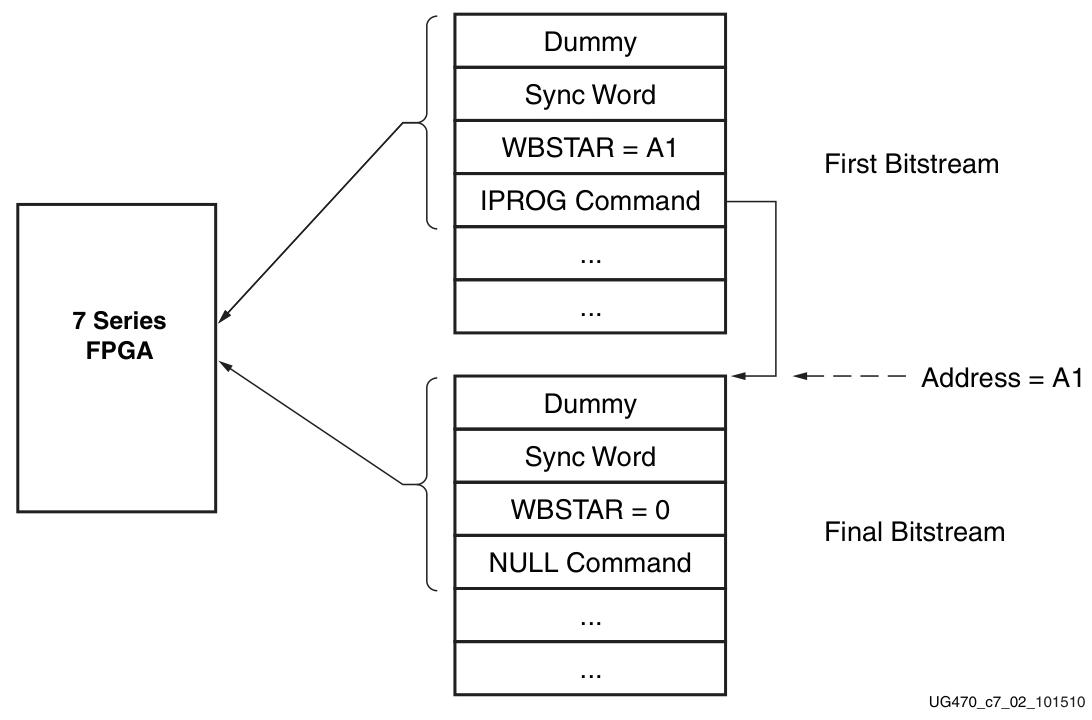

b)黄金镜像初始系统设置

1)上电时,黄金镜像从地址空间0处加载。随后,黄金镜像设计会触发多启动镜像的加载流程。当系统需要在加载运行时镜像前执行初始自检时,该步骤尤为实用。可将系统自检或诊断功能集成在黄金镜像中,而将运行时业务逻辑部署在多启动镜像内。上电后,黄金镜像始终会被优先加载,再由该镜像触发从高地址空间启动多启动镜像的流程。系统中可同时存储多个多启动镜像,且任意一个镜像均能触发其他镜像的加载。若从高地址空间加载多启动镜像的过程中出现错误,降级电路会触发黄金镜像从地址0处重新加载。

→

黄金镜像上电自检针对FPGA自身运行的必备条件,是所有自检的第一步,失败后直接终止多启动镜像加载。典型检查项:电源电压合规性检测、温度异常检测、时钟锁定状态检测(监测MMCM的LOCK引脚状态,若上电后100ms内LOCK引脚未置高,判定为时钟故障;此时可尝试切换备用时钟源,若备用时钟仍无法锁定,则保持黄金镜像运行并上报故障)。

c)黄金镜像与多启动镜像的设计要求

1)硬件层面无特殊要求,但在BPI模式下使用RS[1:0]引脚进行地址控制时除外,具体可参考BPI 模式,硬件RS引脚设计考量章节。

2)需在黄金镜像中嵌入IPROG命令,用于指定下一个配置地址;也可在黄金镜像设计中通过ICAPE2接口下发代码,间接执行IPROG命令。

3)需在比特流中配置WBSTAR寄存器的跳转地址,或通过ICAPE2接口设置该寄存器。

4)多启动镜像必须存储在闪存中,且存储地址需与WBSTAR寄存器配置的地址一致。

5)需启用看门狗定时器,以便在比特流未完全编程时实现故障恢复。

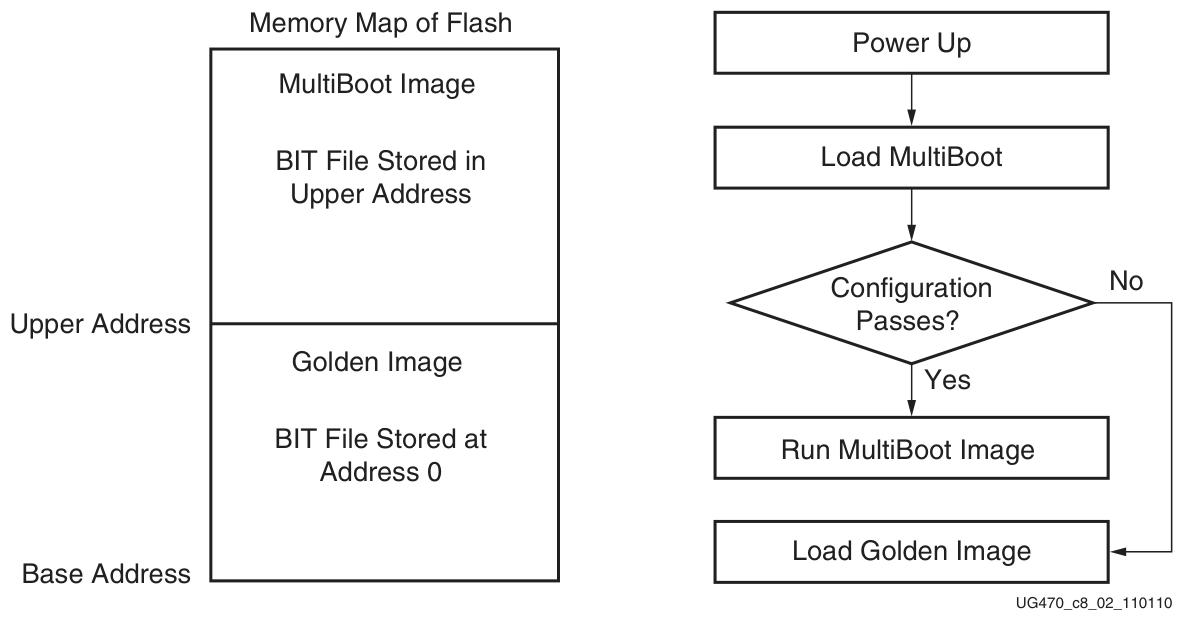

d)多启动镜像初始系统设置

1)另一种启动方案为:上电时直接从高地址空间加载多启动镜像。若该镜像配置失败,器件会自动触发降级机制,从地址0处加载黄金镜像。该方案可支持系统自主完成比特流升级,并实现上电后直接启动最新版本镜像。系统完成升级操作后,可触发自身重新加载最新版本的多启动镜像。若多启动镜像加载失败,降级逻辑会保障系统恢复至黄金镜像运行,黄金镜像则可修复闪存中的错误数据,并再次触发多启动镜像的加载流程。

e)多启动功能的设计考量

1)黄金镜像的设计考量

①比特流中WBSTAR寄存器的配置地址需指向多启动镜像的存储位置。

②需嵌入IPROG命令,确保上电后触发多启动镜像的加载。

③需启用配置定时器。

④若需实现黄金镜像修复闪存并重新触发多启动镜像加载的功能,可在设计中实例化ICAPE2接口,并编写代码以下发IPROG命令。

⑤在SPI配置模式下,黄金镜像的降级加载流程始终采用x1总线宽度。

⑥在BPI配置模式下,黄金镜像的降级加载流程始终采用异步读取模式,因此比特流中配置的同步读取模式参数BPI_sync_mode被忽略。基于此,黄金镜像中配置时钟CCLK的频率参数ConfigRate或ExtMasterCclk_en,必须满足异步读取操作的系统性能要求。

2)多启动镜像的设计考量

①需启用配置定时器。

②若需实现多启动镜像自主完成闪存升级并重新加载新版镜像的功能,可在设计中实例化ICAPE2接口,并编写代码以下发IPROG命令。

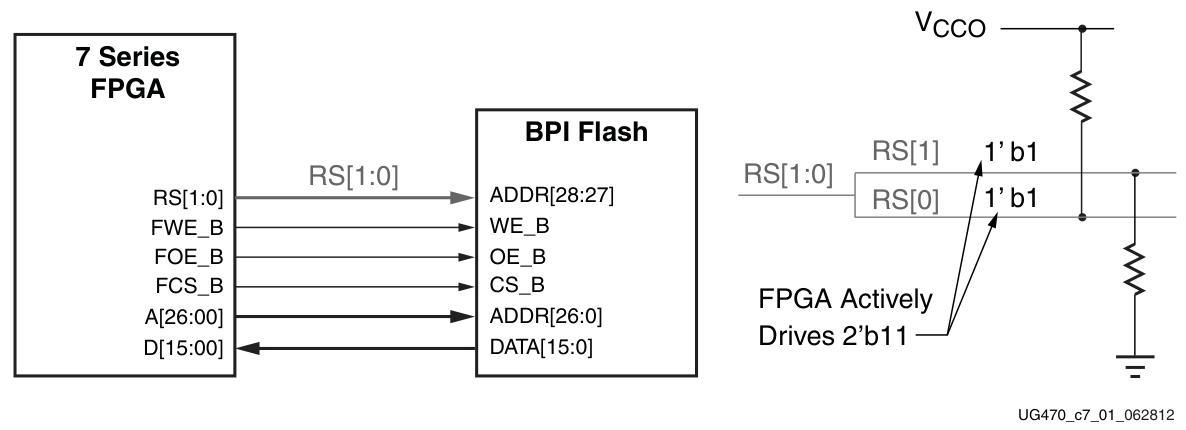

f)BPI模式(硬件RS引脚设计考量)

1)在BPI配置模式下,需将RS引脚与高位地址线相连,且需为其中一个RS引脚配置上拉电阻,使其与某条高位地址线绑定。采用该硬件设计方案后,系统无需依赖WBSTAR寄存器配置的地址,且各镜像对应的比特流选项保持一致。

g)多启动与降级功能的流程细节

1)FPGA的多启动与降级机制会涉及器件内部多个配置组件。

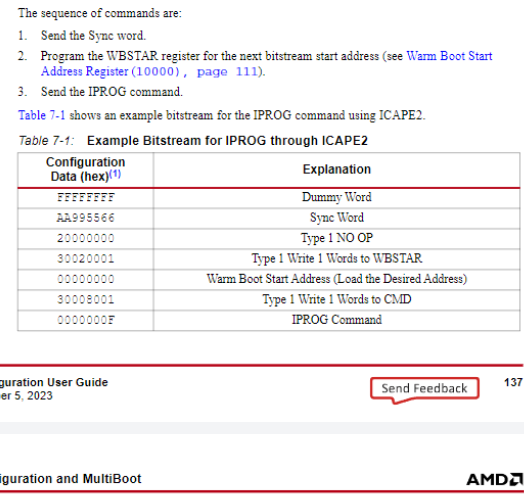

2)IPROG命令

①内部编程命令IPROG的功能,是PROGRAM_B引脚脉冲触发功能的一个子集。二者的核心区别在于:IPROG命令不会擦除WBSTAR、TIMER、BSPI、BOOTSTS寄存器,这些寄存器正是实现多启动与降级功能的关键。

②当IPROG命令下发后,器件会触发初始化流程,INIT与DONE引脚均会拉低,随后器件会尝试重新配置。

③该命令的下发方式有两种

i)通过ICAPE2接口下发:由用户逻辑控制ICAPE2接口,实现器件重配置的自主触发,适用于需要灵活切换镜像的场景;

ii)嵌入比特流中下发:在比特流生成阶段,将IPROG命令嵌入黄金镜像的比特流头部。上电后,器件从闪存读取黄金镜像比特流时,会先加载WBSTAR寄存器配置与IPROG命令;IPROG命令随即触发器件从WBSTAR指定的地址重新加载镜像。若高地址空间的多启动镜像加载失败,器件会再次从基地址0加载黄金镜像。此时配置控制器会检测到错误,自动跳过IPROG命令的执行。降级触发后,IPROG命令的处理流程会被阻塞,器件会持续加载并运行黄金镜像。待黄金镜像配置成功后,可再次下发IPROG命令,触发多启动镜像的加载流程。

④ICAPE2(Internal Configuration Access Port E2)是7系列FPGA内置的内部配置访问接口,核心作用是允许FPGA用户逻辑直接访问配置控制器,实现运行时动态配置管理,是软件层面控制MultiBoot、重配置的核心接口。主要功能包括:读写配置寄存器(如向CMD寄存器下发IPROG命令、修改WBSTAR寄存器的启动地址、读取STAT寄存器的配置状态)、触发动态重配置(通过下发IPROG命令,无需外部触发PROGRAM_B引脚,即可实现运行时镜像切换)、配置数据交互(向FDRI寄存器写入配置数据,或从FDRO寄存器读取配置存储器内容,支持部分重配置Partial Reconfiguration)、安全与状态监控(读取器件DNA、BOOTSTS寄存器的启动历史,实现硬件鉴权与故障溯源)、安全与状态监控(读取器件DNA、BOOTSTS寄存器的启动历史,实现硬件鉴权与故障溯源)。

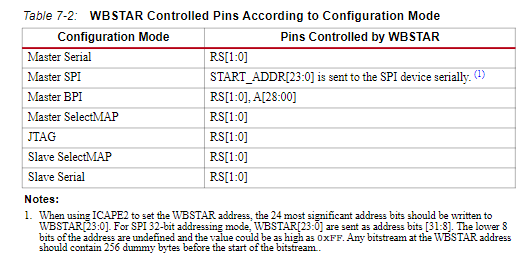

3)WBSTAR寄存器(Warm Boot Start Address)

①热启动起始地址寄存器WBSTAR的作用是:存储IPROG命令触发后,配置控制器需跳转的启动地址。该地址既可以是具体的闪存地址,也可以是RS引脚的电平配置值。

②WBSTAR寄存器的配置方式有两种:一是在比特流生成时预设值;二是通过ICAPE2接口动态写入。若比特流中未配置该寄存器,其默认值为全0。因此,当黄金镜像配置WBSTAR值并触发多启动流程后,若多启动镜像的比特流未重新配置WBSTAR,该寄存器会被默认重置为0。

③上电时,器件默认从闪存地址0开始读取比特流;当WBSTAR寄存器配置完成且IPROG命令下发后,配置控制器会从WBSTAR指定的地址发起读取操作。

4)看门狗定时器

①看门狗定时器支持两种互斥的工作模式:配置监控模式、用户逻辑监控模式。

i)配置监控模式:该模式下,定时器的超时值在比特流中预设,且该值不仅用于当前比特流的配置过程,还适用于所有由IPROG命令触发的后续镜像加载流程。因此,所有镜像的比特流均需配置看门狗定时器的超时值。定时器从比特流开始加载时启动倒计时,直至启动序列结束后自动禁用。若倒计时归0时配置仍未完成,器件会触发降级机制。需要注意的是,PLL锁定等待、DCI阻抗匹配等设置会延长启动序列的时长,配置超时值时需将这些延迟因素纳入考量。看门狗定时器的计数时钟频率约为65MHz。对于配置未启动、或启动后因比特流无效/损坏导致无法完成的场景,看门狗定时器可确保器件在一段合理的延迟后自动重试配置,提升系统的容错能力。

ii)用户逻辑监控模式:该模式用于监控用户逻辑的运行状态,与配置监控模式互斥,启用后仅对用户逻辑的异常进行检测与处理。

5)RS引脚(Revision Select,版本选择)

①RS引脚为双重功能引脚,默认处于禁用状态。其工作特性如下:在BPI或主模式SelectMAP配置下,降级触发时RS引脚会主动拉低;在 SPI配置模式下,降级触发时RS引脚不会拉低。

②对于初始多启动系统,RS引脚需与闪存的高位地址线相连,并通过上拉或下拉电阻将引脚电平固定为高或低。上电时,系统会根据RS引脚的电平配置与地址线的连接关系,从对应的高地址空间启动镜像;降级触发时,RS引脚拉低,器件会从基地址0加载黄金镜像。为确保每个存储段都能完整存放一份比特流文件,建议将RS引脚与系统定义的高位地址线绑定。

③RS引脚是Xilinx 7系列FPGA针对MultiBoot与Fallback功能设计的双重功能硬件引脚,核心作用是硬件层面的启动地址选择,无需依赖寄存器配置,直接通过引脚电平定义上电或降级时的启动镜像地址。属于配置模式辅助引脚,默认处于禁用状态,与MultiBoot功能强关联,不参与常规配置流程,仅影响镜像启动的地址选择。不同配置模式下,降级触发时的引脚行为不同:

i)BPI/主模式SelectMAP:降级触发时,RS引脚会主动拉低,强制器件从地址0加载黄金镜像;

ii)SPI模式:降级触发时,RS引脚不会主动拉低,地址选择完全依赖WBSTAR或默认地址0。

④硬件接线要求:将RS引脚(通常为2个,RS[1:0])直接连接到闪存的高位地址线(如SPI/BPI闪存的A20、A21引脚),为RS引脚配置上拉/下拉电阻,电阻值一般选择 10kΩ。

⑤上电启动阶段:上电时,FPGA采样RS引脚的硬件电平,该电平直接映射为闪存的高位地址值。配置控制器根据高位地址 + 基地址,确定启动镜像的存储区间,实现硬件静态寻址。例如RS[1:0]=01绑定A20=1,若黄金镜像存在0x000000-0x0FFFFF,多启动镜像存在 0x100000-0x1FFFFF,则上电直接加载0x100000起始的多启动镜像。当配置过程中出现CRC错误、IDCODE错误等故障时,FPGA触发Fallback机制,在BPI/主模式SelectMAP下,FPGA会主动拉低RS引脚,覆盖硬件电阻的电平配置,强制映射到高位地址00,配置控制器从地址0启动,加载黄金镜像,实现故障自动降级。

IPORG重配置

a)概述

1)内部编程命令IPROG与触发PROGRAM_B引脚脉冲的效果类似,核心区别在于:IPROG命令不会重置专用重配置逻辑。重配置过程中,器件会采用热启动起始地址寄存器WBSTAR中设置的启动地址,而非默认地址,在BPI与SPI配置模式下,默认启动地址为0。

2)IPROG命令的下发方式有两种:一是通过ICAPE2接口下发,二是直接嵌入比特流中。注意:ICAPE2接口的通信协议与SelectMAP接口类似,因此输入配置总线的数据需执行位序交换操作,有关ICAPE2接口的更多详情,可查阅《Vivado设计套件7系列FPGA和Zynq-7000 SoC库指南》(UG953);ICAPE2接口的最高工作频率FICAPCK参数可参考7系列器件数据手册。

b)基于ICAPE2接口的IPROG命令下发

1)IPROG命令也可通过实例化ICAPE2原语来下发。器件配置成功后,用户逻辑可先确定下一个比特流的启动地址并配置WBSTAR寄存器,再通过ICAPE2接口下发IPROG命令。

2)具体命令序列如下:发送同步字→向WBSTAR寄存器写入下一个比特流的启动地址→发送IPROG命令。

3)当配置逻辑接收到IPROG命令后,FPGA会重置除专用重配置逻辑外的所有模块,INIT_B与DONE引脚随之拉低。待FPGA清空所有配置存储器后,INIT_B引脚会重新拉高,随后器件将以WBSTAR寄存器中配置的地址作为比特流起始地址,启动重配置流程。哪些引脚由WBSTAR寄存器控制,取决于当前的配置模式。除SPI模式外,其余所有配置模式下的RS[1:0]引脚均受WBSTAR寄存器控制;而WBSTAR寄存器中的START_ADDR字段仅在BPI与SPI模式下有效。→WBSTAR的核心作用是指定重配置的启动地址/引脚电平,但它能控制哪些引脚,完全由当前FPGA的配置模式决定,可分为两类场景:①SPI模式:WBSTAR存储的24位地址会串行发送给SPI闪存,直接指定新镜像的存储位置;RS[1:0] 引脚不受控制,降级时也不会主动拉低;②非SPI模式(主串行/BPI/SelectMAP/JTAG等):WBSTAR配置的RS[1:0]电平会覆盖外部上拉/下拉电阻的硬件配置,强制选择对应的闪存高位地址段,实现镜像切换。→IPROG命令负责触发重配置流程,WBSTAR负责指定重配置的目标位置,但WBSTAR的指定方式(控地址/控引脚)和地址字段是否有效,完全由配置模式决定。

4)

通过ICAPE2接口配置WBSTAR地址时,需将地址的24位最高有效位写入WBSTAR[23:0]。在SPI 32位寻址模式下,WBSTAR[23:0]会被映射为地址位[31:8];地址的低8位为未定义状态,其值最大可达0xFF。因此,存储在WBSTAR指定地址的比特流,需在有效数据前添加256字节的虚拟数据。

5)

除CCLK引脚外,所有BPI相关引脚均为多功能I/O引脚。当配置完成(DONE引脚拉高)后,这些引脚会切换为用户侧I/O引脚,用户逻辑可通过这些引脚访问BPI闪存,实现用户数据的存储与编程操作。

c)比特流嵌入IPROG命令

1)用户可将WBSTAR寄存器配置信息与IPROG命令直接嵌入比特流中。具体实现方案如下:

①在BPI或SPI模式下,将一个可靠的比特流(黄金镜像)存储在地址0处;

②后续如需向闪存中添加新的应用比特流,只需修改存储在地址0处的原始比特流,更新其中的WBSTAR寄存器配置值与IPROG命令;

③修改完成后,FPGA上电会直接加载新的应用比特流;若新比特流加载失败,器件会触发降级机制,重新加载地址0处的原始比特流。

2)AMD开发工具会在每个7系列FPGA比特流中,自动添加一条向WBSTAR寄存器写入空数据的指令,同时为IPROG命令预留一个占位符。用户可根据需求修改该占位符,例如:将WBSTAR寄存器的配置值修改为目标启动地址;将WBSTAR寄存器配置指令后的空命令NULL修改为IPROG命令,具体方法为将该命令的4位最低有效位全部置1。

降级与IPROG重配置的状态寄存器

a)7系列器件内置启动历史状态寄存器BOOTSTS,用于存储配置历史信息。该寄存器的工作机制类似于一个双项先进先出缓冲区FIFO:最新的配置状态会存入Status_0,而Status_0中原有的状态会移位至Status_1。Valid_0位用于标识Status_0中的其余状态位是否有效。

Status_1的状态表明:系统曾尝试执行IPROG重配置,且检测到该次加载的比特流存在CRC错误;

Status_0的状态表明:降级比特流已成功加载。此状态下IPROG位同样被置 1,原因是降级比特流中包含 IPROG 命令。尽管降级过程中该命令会被忽略,但状态寄存器仍会记录这一事件。

b)回退到黄金比特流的完整流程

1)错误检测:配置逻辑在加载新镜像过程中,检测到以下任意一种错误:CRC校验错误、IDCODE不匹配错误、看门狗定时器超时(若启用配置监控模式)、BPI地址计数器环绕错误(仅BPI模式);

2)硬件复位触发:配置逻辑生成内部复位脉冲,该脉冲仅重置除专用重配置逻辑(WBSTAR、BOOTSTS、TIMER等寄存器)外的所有模块;

3)引脚与内存状态切换:拉低INIT_B和DONE引脚,告知外部系统进入降级流程;清空内部配置存储器,清除新镜像的残留数据;

4)强制地址0启动:对于BPI/主SelectMAP模式,RS[1:0]引脚被硬件拉低,覆盖外部电阻的电平配置,强制映射到地址0;对于SPI模式,配置逻辑忽略WBSTAR的地址,直接从默认的地址0读取黄金镜像;

5)黄金镜像加载:FPGA从地址0加载黄金镜像,完成配置后DONE引脚拉高,系统恢复正常运行。

c)回退功能生效的前提条件

1)黄金镜像必须常驻地址0:地址0的黄金镜像需为经过严格验证的可靠版本,且存储区域无坏块、无数据损坏,确保降级时可正常读取;

2)启用降级功能配置:需在比特流中设置ConfigFallback选项,明确开启降级功能;若未配置该选项,新镜像加载失败后配置会直接终止,INIT_B和DONE引脚持续拉低;

3)专用重配置逻辑未损坏:WBSTAR、BOOTSTS等专用寄存器是降级机制的核心,若这些硬件逻辑损坏,系统无法触发降级流程;

4)看门狗定时器配置合理(可选):若启用看门狗的配置监控模式,需确保TIMER_VALUE的取值覆盖完整配置时长(包括DCI匹配、MMCM锁定的等待时间);超时时间过短会误触发降级,过长则无法及时响应真故障;

5)禁用比特流加密与安全限制:若黄金镜像或新镜像启用了加密功能,或配置了security:all等限制回读/重配置的安全选项,会导致降级流程无法执行。

看门狗定时器

a)概述

1)7系列FPGA的看门狗定时器可用于监控比特流配置过程或FPGA逻辑中的用户逻辑运行状态。当看门狗定时器超时,配置逻辑会自动加载降级比特流。

2)看门狗定时器采用专用内部时钟CFGMCLK的分频信号,该时钟的标称频率为65MHz。时钟信号会先经过256分频,因此看门狗定时器的时钟周期约为4000纳秒。看门狗计数器的位宽为30位,理论上支持的最大超时时间约为4230秒,具体超时值可通过比特流选项进行配置。

3)看门狗定时器的使能方式有两种:一是在比特流中预先配置;二是通过任意配置端口向TIMER寄存器写入配置值。注意:在降级重配置的过程中及完成后,看门狗定时器会被自动禁用;只有通过一次成功的降级重配置触发IPROG重配置,且该次IPROG重配置成功完成后,才能重新启用看门狗定时器。

b)加载监控模式

1)若需使用看门狗定时器监控比特流配置过程,需在比特流中向TIMER寄存器写入配置参数:将TIMER_CFG_MON位置1,并设置预期的TIMER_VALUE值。TIMER_VALUE的取值需满足覆盖FPGA从配置启动到启动序列完成的全部时长,包括启动阶段中因DCI阻抗匹配、MMCM时钟锁定、DONE信号释放等操作产生的等待时间。

c)用户监控模式

1)若需使用看门狗定时器监控用户逻辑运行状态,需在比特流中向TIMER寄存器写入配置参数:将TIMER_USR_MON位置 1,并设置预期的TIMER_VALUE值。用户必须在定时器超时前,通过下发LTIMER命令或直接写入TIMER寄存器的方式,持续重置看门狗计数器。当器件进入关闭状态或掉电状态(包括正常关机)时,看门狗定时器会自动禁用。

d)

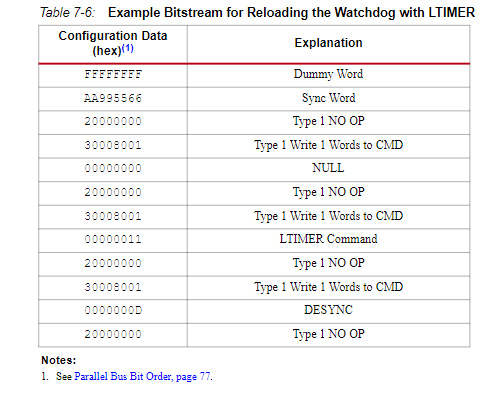

1)Dummy Word:总线同步与缓冲。用于初始化配置总线,抵消接口传输延迟,确保后续命令能被配置控制器正确识别,无实际功能含义,仅作为填充缓冲。

2)Sync Word:建立配置包同步。7系列FPGA配置包的标准同步标识,告知配置控制器后续数据为有效配置包,触发控制器进入包接收状态。

3)Type 1 NOOP:刷新包缓冲区。空操作指令,用于等待前序同步字生效,同时刷新配置包缓冲区,避免残留数据干扰后续命令解析。

4)Type 1 Write 1 Word to CMD:指定命令写入目标。1类包的包头指令,明确后续数据将写入命令寄存器CMD,且写入长度为1个32位字。

5)NULL:占位与缓冲。无实际功能的空命令,用于过渡缓冲,确保写命令与后续LTIMER命令之间的时序间隔满足要求。

6)Type 1 NOOP:等待命令执行。等待空命令写入完成,避免命令总线冲突,为后续LTIMER命令执行预留时序余量。

7)Type 1 Write 1 Word to CMD:再次指定CMD寄存器写入。重复步骤4的包头指令,明确后续LTIMER命令将写入CMD寄存器。

8)DESYNC:释放配置逻辑。释放配置控制器,允许回读CRC等其他配置功能访问配置逻辑;同时清除可能存在的CRC_ERROR标记。

回读CRC(Readback CRC)

a)概述

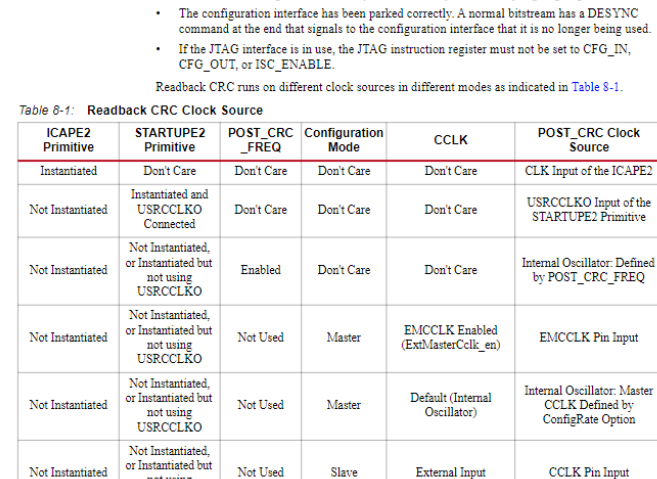

1)AMD 7系列器件支持在用户设计后台持续回读配置数据的功能。该功能旨在简化单粒子翻转SEU的检测。单粒子翻转会导致配置存储单元比特位翻转,且可与帧纠错码FRAME ECC功能配合使用,实现SEU纠错等高级操作。

2)启用回读CRC功能需将配置用户约束POST_CRC设置为Enable;启用后,配置专用逻辑会在后台持续执行回读操作,校验配置存储器内容的CRC值。回读频率可通过配置约束POST_CRC_FREQ自定义设定。

3)校验流程与错误处理

①多轮校验逻辑:首轮回读对纠错码ECC校验子位进行校准,为后续错误检测建立基准。次轮回读将计算出的CRC值锁存为黄金参考值,用于后续比对,也可通过将配置约束POST_CRC_SOURCE设置为PRE_COMPUTED,直接指定已知的黄金CRC值(无需器件自动计算)。后续回读每次回读时将实时计算的CRC值与黄金参考值比对,根据错误类型触发对应动作:

i)检测到单比特 / 双比特错误:ECCERROR信号产生脉冲,同时输出校验子SYNDROME、校验字SYNWORD、错误比特位SYNBIT、单比特错误标记ECCERRORSINGLE、帧地址寄存器FAR等详细错误信息。

ii)检测到CRC不匹配:FRAME_ECCE2原语的CRCERROR引脚拉高,随后INIT_B引脚拉低,DONE引脚保持高电平(标识配置未失效但存在错误)。

iii)可选配置:可通过将约束POST_CRC_INIT_FLAG设置为DISABLE,关闭INIT_B引脚作为回读CRC错误标记的功能。

iv)错误标记状态:若错误未被纠正,错误标记会保持有效,直至下一次CRC比对周期。

②功能暂停与自动恢复:当用户逻辑通过ICAPE2命令、JTAG接口、SelectMAP接口访问配置逻辑时,回读CRC功能会自动暂停,且错误标记会被清除;用户完成配置逻辑访问后,回读CRC功能无需手动重启,会自动恢复运行。

③错误处理动作配置:可通过配置用户约束POST_CRC_ACTION指定检测到错误后的处理策略,可选选项如下:Halt(暂停回读CRC功能,等待人工干预)、Continue(忽略错误,继续执行回读CRC功能)、Correct_And_Halt(纠正错误后暂停回读)、Correct_And_Continue(纠正错误后继续回读)。

b)单粒子翻转SEU检测

1)回读CRC逻辑需满足以下条件才能正常运行:

①所有配置操作必须以解除同步DESYNC命令结束,以释放配置逻辑的访问权限;若未下发DESYNC命令,回读CRC逻辑将无法访问配置逻辑,导致功能失效。此外,DESYNC命令会清除CRC_ERROR标记。

②JTAG 指令寄存器IR不得包含任何配置类指令(CFG_IN、CFG_OUT、ISC_ENABLE);只要这些指令存在,回读CRC逻辑就会被阻塞,无法运行。通过JTAG接口执行的所有配置操作,结束时需将IR加载为非上述三类配置指令的值。

2)后台回读的屏蔽存储单元:以下动态可修改的存储单元会在后台回读时被屏蔽(不参与CRC校验),避免干扰用户功能。

①SLICEM查找表(LUT,用作RAM或移位寄存器查找表SRL);

②BRAM:回读时跳过其内容,避免影响用户数据读写;BRAM可通过自身独立的ECC电路在运行时实现错误防护;

③动态可重配置端口DRP存储器。

3)启用回读CRC功能后,需同时满足以下条件,逻辑才会在配置完成后自动后台运行:

①FPGA配置成功(DONE引脚拉高,标识配置完成);

②配置接口已正确挂起:标准比特流的末尾会包含DESYNC命令,告知配置接口不再被占用;

③若使用JTAG接口,其指令寄存器不得设置为CFG_IN、CFG_OUT、ISC_ENABLE。

c)

回读CRC时钟源的选择优先级:ICAPE2时钟 → STARTUPE2 USRCCLKO → 外部专用时钟EMCCLK/CCLK → 内部振荡器,按是否实例化对应原语→是否启用外部时钟→是否自定义频率的顺序判断,无需复杂计算。

d)由于JTAG在配置模式中拥有最高优先级,因此它可在需要时随时占用配置总线。若仅打算通过JTAG执行配置,建议将M[2:0]引脚设置为主串行模式,确保内部振荡器提供持续时钟。同时,JTAG指令寄存器不得挂起在CFG_IN、CFG_OUT、ISC_ENABLE指令上。在部分重配置应用中,配置存储器的内容会发生变化,因此黄金特征值(golden signature)必须重新计算。器件硬件会在每次向FDRI寄存器写入数据后,自动重新生成黄金CRC值,确保后续回读校验的准确性。

d)SEU纠错功能

1)若通过约束POST_CRC_ACTION启用了纠错功能,回读CRC逻辑会对单比特错误执行自动纠正,具体流程如下:

①回读过程中,为每帧配置数据计算校验子位syndrome bits;

②检测到单比特错误时,立即停止当前回读操作;

③重新回读存在错误的帧数据;

④利用校验子信息定位错误比特位,修正错误后将正确数据写回该帧;

⑤纠错后的行为由POST_CRC_ACTION的配置决定:若设置为Correct_And_Continue回读逻辑从起始地址重新开始扫描;若设置为Correct_And_Halt纠错完成后回读逻辑停止运行。以下是POST_CRC_ACTION设置为Correct_And_Continue时,不同错误场景下硬件纠错逻辑的行为(回读CRC均从起始地址开始扫描):

i)单比特错误:读取到含错误比特的帧后,CRCERROR和INIT_B引脚置位,ECCERROR信号产生两次脉冲,纠错流程启动;错误比特修正后,ECCERROR、CRCERROR、INIT_B引脚恢复无效状态;回读CRC周期从起始地址重新开始。

ii)两个及以上不同帧存在错误:读取到第一个含错误的帧后,按场景1的逻辑完成纠错;回读CRC周期从起始地址重启,继续扫描直至读取到第二个含错误的帧;按场景1的逻辑修正第二个错误;若这是最后一个错误,回读CRC从起始地址恢复正常扫描;若仍有其他帧存在错误,重复。

iii)同一帧存在两个及以上错误: 读取到含多个错误的帧后,ECCERROR引脚置位;内置逻辑无法纠正同一帧中的多个错误,回读CRC继续扫描下一帧,ECCERROR状态根据当前帧的错误情况更新;当回读CRC扫描至最后一个地址时,CRCERROR引脚置位;回读CRC周期从起始地址重启,且CRCERROR标记保持置位状态;此时的回读行为由POST_CRC_ACTION的配置决定(如Halt则停止,Continue则继续扫描)。

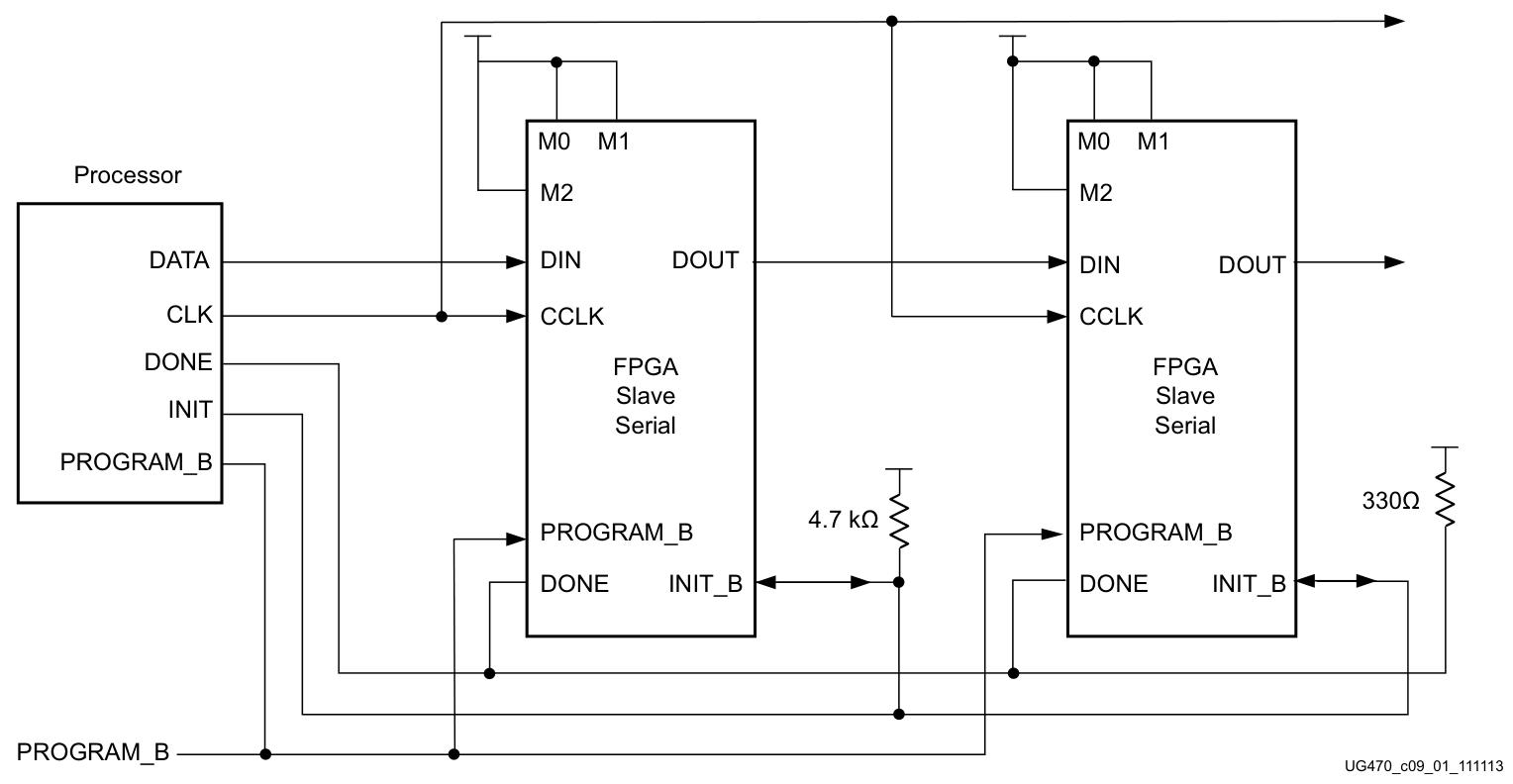

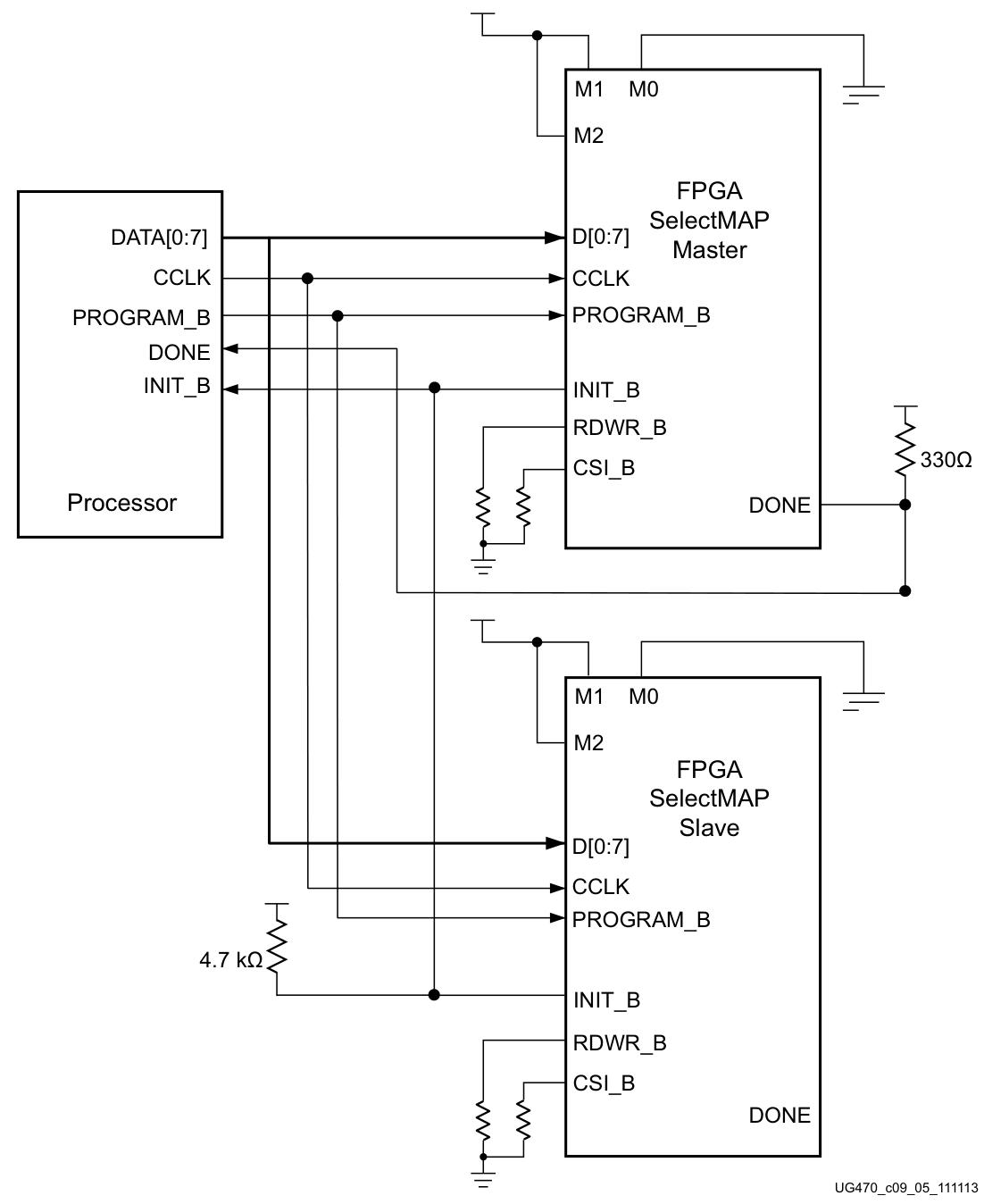

多FPGA配置

a)概述

1)在需要多个FPGA的应用中,所有器件可通过单一配置源进行配置。使用相同配置文件的FPGA可同时进行组播加载;使用不同配置文件的FPGA则可通过FPGA内置逻辑(菊花链方式)或外部逻辑依次加载。本章涵盖以下内容:串行配置模式、串行菊花链配置、组播串行配置、并行配置模式、多器件SelectMAP配置、并行菊花链配置、组播SelectMAP配置。

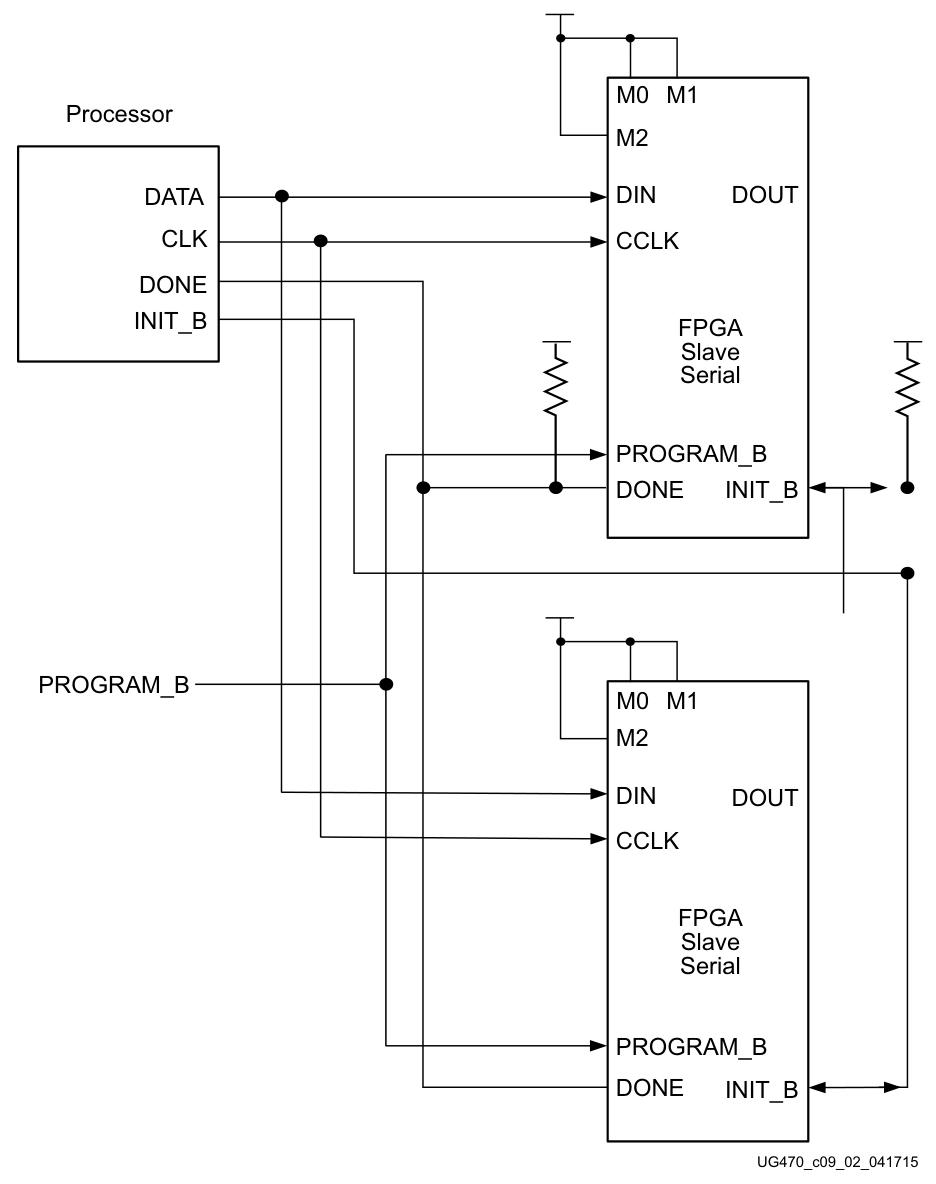

b)串行菊花链配置

1)多个7系列器件可通过串行菊花链连接,从单一配置源获取配置数据。在串行菊花链中,器件通过DIN引脚接收配置数据,并通过DOUT引脚将数据传递给下游器件。DOUT上的数据在CCLK的下降沿输出,下游器件在CCLK的上升沿捕获DIN上的数据。距离配置数据源最近的器件为最上游器件,最远的为最下游器件。

2)串行菊花链中,所有器件均需设置为从串行模式,配置时钟由外部提供。另一种方案是让第一个器件采用SPI模式,菊花链数据仍通过DOUT输出,但SPI菊花链不支持回退重配置功能。

3)

①DONE引脚为开漏输出,从串行菊花链中所有器件的DONE引脚必须连接在一起。

②INIT_B引脚为双向开漏引脚,需外接上拉电阻。

③比特流的启动时钟必须设置为CCLK(用于串行配置)。

4)串行菊花链中的第一个设备是最后完成配置的。CRC校验仅覆盖当前器件的数据,不包含链中其他器件。

5)当链中最后一个器件完成配置并通过CRC校验后,将进入启动序列。在启动序列的释放DONE引脚阶段,该器件会将其DONE引脚置于高阻态,同时链中倒数第二个器件进行配置。待所有器件均释放DONE引脚后,公共DONE信号会被上拉为高电平,或由链中第一个器件驱动为高电平。下一个CCLK上升沿到来时,所有器件将退出释放DONE引脚阶段,完成启动序列。

c)混合串行菊花链

1)7系列器件可与早期AMD Virtex和AMD Spartan系列器件构成混合串行菊花链。设计混合串行菊花链时,需注意以下关键事项:

①许多早期FPGA器件无法承受7系列器件生成的CCLK频率,需选择所有器件均支持的配置CCLK速度。

②7系列器件应始终置于串行菊花链的起始端,早期系列器件则置于链的末端。

③所有7系列器件家族均具备相似的比特流选项,只要条件允许,7系列FPGA比特流选项的相关指南应适用于串行菊花链中的所有器件。

④器件通过DOUT引脚传输的配置比特数存在限制:7系列及Virtex-II及后续系列Virtex器件的限制为4,294,967,264比特;Spartan-6和Spartan-3系列器件的限制为2,147,483,632比特。所有下游器件的比特流长度之和不得超过该数值。

d)串行菊花链的设计指南与注意事项

1)启动时序(GTS信号):全局三态信号GTS应在DONE信号置高前或同一时钟周期内释放,确保所有DONE引脚释放时,器件已处于可运行状态。

②连接所有DONE引脚:串行菊花链中所有器件的DONE引脚必须连接在一起,否则会导致配置失败。出于调试需求,建议设计可断开单个DONE引脚与公共DONE信号的机制,以便通过串行或JTAG接口对单个器件进行独立配置。

③DONE引脚上升时间:所有DONE引脚释放后,DONE信号应从逻辑0上升至逻辑1。若DONE信号上升需要额外时间,可为串行菊花链中的所有器件设置DonePipe选项。

e)组播串行配置

1)采用组播串行配置方案,可通过同一比特流同时配置多个器件。该方案中,所有器件的串行配置引脚短接在一起,确保每个器件接收相同的信号跳变。组播串行配置要求所有器件必须完全一致。配置可由外部配置控制器驱动,从闪存或其他存储器中读取比特流。

2)

①DONE引脚为开漏输出。

②INIT_B引脚为双向开漏引脚,需外接上拉电阻。

③串行配置的启动时钟必须设置为CCLK。

④组播串行配置要求所有器件完全一致(相同IDCODE),且需使用同一比特流进行配置。

3)组播串行配置的关键注意事项

①启动时序(GTS信号):全局三态信号GTS应在DONE信号置高前或同一时钟周期内释放,确保所有DONE引脚释放时,所有器件均已处于可运行状态。

②DONE引脚可断开:出于调试需求,建议设计可断开单个DONE引脚与公共DONE信号的机制。若所有器件均设置为从串行模式,即使DONE引脚断开,只要外部CCLK持续跳变直至所有DONE引脚置高,配置仍可正常完成。

③CCLK的板级布局设计:CCLK信号速率相对较低,但7系列FPGA输入缓冲器的边沿速率极快。即使CCLK信号存在轻微的信号完整性问题,也可能导致配置失败(典型故障现象:DONE引脚仍为低电平,INIT_B引脚为高电平)。因此,建议采用注重信号完整性的设计方案,包括使用IBIS模型进行信号完整性仿真。

④组播串行配置的PROM文件:组播串行配置所用的PROM文件与单个器件配置的PROM文件完全相同,无需特殊设计。

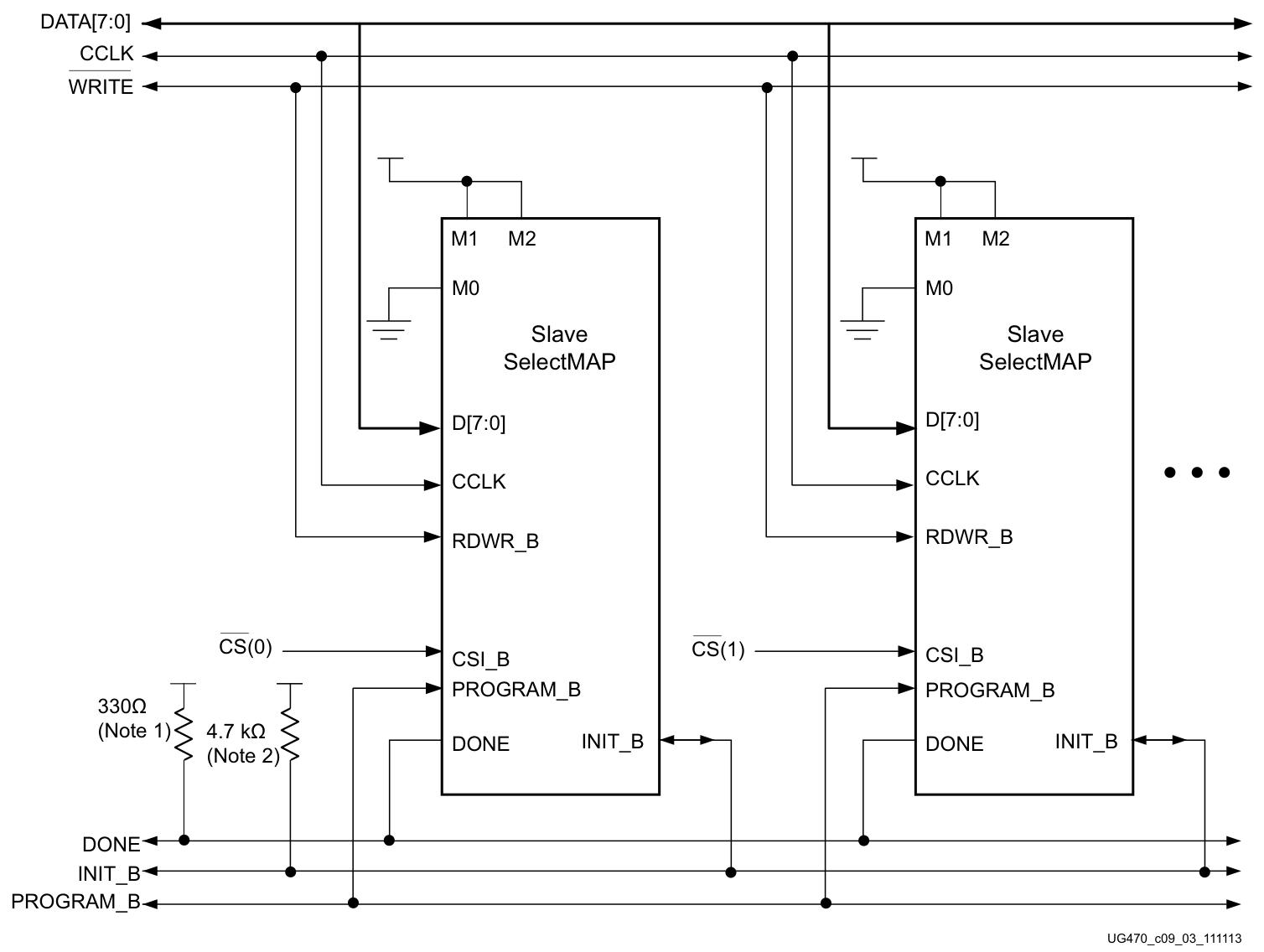

f)多器件SelectMAP配置

1)多个工作在从模式SelectMAP的7系列器件可连接到公共SelectMAP总线。在该总线架构中,所有器件的DATA、CCLK、RDWR_B、PROGRAM_B、DONE、INIT_B引脚共享公共连接;而为了实现单个器件的独立访问,CSI_B输入引脚不得短接在一起,需由外部控制器(通常是微处理器或CPLD)提供CSI_B信号控制。若配置后需对器件执行读回操作,需正确处理RDWR_B信号,否则,可将RDWR_B引脚直接拉低。

2)

①DONE引脚为开漏输出。

②INIT_B引脚为双向开漏引脚,需外接上拉电阻。

③不支持回退重配置功能。

④SelectMAP配置的启动时钟必须设置为CCLK。

⑤需外部控制器(如微处理器或CPLD)控制配置过程。

⑥数据总线宽度可为x8、x16、 x32位(适用于从模式SelectMAP)。

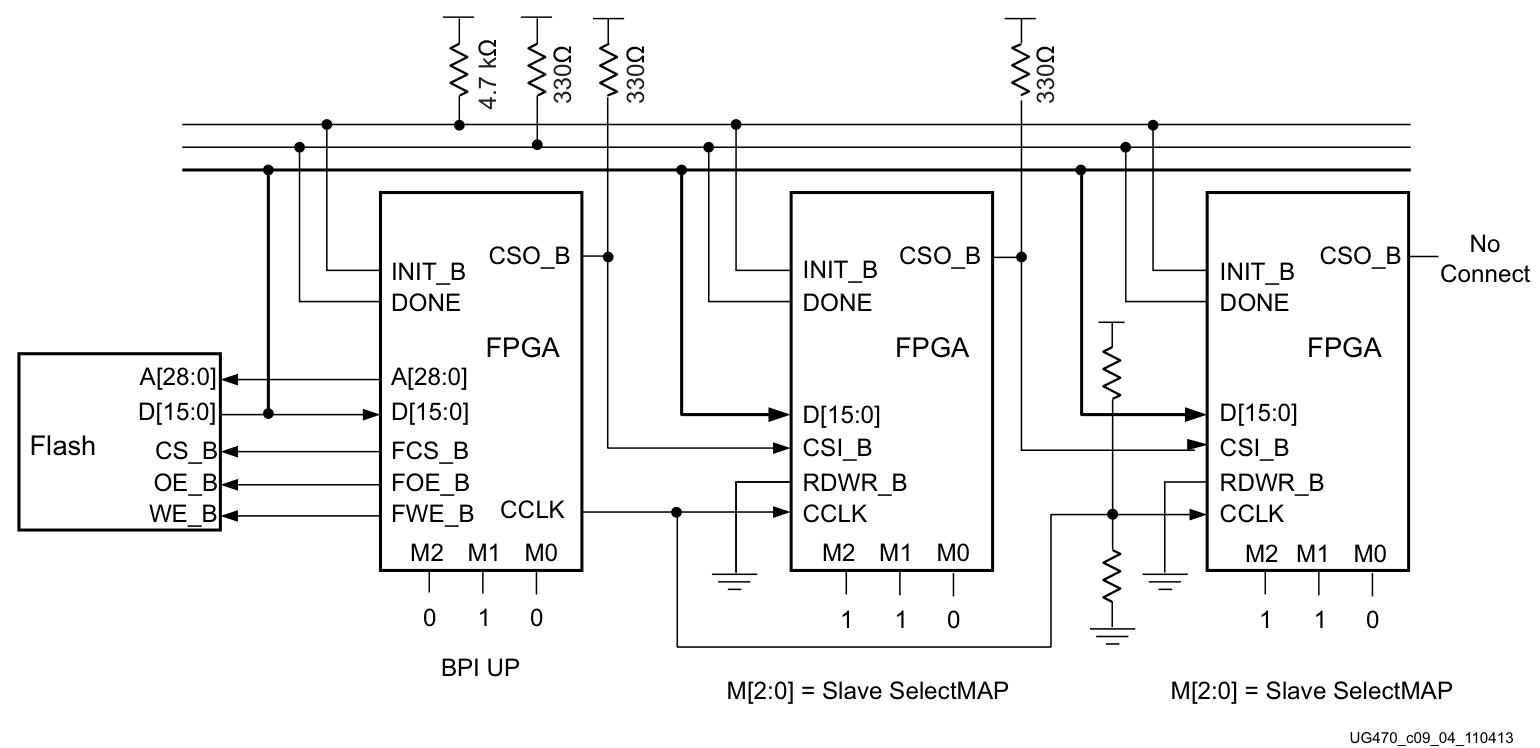

g)并行菊花链配置

1)7系列FPGA支持并行菊花链配置。领头器件也可工作在主模式/从模式SelectMAP。所有器件的D[15:00]、CCLK、RDWR_B、PROGRAM_B、DONE、INIT_B引脚共享公共连接,CSI_B引脚则采用菊花链连接。

2)

①DONE引脚为开漏输出。

②INIT_B引脚为双向开漏引脚,需外接上拉电阻。

③SelectMAP配置的启动时钟必须设置为CCLK。

④应启用FCS_B、FWE_B、FOE_B、CSO_B引脚的弱上拉电阻,否则需为每个引脚外接上拉电阻;默认情况下,所有多功能I/O引脚在配置后为弱下拉状态。

⑤链中第一个器件可为主模式SelectMAP、从模式SelectMAP、BPI模式,后续器件必须工作在从模式SelectMAP。

⑥并行菊花链方案不支持读回功能。

⑦不支持回退重配置功能。

h)组播SelectMAP配置

1)采用组播SelectMAP配置方案,可通过同一配置比特流同时配置多个器件。该方案中,两个及以上器件的CSI_B引脚需短接在一起(或直接拉低至地),使所有器件均能识别D引脚传输的配置数据。

2)若系统提供外部振荡器,所有器件均可设置为从模式SelectMAP。

3)

①不支持同步SelectMAP模式。

②不支持回退重配置功能。

③DONE引脚为开漏输出。

④INIT_B引脚为双向开漏引脚,需外接上拉电阻。

⑤SelectMAP配置的启动时钟必须设置为CCLK。

4)公共DONE信号需外接上拉电阻。由于该配置会增加信号扇出,设计人员必须重点关注信号完整性,建议通过仿真验证信号质量。此外,若CSI_B信号短接,所有器件会同时尝试驱动数据总线,因此无法实现读回功能。

高级JTAG应用

a)概述

1)7系列器件支持IEEE测试访问端口与边界扫描架构标准(IEEE Std 1149.1)及高级数字网络边界扫描标准(IEEE 1149.6)。联合测试行动小组(JTAG)是最初负责制定该标准的技术小组,该标准可确保板级层面各组件及其互连的完整性。

2)随着PCB的密度不断提高,以及更复杂的表面贴装技术的应用,边界扫描测试已成为广泛应用的重要调试工具。具备边界扫描逻辑的器件可通过I/O引脚输出数据,用于测试板级器件间的连接;该电路还可内部发送信号,用于测试器件特定行为。这类测试常用于检测板级和器件级的开路与短路问题。

3)除测试功能外,边界扫描还支持器件自定义指令集。新增的通用厂商特定指令(如配置和验证指令)进一步提升了边界扫描测试的实用性和普及度。

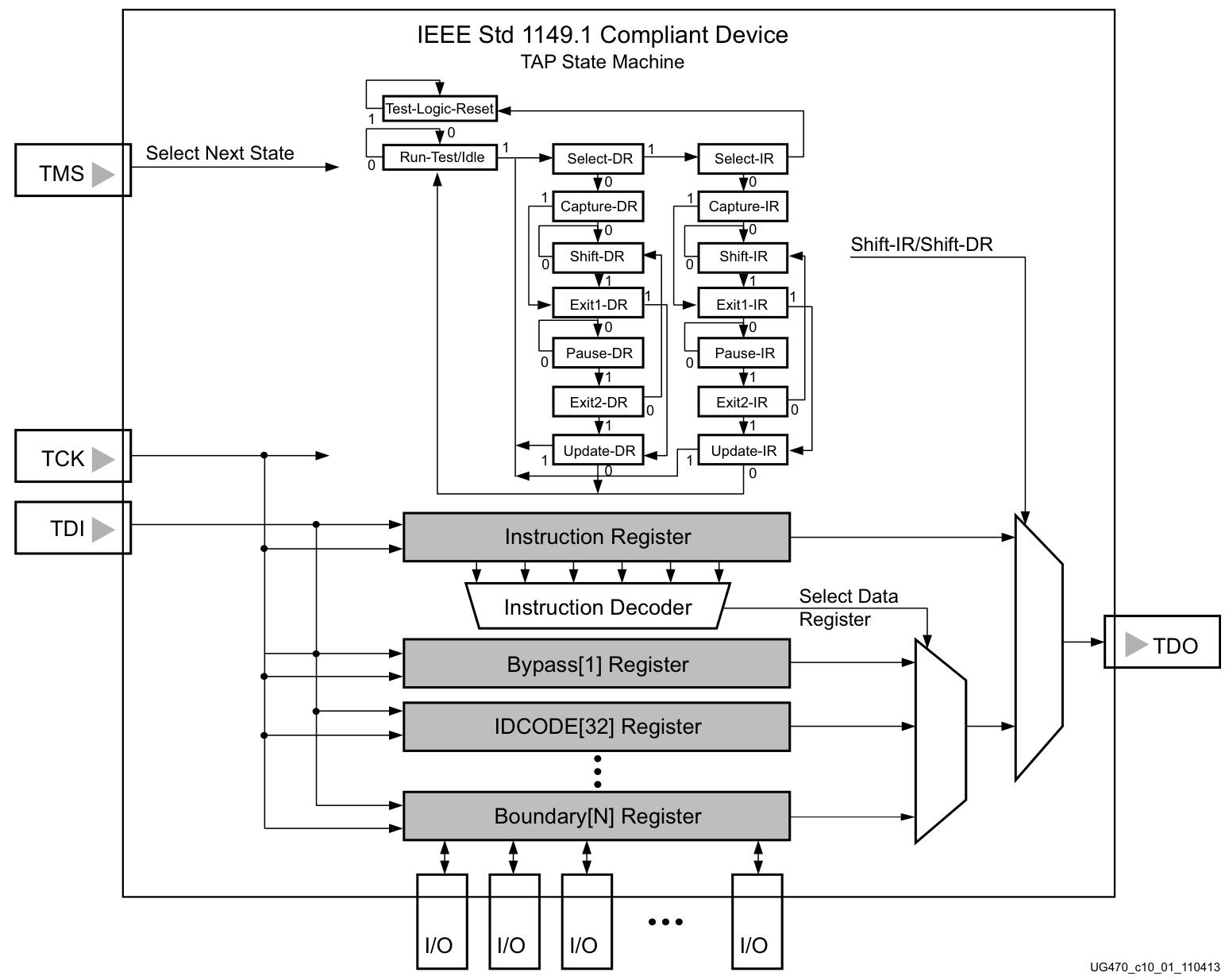

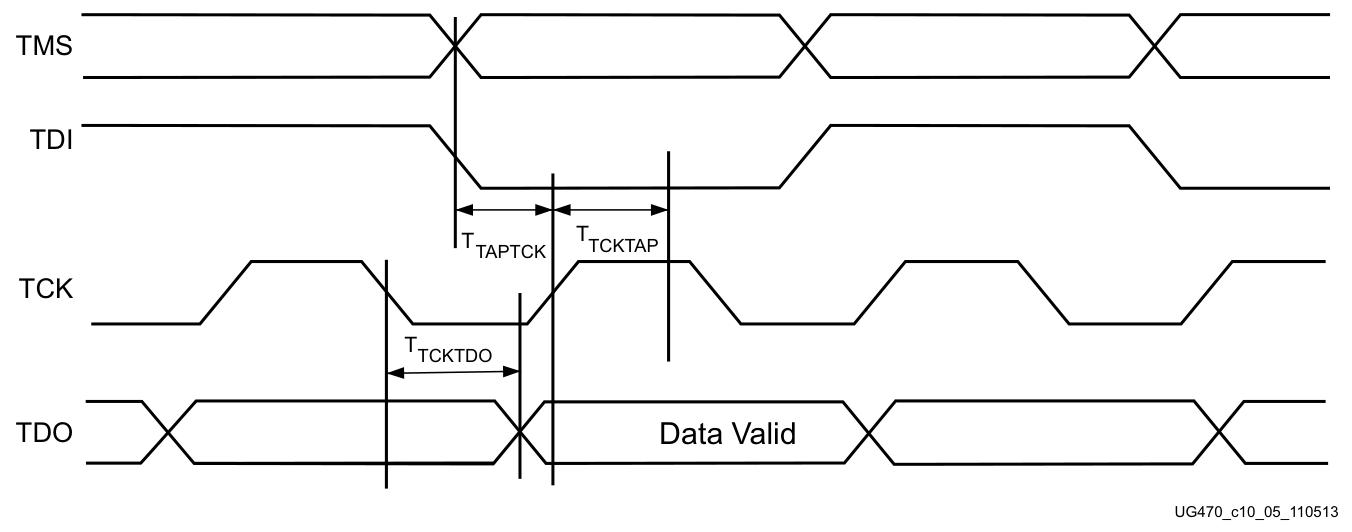

b)TAP控制器与架构

1)FPGA的测试访问端口TAP包含4个标准强制专用引脚。

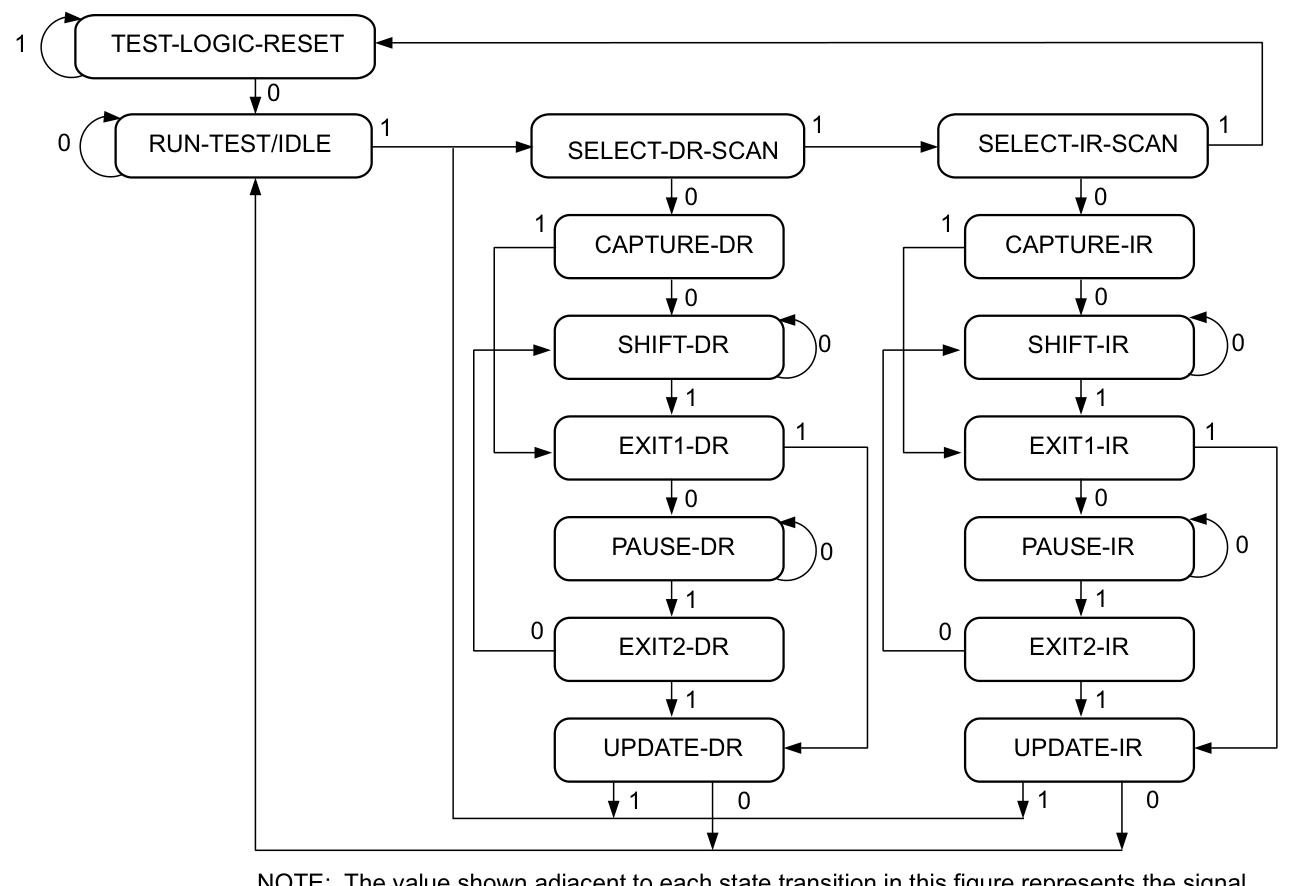

2)

①该架构描绘了一个16状态的有限状态机,4个TAP引脚(TCK、TMS、TDI、TDO)控制数据如何移入各类寄存器。TCK上升沿时TMS引脚的状态,决定了状态转移的顺序。整个状态机包含两条核心流程:一条用于将数据移入数据寄存器,另一条用于将指令移入指令寄存器。

②状态间的转移仅在TCK上升沿发生,每个状态均有唯一名称。图中两个垂直列(各含7个状态)分别对应指令路径和数据路径:数据寄存器仅在名称以DR结尾的状态下工作,指令寄存器仅在名称以IR结尾的状态下工作,两条路径的状态除操作对象不同外,其余功能完全相同。

③各状态的具体操作如下:

Test-Logic-Reset(测试逻辑复位状态):此状态下所有测试逻辑被禁用,器件恢复正常工作模式。TAP控制器状态机设计为:无论初始状态如何,只要将TMS引脚置高并脉冲触发TCK五次,即可进入该状态。因此,测试复位TRST引脚为可选配置。

Run-Test-Idle(运行测试空闲状态):此状态下,仅当存在特定激活指令时(如自测试指令),器件内部测试逻辑才会工作;否则测试逻辑保持空闲。

Select-DR-Scan(数据寄存器扫描选择状态):控制状态机进入数据路径或跳转至Select-IR-Scan状态。

Select-IR-Scan(指令寄存器扫描选择状态):控制状态机进入指令路径;若未触发路径选择,状态机可返回Test-Logic-Reset状态。

Capture-IR(指令捕获状态):TCK上升沿时,指令寄存器中的移位寄存器组会并行加载一组固定值模式,其中最后两位有效位必须为 01。

Shift-IR(指令移位状态):指令寄存器被接入TDI与TDO之间,捕获的固定值模式在每个TCK上升沿移位输出;同时,TDI引脚上的指令数据被串行移入指令寄存器。

Exit1-IR(指令移位退出1状态):控制状态机进入Pause-IR状态(暂停移位)或Update-IR状态(更新指令)。

Pause-IR(指令移位暂停状态):可暂时停止指令寄存器的移位操作。

Exit2-DR(数据移位退出2状态):控制状态机进入Shift-DR状态(继续数据移位)或Update-DR状态(更新数据)。

Update-IR(指令更新状态):TCK下降沿时,指令寄存器中的指令被锁存至指令寄存器的锁存组,该指令自此成为当前生效指令。

Capture-DR(数据捕获状态):TCK上升沿时,当前指令选中的数据寄存器会并行加载目标数据(如边界扫描寄存器采样I/O引脚信号、IDCODE寄存器加载器件标识)。

Shift-DR、Exit1-DR、Pause-DR、Exit2-DR、Update-DR(数据路径相关状态):功能与指令路径的Shift-IR、Exit1-IR、Pause-IR、Exit2-IR、Update-IR状态一致,仅操作对象为数据寄存器。

3)7系列器件支持IEEE Std 1149.1标准规定的强制指令,同时兼容多项AMD厂商特定指令,包括:

①标准指令:EXTEST(边界扫描测试)、SAMPLE/PRELOAD(采样 / 预加载)、BYPASS(旁路)、IDCODE(读取器件标识)、USERCODE(读取用户自定义代码)。

②厂商特定指令:JSTART(启动配置序列)、JSHUTDOWN(启动关断序列)、HIGHZ_IO(仅禁用用户I/O引脚,区别于标准HIGHZ指令)。

③扩展功能:支持用户自定义内部寄存器(USER1~USER4),以及器件的JTAG配置与读回;不支持INTEST指令。

4)FPGA的边界扫描操作与配置模式选择相互独立,且边界扫描模式优先级高于其他配置模式。因此,使用边界扫描寄存器的指令(SAMPLE/PRELOAD、EXTEST)不得在配置过程中执行。器件未配置前,除用户自定义指令外,其余所有指令均可用;配置完成后,所有指令均支持。

5)需注意:7系列器件的TAP控制器不会被PROGRAM_B引脚复位,仅能通过将状态机切换至Test-Logic-Reset状态实现复位(具体操作:将TMS置高并脉冲触发TCK五次,确保状态机进入TLR);TAP控制器在上电时会自动复位。

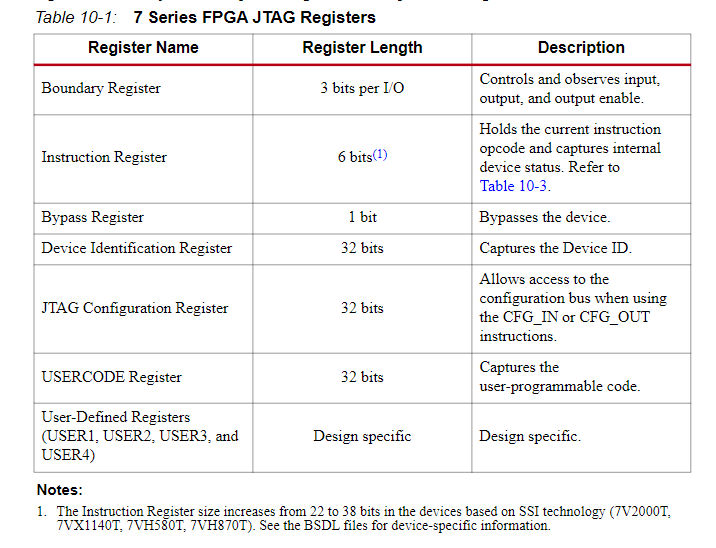

c)边界扫描架构

1)7系列器件的寄存器包含IEEE Std 1149.1标准要求的所有寄存器,此外还集成了用于简化测试与验证的可选寄存器。

①标准必备寄存器:边界扫描寄存器、指令寄存器、旁路寄存器、器件标识寄存器;

②配置专用寄存器:JTAG配置寄存器、用户代码寄存器;

③用户自定义寄存器:USER1~USER4。

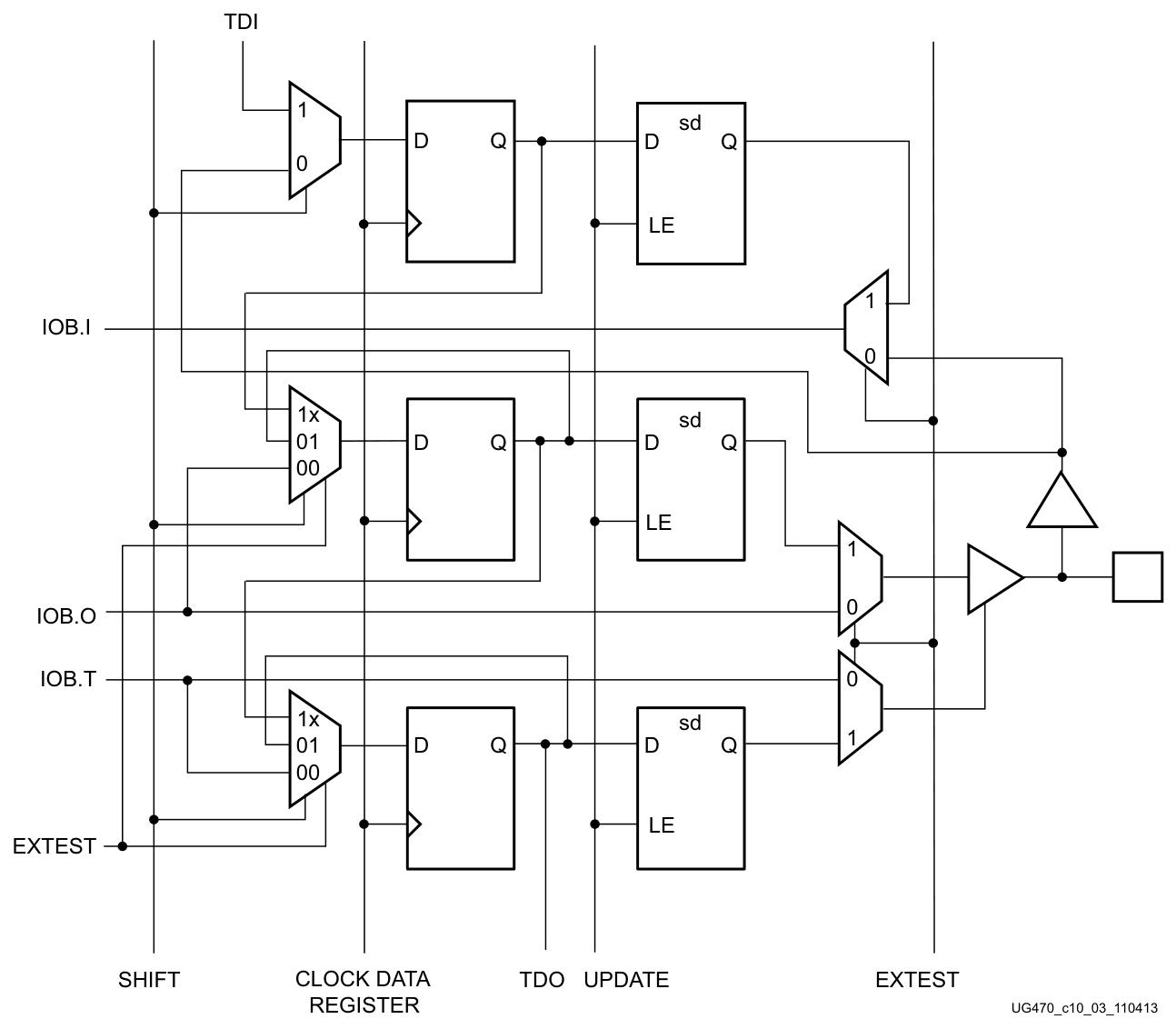

2)边界扫描寄存器(Boundary Register)

①边界扫描寄存器是核心数据寄存器,边界扫描操作与单个IOB(I/O缓冲器)的配置相互独立。每个IOB(无论引脚是否已绑定)初始状态为带三态控制的双向模式,后续可配置为输入、输出、仅三态模式。因此,每个IOB对应3位数据寄存器。

①TDI串行输入→3位寄存器并行控制IOB→TDO串行输出

3)执行数据寄存器DR操作时,流程如下:捕获阶段(CAPTURE-DR状态)数据以并行方式被捕获到数据寄存器中;移位阶段(SHIFT-DR 状态)已捕获的数据被串行移位输出,同时新数据被移入寄存器;更新阶段每个数据寄存器位都配有更新锁存器,用于在下次SHIFT-DR状态期间保持输入数据稳定,最终在UPDATE-DR状态的TCK低电平时完成数据锁存。

d)边界扫描寄存器的位序

1)本节说明每个非TAP引脚IOB(I/O缓冲器)在边界扫描寄存器中的位序规则:依次为输入位、输出位,最后是IOB三态控制位,其中三态控制位紧邻TDO(测试数据输出)端。仅输入引脚仅在边界扫描I/O数据寄存器中占用输入位,无输出位和三态控制位。器件的边界扫描位序可从7系列家族的BSDL(边界扫描描述语言)文件中获取(该文件可从AMD下载区获取,描述的是未配置状态下的FPGA)。需注意:边界扫描位序具有固定的顺序和位数,与具体设计方案无关。若需对已配置的FPGA执行边界扫描测试,AMD提供ISE BSDLAnno工具,可自动修改BSDL文件,以适配配置后的互连测试。该工具从已实现的设计中提取必要的FPGA设计信息,生成能反映器件配置后边界扫描架构的BSDL文件。Vivado也提供类似功能。

e)指令寄存器

1)在指令扫描序列期间,7系列器件的指令寄存器会接入TDI(测试数据输入)与TDO之间。序列启动前,指令寄存器会并行加载一组固定的指令捕获模式,该模式以最低位LSB优先的方式从TDO移位输出,同时新的指令从TDI移位移入指令寄存器。

2)旁路寄存器(Bypass Register):另一款标准数据寄存器是单触发器结构的旁路寄存器。执行BYPASS指令时,它会将数据从TDI(测试数据输入)引脚串行传递至TDO(测试数据输出)引脚。当TAP控制器处于CAPTURE-DR状态时,该寄存器会初始化为0。

3)器件标识寄存器(IDCODE Register):7系列器件配备32位的器件标识寄存器(IDCODE寄存器),其设计遵循IEEE Std 1149.1标准,是厂商分配的固定值,用于电气层面识别目标器件的厂商信息与器件类型。通过边界扫描进行测试或编程时,可借助该寄存器快速识别器件;执行IDCODE指令即可将寄存器内的数据移位输出,供外部设备读取校验。需注意:IDCODE 寄存器的最低位LSB始终为1(符合JTAG IEEE 1149.1标准),且寄存器值的最后三位十六进制数固定为0x093。

4)JTAG配置寄存器(JTAG Configuration Register):JTAG配置寄存器为32位宽,其核心功能是提供配置总线的访问通道,支持JTAG相关的配置写入与读回操作。

5)用户代码寄存器(USERCODE Register):7系列家族支持USERCODE指令,该寄存器允许用户指定设计专属的识别码(如版本号、项目标识等)。USERCODE可被编程到器件中,后续可通过JTAG读回校验。比特流生成时(通过UserID选项),USERCODE会被嵌入比特流,且仅在器件配置完成后生效。若器件为空白(未配置)或未编程USERCODE,该寄存器的默认值为0xFFFFFFFF。

6)USER1~USER4寄存器(USER1, USER2, USER3, USER4 Registers):USER1-USER4 、寄存器仅在器件配置完成后可用,这四个寄存器的功能需用户在设计中自行定义。定义完成后,可通过TAP引脚访问这些寄存器;创建此类用户自定义寄存器时,必须使用BSCANE2库原语(BSCANE2 library primitive)。

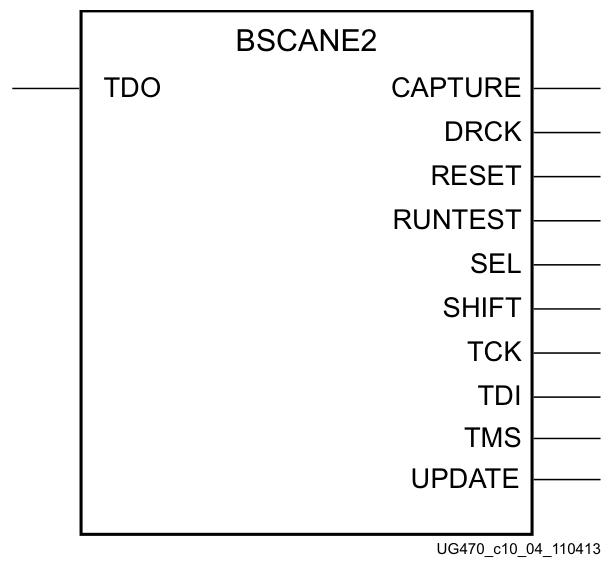

f)BSCANE2原语(BSCANE2 Primitive)

1)BSCANE2原语用于实现FPGA内部逻辑与JTAG边界扫描逻辑控制器之间的通信,搭建起FPGA内部运行的设计与专用JTAG引脚(测试访问端口TAP)之间的交互通道。若需从FPGA内部访问JTAG引脚,必须例化该原语;而通过JTAG引脚直接访问TAP控制器的常规JTAG操作(如标准边界扫描测试),则无需使用BSCANE2原语。使用Vivado逻辑分析仪时,工具会自动在设计中添加BSCANE2原语。

2)BSCANE2原语的典型应用场景是在FPGA逻辑中创建内部专用扫描寄存器。这类扫描寄存器的数据传输仅在FPGA内部逻辑中进行,区别于标准JTAG边界扫描(数据通过边界I/O传输)。每个BSCANE2原语实例仅支持一条JTAG USER指令,多实例通过JTAG_CHAIN属性区分;若需支持全部四条USER指令(USER1~USER4),需例化四个BSCANE2原语,并为每个实例设置唯一的JTAG_CHAIN属性。

3)

TDI:接收JTAG TAP端口的外部TDI信号,用于将数据移入内部扫描链。

TDO:向JTAG TAP端口的外部TDO引脚输出数据,用于将内部扫描链的数据移出。

TCK:接收JTAG TAP端口的外部TCK时钟信号,为原语所有操作提供同步基准。

TMS: 接收JTAG TAP端口的外部TMS信号,用于监控TAP控制器的模式选择状态。

CAPTURE:边界扫描内部状态机CAPTURE-DR状态的解码信号(高电平有效)。

SHIFT:边界扫描内部状态机SHIFT-DR状态的解码信号(高电平有效)。

UPDATE:边界扫描内部状态机UPDATE-DR状态的解码信号(高电平有效)。

DRCK:输出TAP控制器生成的数据寄存器时钟,供内部扫描链执行移位与捕获操作。

RESET:边界扫描逻辑的复位信号(高电平有效),由TAP控制器状态机解码生成。

RUNTEST:边界扫描内部状态机RUN-TEST/Idle状态的解码信号(高电平有效)。

SEL:指示当前激活的USER指令(USER1~USER4),高电平有效。

4)

(持续补充)

(持续补充)