题目考查的是向量处理器(Vector Processing)架构设计的核心知识点,包括向量流水线延迟、链式操作(Chaining)、存储器分体交叉存取(Memory Bank Interleaving)以及多核共享存储冲突。

以下是详细的知识点解析和作答:

一、 相关知识点

- 向量指令流水线(Vector Pipeline) :向量指令对一组元素执行相同操作。总执行时间通常为: T = Start-up Latency + ( L − 1 ) T = \text{Start-up Latency} + (L - 1) T=Start-up Latency+(L−1),其中 L L L 是向量长度。

- 分体交叉存储(Memory Banking) :为了隐藏内存访问延迟,将内存分为多个 Bank。若 Bank 数量 B ≥ 延迟 N B \ge \text{延迟 } N B≥延迟 N,则可以实现每个时钟周期处理一个元素。若 B < N B < N B<N,则会产生 Bank Conflict(存储体冲突),导致流水线阻塞。

- 链式操作(Chaining):允许一条向量指令在产生第一个元素结果时,立即将其送入下一条指令的流水线,而不必等待整个向量计算完毕。这类似于标量处理中的数据转发(Forwarding)。

- 存储体冲突阻塞计算 :当产生冲突时,后续访问必须等待 Bank 恢复。增加的停顿周期通常为 ( N − B ) (N - B) (N−B),每经过一轮 Bank 循环都会产生一次停顿。

- Row Buffer(行缓冲区)冲突:在多核共享内存中,不同核心访问同一 Bank 的不同行会导致行缓冲区频繁置换(Precharge/Activate),显著增加延迟。

二、 详细作答内容

这是一道非常经典的关于 向量处理器(Vector Processing) 、内存交叉存取(Memory Interleaving) 、链式操作(Chaining) 以及 流水线(Pipeline) 性能分析的题目。

以下是针对每个小题的详细考点解析和解题过程。

题目背景梳理

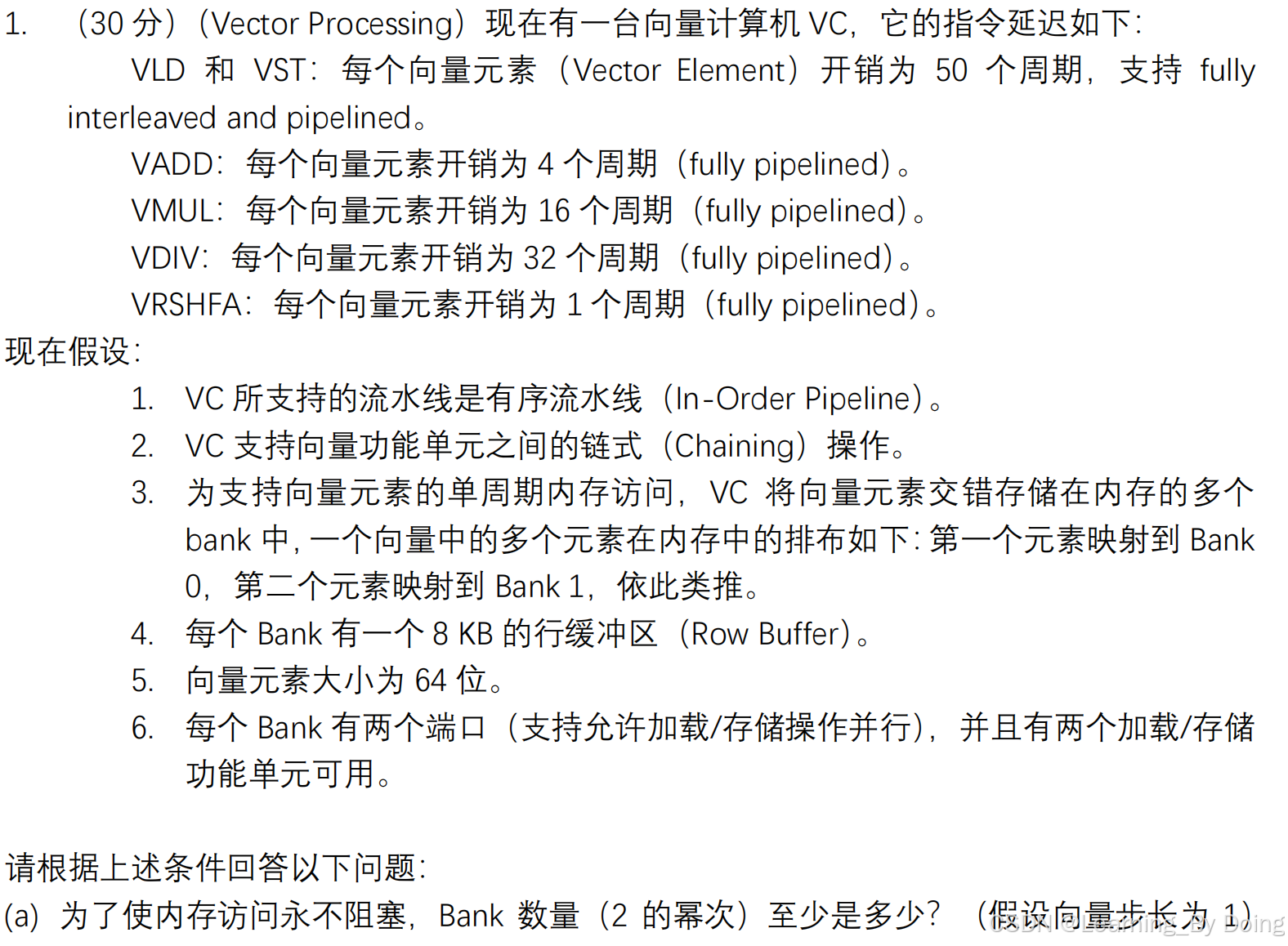

- 指令延迟(Latency):

- Load/Store (VLD/VST): 50 cycles

- Add (VADD): 4 cycles

- Mul (VMUL): 16 cycles

- Div (VDIV): 32 cycles

- Shift (VRSHFA): 1 cycle

- 架构特性:

- 支持链式操作(Chaining):后一条指令可以在前一条指令产生第一个结果后立即开始,不需要等待整个向量完成。

- 支持并行 Load/Store:有2个 Load/Store 单元,每个 Bank 有2个端口。

- 内存:多 Bank 交叉存储(Interleaved),Bank 繁忙时间等于延迟(50 cycles)。

- 向量长度:L。

- 数据分布:Element i i i 映射到 Bank i ( m o d N ) i \pmod N i(modN)。

(a) 内存 Bank 数量计算

考查知识点: 内存交叉存取带宽,Bank 冲突。

问题: 为了使内存访问永不阻塞(即每个周期都能提供一个数据),Bank 数量(2的幂次)至少是多少?

解析:

要实现流水线式的"每个时钟周期取一个数"(吞吐量为 1 element/cycle),内存系统必须能够连续处理请求。

如果一个 Bank 处理一次请求需要 T l a t e n c y = 50 T_{latency} = 50 Tlatency=50 个周期,那么在同一个 Bank 准备好接受下一次请求之前,处理器可以向其他 Bank 发送请求。

为了让第 0 号 Bank 在再次被访问时已经空闲,我们必须至少经过 50 个周期。

因为是交叉存储(Stride=1),我们会依次访问 Bank 0, 1, 2...

所需的最小 Bank 数量 N N N 满足:

N ≥ Memory Latency × Desired Throughput N \ge \text{Memory Latency} \times \text{Desired Throughput} N≥Memory Latency×Desired Throughput

N ≥ 50 × 1 = 50 N \ge 50 \times 1 = 50 N≥50×1=50

题目要求 Bank 数量必须是 2 的幂次。

大于等于 50 的最小 2 的幂次是 64。

答案: 64 banks

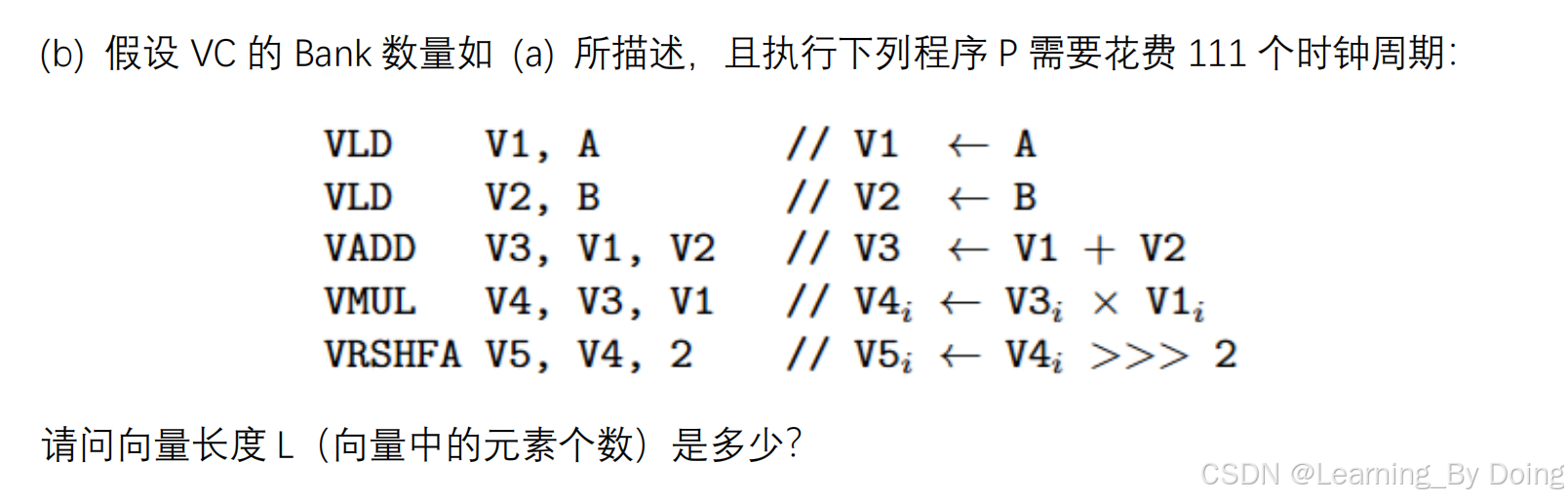

(b) 链式操作下的向量长度计算

考查知识点: 向量链式操作(Chaining)的时序分析。

问题: 执行程序 P 花费 111 个周期,求向量长度 L L L。

解析:

程序 P 的指令依赖关系如下:

VLD V1, AVLD V2, B(与 V1 并行,延迟 1 周期发射)VADD V3, V1, V2(依赖 V1, V2)VMUL V4, V3, V1(依赖 V3, V1)VRSHFA V5, V4, 2(依赖 V4)

计算关键路径(Critical Path):

在链式操作中,总执行时间 = 首元素产生时间(Start-up Latency) + (向量长度 L - 1)。

我们需要计算最后一个结果 V5[0] 产生的时间(Start-up):

- VLD V2: 第 2 条 Load 指令比第 1 条晚 1 个周期发射。V2[0] 就绪时间 = 1 + 50 = 51 1 + 50 = 51 1+50=51。

- 注:虽然 VLD V1 在 50 就绪,但 VADD 需要两个操作数,取决于较慢的那个(V2)。

- VADD: 拿到 V1[0] 和 V2[0] 后开始。耗时 4。V3[0] 就绪时间 = 51 + 4 = 55 51 + 4 = 55 51+4=55。

- VMUL: 拿到 V3[0] 和 V1[0](早已就绪)后开始。耗时 16。V4[0] 就绪时间 = 55 + 16 = 71 55 + 16 = 71 55+16=71。

- VRSHFA: 拿到 V4[0] 后开始。耗时 1。V5[0] 就绪时间 = 71 + 1 = 72 71 + 1 = 72 71+1=72。

总时间公式:

T t o t a l = T f i r s t _ e l e m e n t _ r e a d y + ( L − 1 ) T_{total} = T_{first\_element\_ready} + (L - 1) Ttotal=Tfirst_element_ready+(L−1)

111 = 72 + ( L − 1 ) 111 = 72 + (L - 1) 111=72+(L−1)

111 = 71 + L 111 = 71 + L 111=71+L

L = 40 L = 40 L=40

答案: L = 40

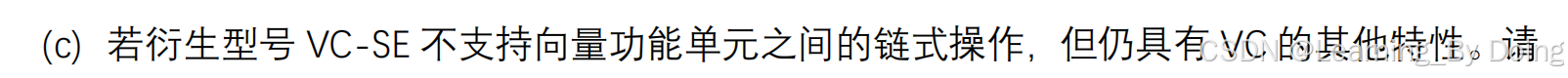

© 无链式操作(No Chaining)的执行时间

考查知识点: 无链式机制下的向量执行时序。

问题: 衍生型号 VC-SE 不支持链式操作,求执行时间。

解析:

不支持链式操作意味着:一条向量指令必须完全执行完毕(所有 L 个元素都写回),下一条依赖它的指令才能开始。

向量长度 L = 40 L=40 L=40。

每条指令的执行时间 = S t a r t _ u p + ( L − 1 ) Start\_up + (L-1) Start_up+(L−1)。但是,由于没有链式,依赖指令的启动时间必须叠加前一条指令的全部执行时间。

执行流程分析:

-

VLD V1 & VLD V2: 并行执行(有2个 Load 单元)。

VLD V2较晚结束,决定了后续VADD的开始时间。VLD V2开始于 T=1。VLD V2结束时间 = 1 ( offset ) + 50 ( latency ) + ( 40 − 1 ) = 90 1 (\text{offset}) + 50 (\text{latency}) + (40-1) = 90 1(offset)+50(latency)+(40−1)=90。- 此刻 V1 和 V2 都准备好了。

-

VADD: 在 T=90 开始。

- 持续时间 = 4 ( latency ) + ( 40 − 1 ) = 43 4 (\text{latency}) + (40-1) = 43 4(latency)+(40−1)=43。

- 结束时间 = 90 + 43 = 133 90 + 43 = 133 90+43=133。

-

VMUL: 在 T=133 开始。

- 持续时间 = 16 ( latency ) + ( 40 − 1 ) = 55 16 (\text{latency}) + (40-1) = 55 16(latency)+(40−1)=55。

- 结束时间 = 133 + 55 = 188 133 + 55 = 188 133+55=188。

-

VRSHFA: 在 T=188 开始。

- 持续时间 = 1 ( latency ) + ( 40 − 1 ) = 40 1 (\text{latency}) + (40-1) = 40 1(latency)+(40−1)=40。

- 结束时间 = 188 + 40 = 228 188 + 40 = 228 188+40=228。

或者使用红字中的累加公式理解:

总时间 = (VLD2 启动开销) + (VADD 启动开销) + (VMUL 启动开销) + (SHIFT 启动开销) + 4 × ( L − 1 ) 4 \times (L-1) 4×(L−1)

T = ( 1 + 50 ) + 4 + 16 + 1 + 4 × 39 T = (1 + 50) + 4 + 16 + 1 + 4 \times 39 T=(1+50)+4+16+1+4×39

T = 72 + 156 = 228 T = 72 + 156 = 228 T=72+156=228

答案: 228 cycles

(d) VC-Mini (Bank 减半) 的执行时间

考查知识点: Bank 冲突(Bank Conflict)与仲裁带来的延迟。

问题: Bank 数量减半为 32 个( 64 / 2 64/2 64/2),向量长度 L = 40 L=40 L=40,Bank 增加仲裁器。求执行时间。

解析:

Bank 数量 B = 32 B=32 B=32,向量长度 L = 40 L=40 L=40。

这意味着向量无法一次性无冲突地访问内存。

- Element 0 到 31 映射到 Bank 0 到 31(无冲突)。

- Element 32 再次映射到 Bank 0。

冲突分析:

- Bank 的繁忙时间(Busy time)= 50 cycles。

- 访问 Bank 0 的时刻:

- Element 0 在 T = 0 T=0 T=0 发起访问。Bank 0 在 T = 0 ∼ 50 T=0 \sim 50 T=0∼50 处于忙碌状态。

- Element 32 想要在 T = 32 T=32 T=32 发起访问。但 Bank 0 此时忙碌。

- 仲裁器会让 Element 32 等待,直到 T = 50 T=50 T=50 Bank 0 变为空闲。

- 这导致了流水线的停顿(Stall)。

VLD 过程计算(以 VLD V2 为关键路径,因为它晚 1 周期):

- 第一批 (Elements 0-31): 正常流水。耗时 = Latency = 50。

- Bank 0 阻塞: Element 32 必须等到 T = 50 T=50 T=50 才能发射(相对于该指令的起始时间)。

- 第二批 (Elements 32-39):

- Element 32 在 T = 50 T=50 T=50 发射。

- 最后一个 Element 39 在 T = 50 + ( 39 − 32 ) = 57 T = 50 + (39-32) = 57 T=50+(39−32)=57 发射。

- Element 39 完成读取的时间 = 57 ( Issue Time ) + 50 ( Latency ) = 107 57 (\text{Issue Time}) + 50 (\text{Latency}) = 107 57(Issue Time)+50(Latency)=107。

考虑 VLD V2 的 1 周期 Offset:

VLD V2 的 Element 39 完成时间 = 107 + 1 = 108 107 + 1 = 108 107+1=108。

加上 ALU 链式延迟:

一旦最后一个数据进入 ALU 流水线,后续结果顺次产生。

总时间 = VLD_Last_Element_Done + VADD_Lat + VMUL_Lat + SHIFT_Lat

T = 108 + 4 + 16 + 1 = 129 T = 108 + 4 + 16 + 1 = 129 T=108+4+16+1=129

对应红字公式解析:

1 (Offset) + 50 (Latency 1st pass) + 50 (Stall for Bank 0) + 7 (Remaining elements 32-39) + 4+16+1 (ALU)

= 129 = 129 =129 cycles.

(注:这里假设每个Bank有2个端口,所以VLD1和VLD2在Element 0处不冲突,冲突仅来自于Element 32重用Bank 0)

答案: 129 cycles

(e) VC-Tiny (Bank 极少) 的 Bank 数量推断

考查知识点: 根据执行时间反推 Bank 架构参数。

问题: 执行时间为 279 周期,求 Bank 数量(2的幂次)。

解析:

已知公式结构:

T t o t a l = T L o a d _ L a s t _ E l e m e n t + ALU_Latencies T_{total} = T_{Load\_Last\_Element} + \text{ALU\Latencies} Ttotal=TLoad_Last_Element+ALU_Latencies

279 = T L o a d _ L a s t + ( 4 + 16 + 1 ) 279 = T{Load\Last} + (4 + 16 + 1) 279=TLoad_Last+(4+16+1)

T L o a d _ L a s t = 258 T{Load\_Last} = 258 TLoad_Last=258

对于 VLD V2(关键路径,有 +1 偏移):

T L o a d _ L a s t _ V 1 = 257 T_{Load\_Last\_V1} = 257 TLoad_Last_V1=257

最后一个元素是 Index 39。

假设 Bank 数量为 B B B。

Element 39 会在 Bank 39 ( m o d B ) 39 \pmod B 39(modB)。

它需要等待前面的冲突解决。

每一轮冲突(Wrap-around)需要等待 50 个周期(Bank Busy Time)。

Element i i i 的发射时间 ≈ ⌊ i B ⌋ × 50 + ( i ( m o d B ) ) \approx \lfloor \frac{i}{B} \rfloor \times 50 + (i \pmod B) ≈⌊Bi⌋×50+(i(modB))。

对于 i = 39 i=39 i=39:

Issue Time ≈ Rounds × 50 + Remainder \text{Issue Time} \approx \text{Rounds} \times 50 + \text{Remainder} Issue Time≈Rounds×50+Remainder

Finish Time = Issue Time + 50 \text{Finish Time} = \text{Issue Time} + 50 Finish Time=Issue Time+50

257 = Issue Time + 50 ⇒ Issue Time = 207 257 = \text{Issue Time} + 50 \Rightarrow \text{Issue Time} = 207 257=Issue Time+50⇒Issue Time=207

我们看 ⌊ 39 B ⌋ × 50 \lfloor \frac{39}{B} \rfloor \times 50 ⌊B39⌋×50 大约等于 200。

这意味着 ⌊ 39 B ⌋ = 4 \lfloor \frac{39}{B} \rfloor = 4 ⌊B39⌋=4。

即 4 × B ≤ 39 < 5 × B 4 \times B \le 39 < 5 \times B 4×B≤39<5×B。

B B B 必须是 2 的幂次。

若 B = 8 B=8 B=8: 39 / 8 = 4 39 / 8 = 4 39/8=4 余 7 7 7。

Issue Time = 4 × 50 + 7 = 207 4 \times 50 + 7 = 207 4×50+7=207。

Finish Time = 207 + 50 = 257 207 + 50 = 257 207+50=257。

符合!

验证:

若 Bank = 8。

- 0-7: T=0 issue.

- 8-15: T=50 issue.

- 16-23: T=100 issue.

- 24-31: T=150 issue.

- 32-39: T=200 issue.

- Element 39 issue at 200 + 7 = 207 200 + 7 = 207 200+7=207.

- Load Done at 207 + 50 = 257 207 + 50 = 257 207+50=257.

- VLD2 Done at 258.

- Total = 258 + 21 = 279 258 + 21 = 279 258+21=279.

答案: 8 Banks

(f) 多核性能下降原因

考查知识点: 共享内存系统中的资源争用(Contention)。

问题: 4核共享内存,Bank 数量增加了4倍,但单核性能反而比以前只有 1/4 Bank 时还差。为什么?

解析:

尽管总 Bank 数量增加了,但如果所有核心都使用相同的步长(Stride=1)访问内存,并且内存映射方式是简单的交叉存储(Interleaved),那么:

Core 0 访问 Bank 0, 1, 2...

Core 1 访问 Bank 0, 1, 2...

Core 2 访问 Bank 0, 1, 2...

Core 3 访问 Bank 0, 1, 2...

所有核心会在同一时间争抢同一个 Bank(尤其是 Bank 0, 1...)。

这被称为 Row-buffer conflicts 或 Bank Conflicts 。

原本独占 1/4 Bank 时,核心之间没有干扰。现在虽然 Bank 多了,但如果大家都在"排队"访问同一个 Bank,等待时间会大大增加。

答案: Row-buffer conflicts (all cores interleave their vectors across all banks). 所有的核都在尝试同时访问相同的 Bank 序列,导致严重的 Bank 冲突和阻塞。

(g) 缓解措施

考查知识点: 存储系统的优化策略。

问题: 仅改变共享内存架构,如何缓解 (f) 中的问题?

解析:

要解决冲突,必须让不同核心访问不同的 Bank,或者打乱访问模式。

- Memory Partitioning(内存分区): 将 Bank 分组,Core 0 专用 Group 0,Core 1 专用 Group 1。这样消除了核间干扰。

- Better Memory Mapping/Scheduling(更好的映射/调度): 使用基于异或(XOR)的哈希映射或置换映射,使得 Core A 的线性访问和 Core B 的线性访问映射到不同的物理 Bank 序列,减少碰撞概率。

答案: Partition the memory mappings, or using better memory scheduling. (对内存映射进行分区,或使用更好的内存调度策略)。