1. GPIO跟引脚有什么区别

引脚包含GPIO,引脚还包括电源引脚,BOOT引脚,复位引脚等

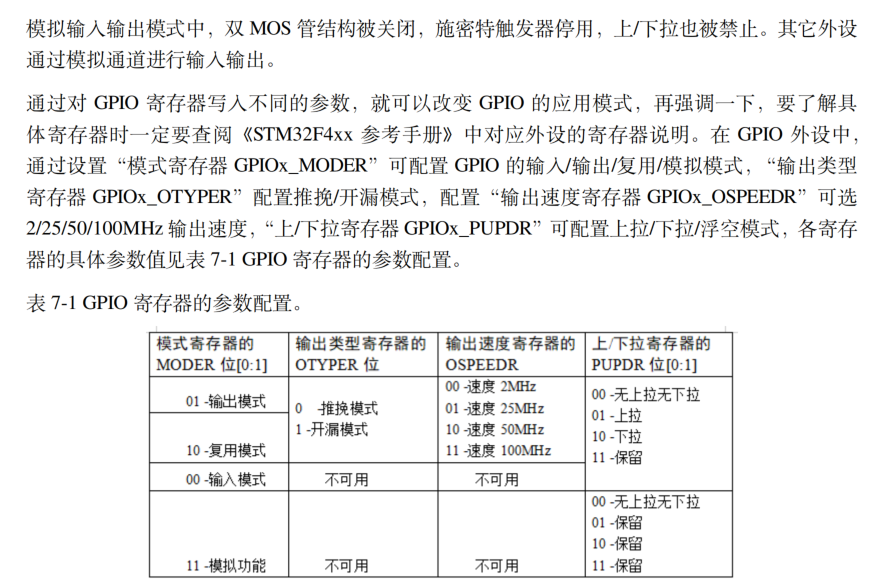

下图是STM32数据手册中的引脚分类

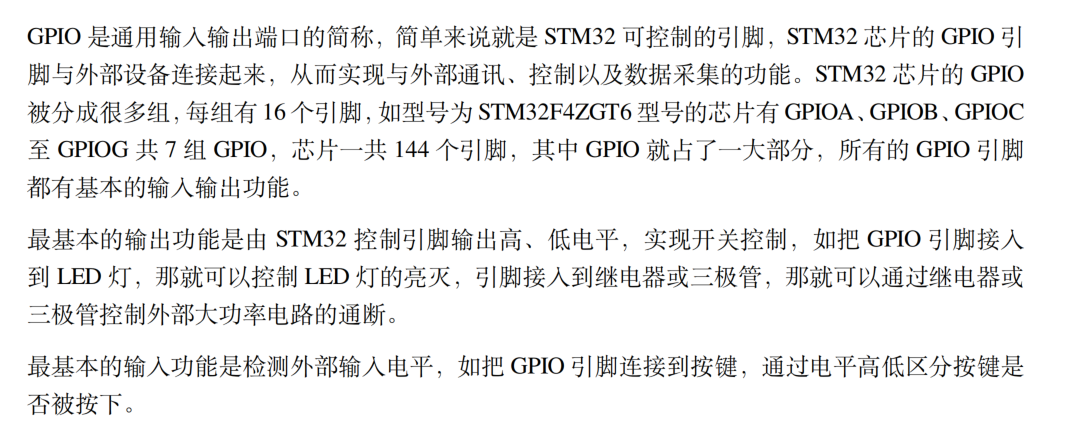

2. GPIO简介

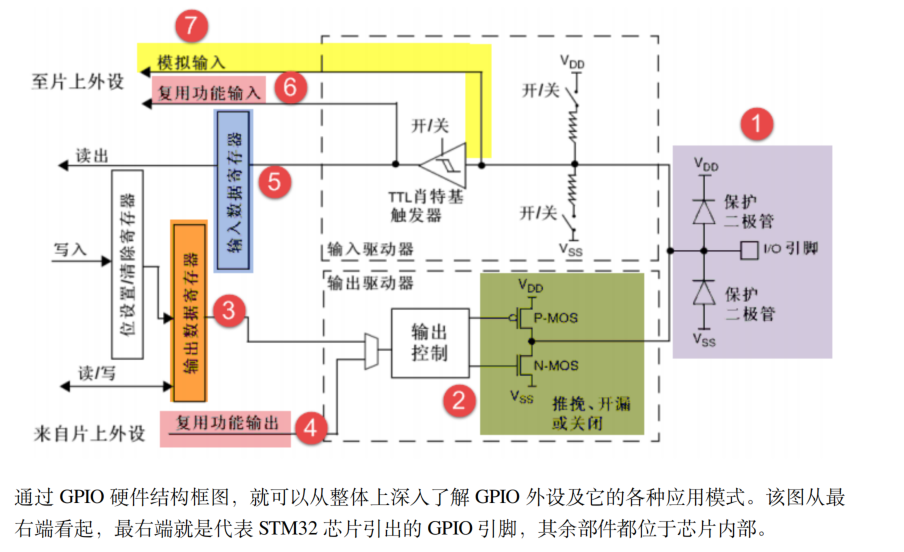

3. GPIO功能框图

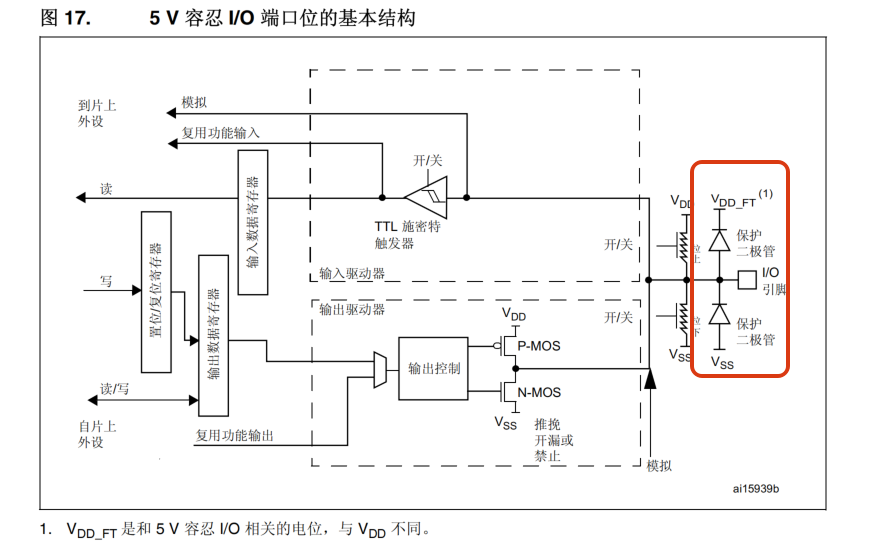

3.1 保护二极管、上下拉电阻

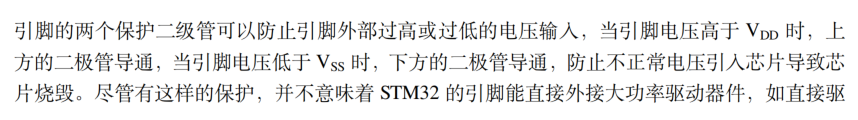

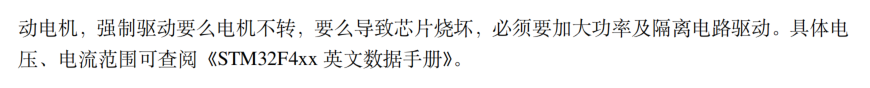

保护二极管

STM32的引脚出了ADC,都是可以容忍5V供电

如输入电压大于5V,则通过上面的保护二极管;如输入电压小于0V,如-1V,则由VSS经下面的二极管从I/O出去。

上下拉电阻

"弱上拉(weak pull-up)"可以把它理解成:STM32 在引脚内部偷偷帮你接了一根"很大电阻"的上拉到 VDD ,让引脚在没人驱动时不要飘(floating),但它拉不动大电流。

- 弱上拉到底"弱"在哪?

因为内部上拉并不是直接硬连到 VDD,而是类似这样:

VDD ──(几十 kΩ 的电阻)── GPIO 引脚

这个"电阻很大"(常见量级 30kΩ~50kΩ,不同芯片略有差异),所以电流很小:

假设 3.3V、40kΩ

电流约:3.3V / 40kΩ ≈ 0.082mA(82µA)

这点电流只能做一件事:给输入脚一个默认高电平

它不适合拿来供电、驱动 LED、拉动继电器之类的负载。

- 弱上拉的典型用途

✅ 给输入脚提供默认电平

比如按键一端接 GND,另一端接 GPIO,打开弱上拉后:

不按:GPIO 被弱上拉 → 读到 1

按下:GPIO 被按键直接拉到 GND → 读到 0

✅ 避免悬空导致乱跳

输入脚悬空时会因为噪声随机读 0/1,弱上拉/下拉就是为了稳定它。

- 为什么说"要大电流还得外部上拉"?

因为外部上拉可以用更小的电阻,比如 4.7kΩ / 10kΩ:

3.3V + 4.7kΩ

电流约:0.7mA(比内部弱上拉大很多)

上升沿更快、抗干扰更强、能拉住更"重"的外部电路输入

内部弱上拉:

电流小

抗干扰一般

对长线、强干扰环境可能不够稳

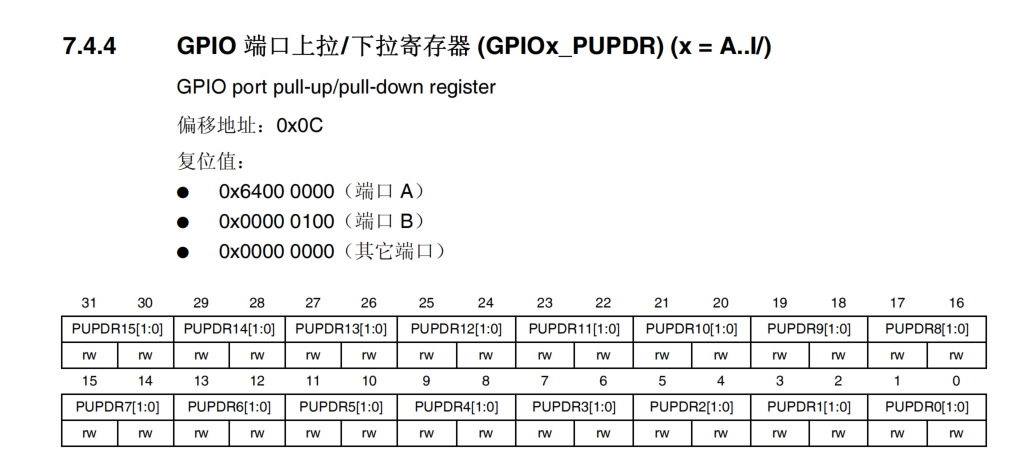

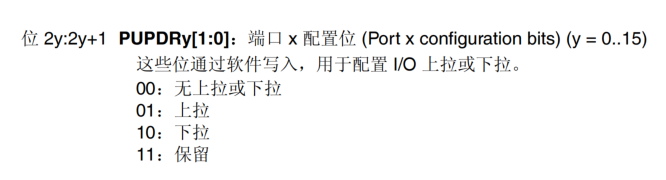

上下拉电阻的控制,通过上拉/下拉寄存器控制,如下所示

PUPDR0[1:0]里的[1:0]表示:这个字段(field)占用 2 个比特 ,从 bit1 到 bit0。

[高位:低位]是寄存器手册里描述"位范围"的常见写法所以

PUPDR0[1:0]= 两位二进制数(bit1、bit0 组成)这两位合起来编码含义(你截图里那张表):

00:无上拉/下拉

01:上拉

10:下拉

11:保留同理:

PUPDR3[1:0]不是寄存器的 bit1..0,而是"第3组字段也有两位",它在整个 32-bit 寄存器里的位置是 bit(23+1 : 23) = bit7:6。记住一句话:

[1:0]说的是字段宽度(2 bit),字段在寄存器里的实际位置要看它对应的 bit 范围(比如 7:6、25:24 等)。

中间那张"31...0 的大表":这是位段分布图GPIOx_PUPDR 这个寄存器是 32 位,每个引脚用 2 位控制(所以刚好 16 个引脚 ×2 = 32 位)。

表里你看到:

PUPDR15[1:0] 对应 bit31..30

PUPDR0[1:0] 对应 bit1..0

......

下面的

rw意思是 read/write(可读可写)。

3.2 输出模式

P-MOS 和 N-MOS 本质都是 MOSFET(场效应管),区别主要在沟道类型、需要的栅极驱动方向、导通特性,以及常见用法(高边/低边)。

1)最核心的区别

N-MOS(NMOS)

多数载流子:电子

栅极相对源极为正 才导通:

Vgs > Vth → 导通一般 导通电阻更小、同尺寸下电流能力更强、价格常更友好

P-MOS(PMOS)

多数载流子:空穴

栅极相对源极为负 才导通:

Vgs < −Vth → 导通(也可理解为"栅极比源极低"才开)一般 导通电阻更大(同工艺同尺寸下通常不如 NMOS)

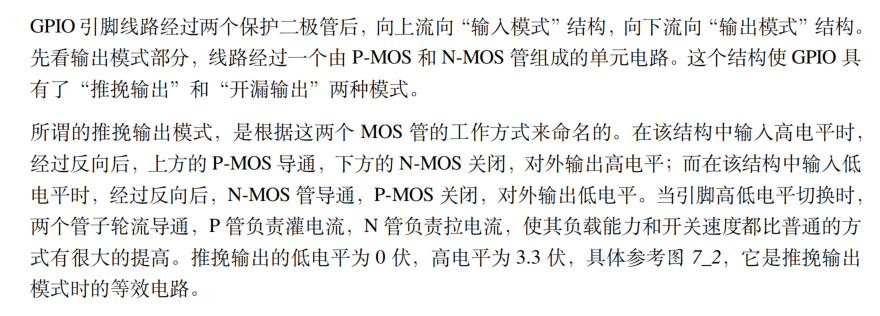

推挽输出

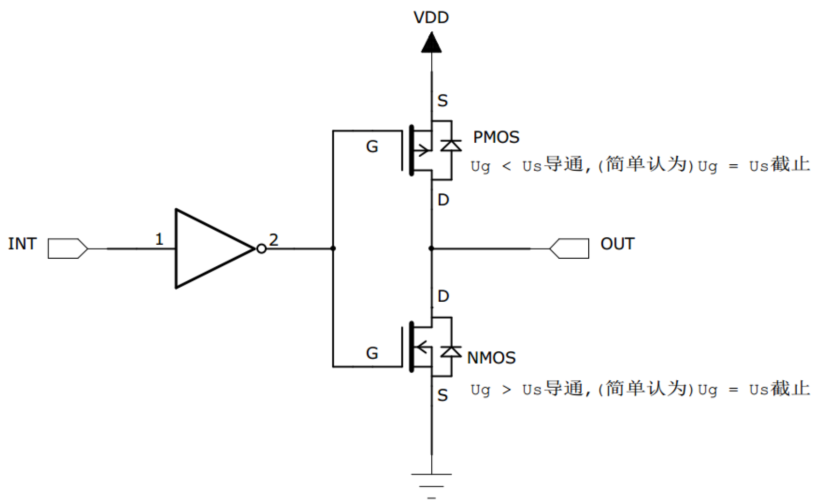

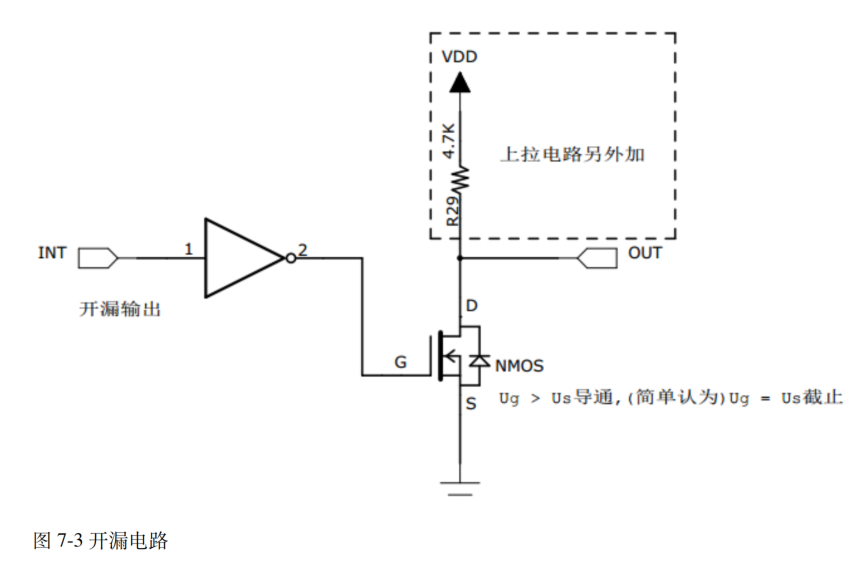

开漏输出

在 GPIO 里,"MOS 导通"≈"强上拉/强下拉"

**推挽输出(push-pull)**时:

上面的 P-MOS 导通 :输出被主动拉向 VDD → 可理解为强上拉

下面的 N-MOS 导通 :输出被主动拉向 GND/VSS → 可理解为强下拉

相比之下,弱上拉/弱下拉 是通过很大的电阻(几十 kΩ)拉,不是用 MOS 管"硬拉"。

但别把"强"理解成"无限强"

MOS 导通也不是理想短路,它有 Rds(on)(等效导通电阻),所以:

输出高电平并不一定等于 VDD(带大电流时会掉一点)

输出低电平也不一定等于 0V(带大电流时会抬一点)

STM32 每个 IO 口都有最大灌/拉电流限制(具体数值看 datasheet)

所以更准确的说法是:

MOS 导通 = 低阻驱动(strong drive),但受限于导通电阻和电流规格。

还有一种情况:开漏不是"强上拉"

**开漏输出(open-drain)**时:

只有 N-MOS那条"强下拉"

"上拉"要靠外部电阻 或内部弱上拉

→ 这时候就不是"强上拉"了

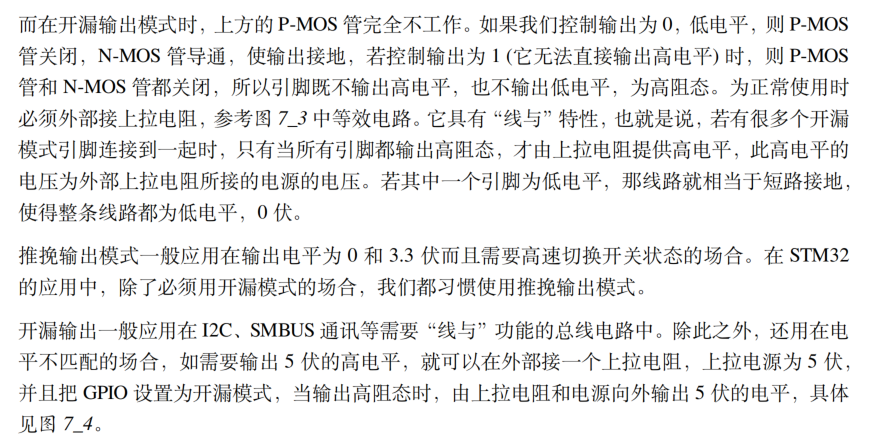

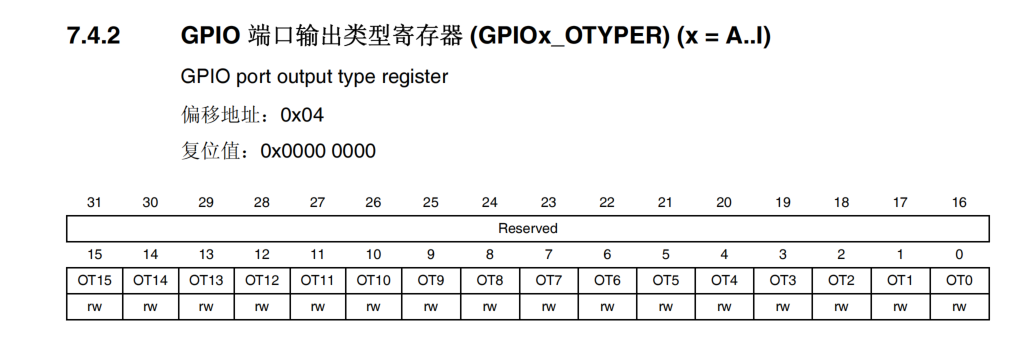

输出类型寄存器

两种输出模式通过输出类型寄存器控制

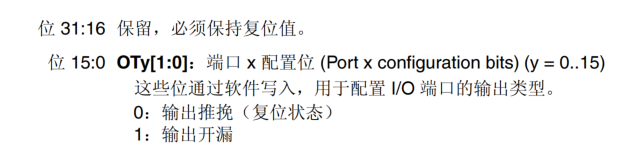

输出速度寄存器

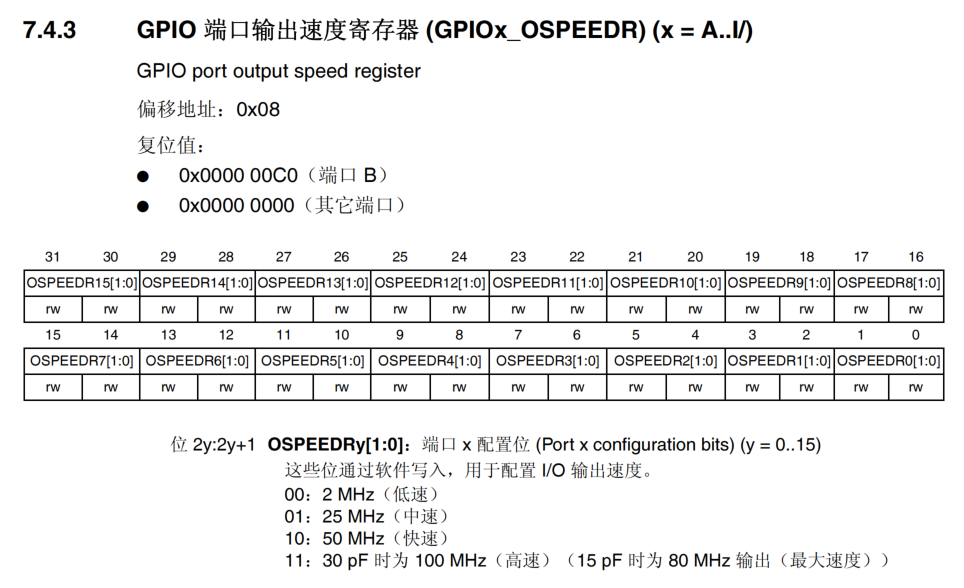

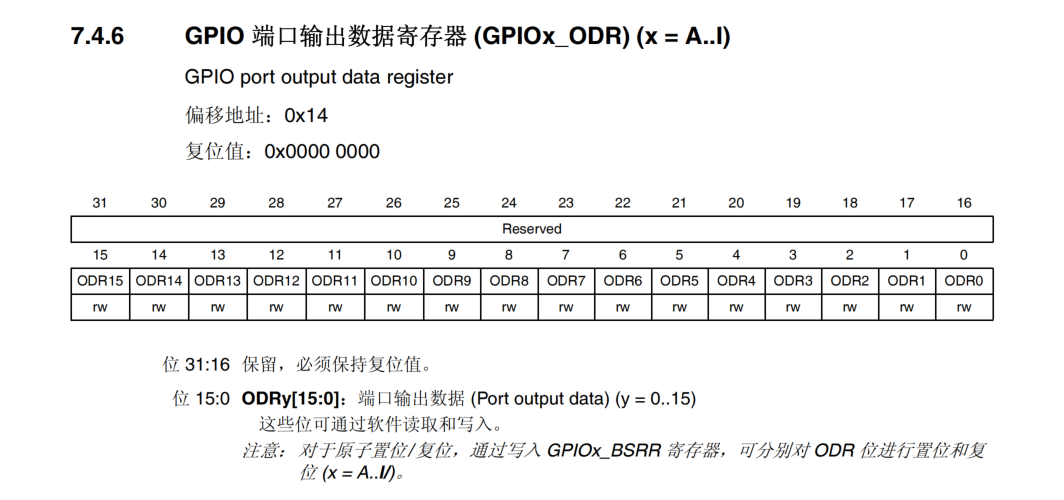

3.3 数据输出

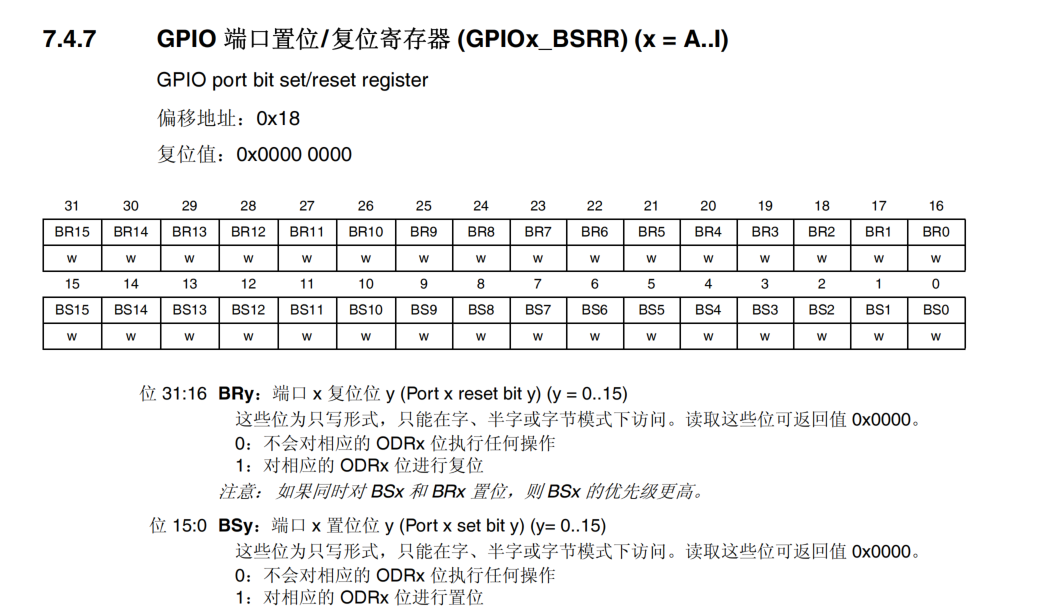

端口置位/复位寄存器

输出数据寄存器

也就是说BSRR寄存器会影响ODR寄存器

3.4 复用功能输出

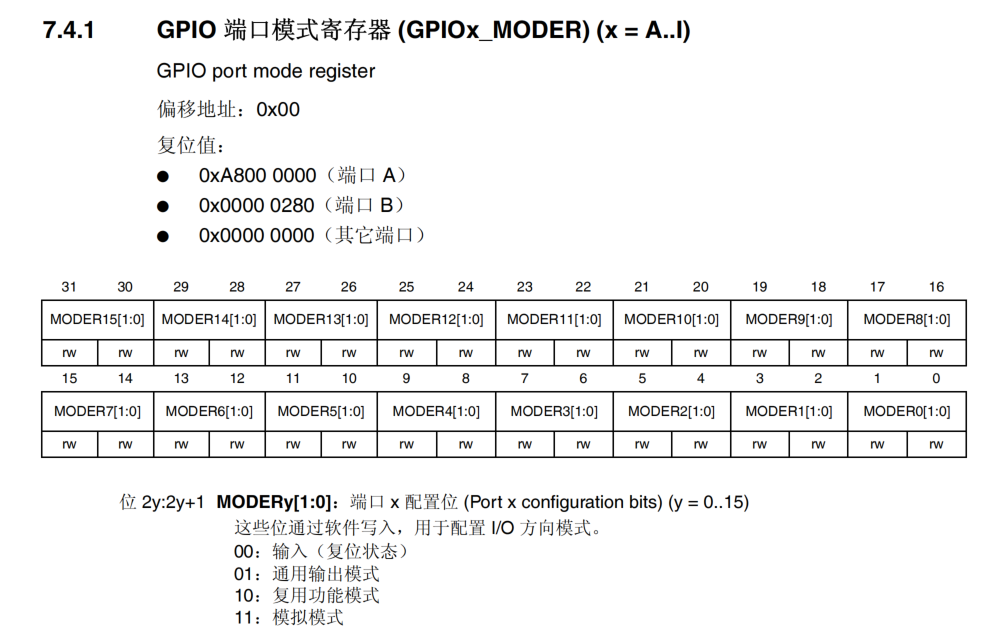

端口模式寄存器

以上说的输出模式都是通用输出模式,复用功能模式的输入输出就是片上的外设来控制IO口了,另外复用输出时,就是片上外设直接控制输出数据寄存器了(ODR),不用置位/复位寄存器了。

3.5 输入数据寄存器

3.6 复用功能输入

下面把 TTL 电平 和 CMOS 电平 讲清楚:它们本质是两套"数字 0/1 怎么判定"的电压门限 和对应的输出能力/输入特性。工程里最重要的是:能不能互连、需不需要电平转换。

1)TTL 电平是什么

TTL 来自早期 5V TTL 逻辑芯片 (74xx 系列等)的标准。它的门限特点是相对固定(不太随电源比例变化),典型(经典 TTL):

输入低(0):VIL ≤ 0.8V

输入高(1):VIH ≥ 2.0V

输出保证(典型):

输出低:VOL ≤ 0.4V

输出高:VOH ≥ 2.4V(注意:不一定到 5V)

特点总结:

高电平判定门限比较低(≥2.0V 就算 1)

输出高电平不必接近 5V

早期 TTL 输入需要一定电流(输入特性与老 CMOS 不同)

2)CMOS 电平是什么

CMOS 是另一类逻辑家族,门限通常跟供电电压 VDD 成比例(不同系列会有差异,但"比例型"是典型特征)。

常见经验值(很多 CMOS/MCU 输入大致如此,具体看 datasheet):

输入低(0):VIL ≤ 0.3 × VDD

输入高(1):VIH ≥ 0.7 × VDD

例如 VDD=3.3V:

低:≤ 0.99V

高:≥ 2.31V

特点总结:

门限随 VDD 变化(3.3V 和 5V 的门限不同)

静态输入电流非常小(高阻输入)

输出高电平通常更接近 VDD("摆幅更满")

3.7 模拟输入输出

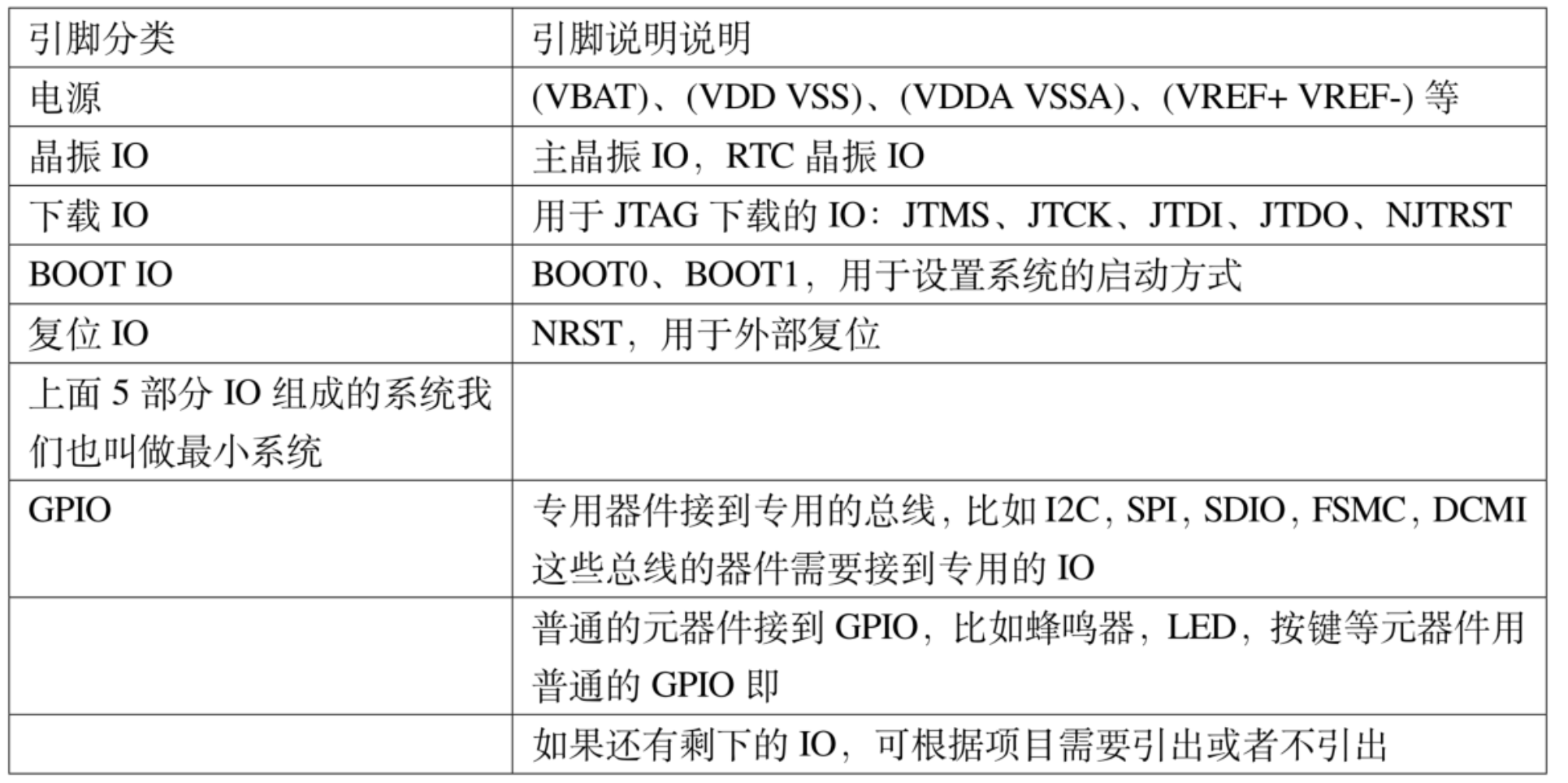

4. GPIO工作模式

4.1 输入模式(上拉/下拉/浮空)

4.2 输出模式(推挽/开漏,上拉/下拉)

4.3 复用功能(推挽/开漏,上拉/下拉)

4.4 模拟输入输出