功能特点

- AEC-Q100 认证

- 2 通道 PSI5 收发器,兼容 rev. 1.3 和 rev. 2.x

- 曼彻斯特编码的数字数据传输

- 高数据传输速率 125 kbps(可选 83.3 kbps 和 189 kbps)

- 高电磁兼容性和低电磁辐射

- 用于同步脉冲的自举电路

- 接口引脚上的电流限制和电压钳位

- 集成的充电泵阶段,采用扩频技术进行预调节

- 集成的 FLL 模块,实现高精度定时控制

- 反向电压保护结构

- 耐短路至地,支持 ±1.5 V 地电位偏移

- 32 位 SPI 接口,具有地址复用功能

- 工作电压:VB = 4.8 V(同步脉冲时为 5.2 V,步进为 3.5 V)至 35 V

- 工作温度范围:-40°C 至 140°C

- 封装形式:VFQFPN28 或 TQFP32EP

描述

外设传感器接口(PSI5)是一种用于汽车传感器应用的接口。PSI5 是基于现有外设传感器接口的开放标准,为多种传感器应用提供了一种通用且灵活的解决方案。

PSI5 接口支持异步或同步操作以及不同的总线模式。该设备兼容 v1.3 和 v2.x 版本的 PSI5(具体限制详见本文档)。它能够支持广泛的传感器供电电流和可变的数据字长(8 到 28 位)。

传感器通过同一线路连接到 ECU,用于电源供应和数据传输。收发器 IC 提供预调节电压给传感器,并读取传输的传感器数据。

PSI5 接口支持点对点连接或总线模式。

目录

1、总体描述

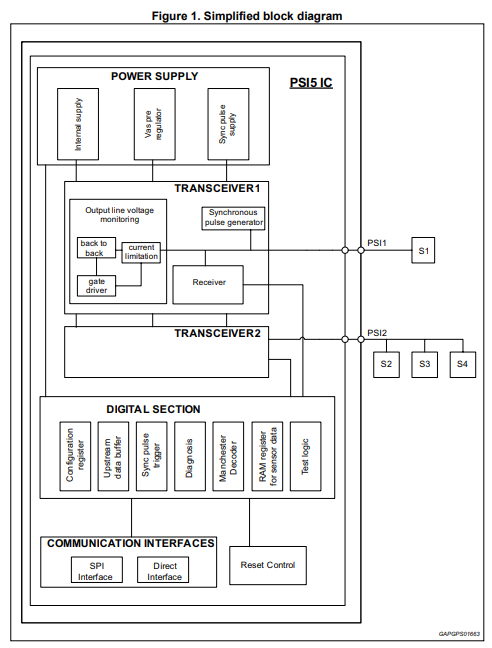

1.1 简化的框图

1.2 主要功能

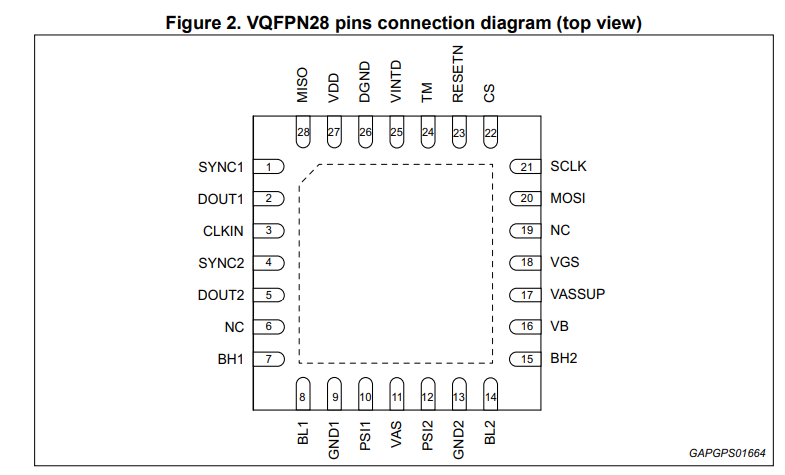

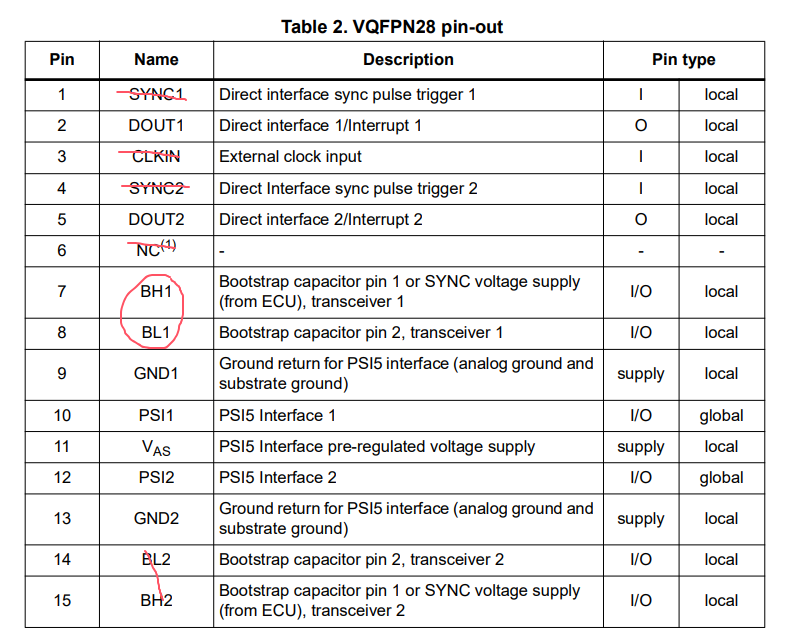

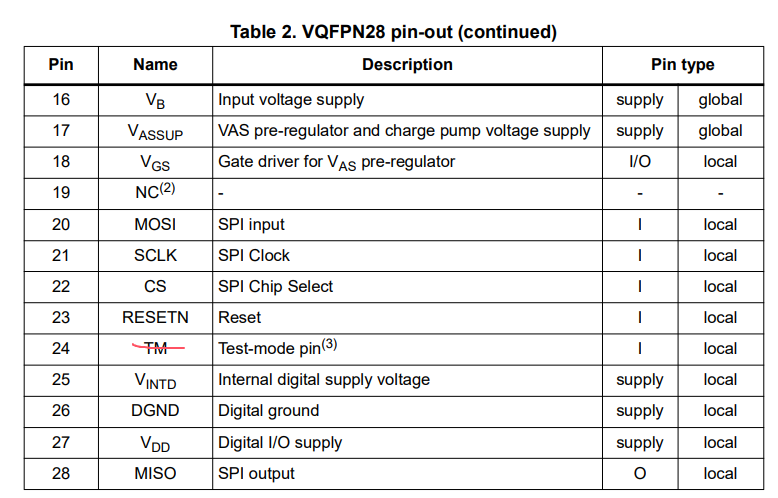

1.3 VQFPN28 引脚描述

1.4 TQFP32 引脚描述

1.5 最大额定值

1.6 详细的框图

1.7 上电顺序

2、电源供应

2.1 内部电源

2.2 VAS 电源与预调节器

2.3 同步脉冲生成电压供应 VSYNCx

2.4 PSI5 传感器线电源供应

2.5 频率参考

2.6 复位处理

3、卫星接口

3.1 数字采样与滤波接收器

3.2 曼彻斯特解码器与错误检测

3.3 接收模块

3.3.1 PSI5 接收寄存器

3.3.2 传感器数据缓冲区

3.3.3 中断生成器

3.3.4 传感器初始化数据的自动存储

3.4 上游数据缓冲区

3.5 同步脉冲的触发脉冲生成器

3.6 同步脉冲生成器

3.7 安全概念

3.7.1 电压监控检查

3.7.2 传感器数据一致性

3.7.3 缓冲区为空检查

3.7.4 DOUTx 路径检查

3.7.5 交叉耦合测试

4、诊断

4.1 PSIx 输出电压钳位电路

4.2 PSIx 输出欠压监控

4.3 PSIx 短路检测

4.4 PSIx 反向电压监控

4.5 VAS 欠压/过压监控

4.6 同步脉冲幅度监控

5、通信接口

5.1 设备寄存器

5.2 SPI 接口

5.2.1 物理层和信号描述

5.2.2 时钟和数据特性

5.2.3 帧定义

5.2.4 通信帧

5.3 直接接口

6、电气特性

6.1 SPI 接口

7、勘误表

8、封装信息

8.1 TQFP32 (7x7x1.0 mm 引脚朝下) 封装信息

8.1.1 形状和位置公差

8.2 VFQFPN-28 (5x5x1.0 mm) 封装信息

修订历史

表格列表

表 1. 设备概述

表 2. VQFPN28 引脚排列

表 3. TQFP32 引脚排列

表 4. 引脚最大额定值

表 5. 时间 (t0-t2) 与传感器数据的关系

表 6. 传感器通信中的错误代码

表 7. 故障优先级

表 8. 时间 (t0-t7) 与传感器数据的关系

表 9. Doutx 测试模式位值

表 10. 工作条件

表 11. VINTx 内部电源

表 12. VAS 电源

表 13. VAS 外部 MOS

表 14. VAS 预调节器

表 15. VSYNCx

表 16. PSI5 输出电源

表 17. PSI5 接收器

表 18. 同步脉冲生成器

表 19. 复位

表 20. VAS 欠压/过压监控

表 21. 同步脉冲幅度监控

表 22. 时隙监控

表 23. 数字 I/O

表 24. 频率参考

表 25. SPI 通信时序

表 26. 直接接口

表 27. 勘误表

表 28. TQFP32 (7x7x1.0 mm 引脚朝下, 5.0x5.0 mm 可选引脚朝下 T1) 封装机械数据

表 29. 形状和位置公差

表 30. VFQFPN-28 (5x5x1.0 mm) 封装机械数据

表 31. 文档修订历史

图 1. 简化的框图

图 2. VQFPN28 引脚连接图(顶视图)

图 3. TQFP32 引脚连接图(顶视图)

图 4. 详细的框图

图 5. PSI5 电源线模型

图 6. 收发器 IC 上电序列

图 7. 内部电源供应与复位生成

图 8. 电源输入结构

图 9. VAS 应用图

图 10. 收发器 1 的框图

图 11. 内部振荡器与外部时钟频率对比

图 12. FLL 时钟误差检测

图 13. 输入数据缓冲区框图

图 14. PSI5 v1.3 帧

图 15. PSI5 v2.0 帧

图 16. 同步模式下的传感器缓冲区图

图 17. 异步模式下的传感器缓冲区图

图 18. 带有中断引脚的框图

图 19. 时序图

图 20. ECU 到传感器的通信图

图 21. 短同步脉冲触发(当 1 µs < tw < 5 µs 时),符合 PSI5 标准

图 22. PSIx 欠电压检测时序

图 23. PSIx 反向电压检测时序

图 24. VAS 欠电压检测时序

图 25. 同步脉冲电压监测时序

图 26. SPI 接口

图 27. 内部寄存器操作(带上游数据缓冲区)

图 28. 初始化数据读取

图 29. 传感器数据读取

图 30. 同步生成器

图 31. SPI 通信时序图

图 32. TQFP32 (7x7x1.0 mm pad down) 封装轮廓

图 33. VFQFPN-28 (5x5x1.0 mm) 封装轮廓 1、总体描述

1.1 简化的框图

1.2 主要功能

该收发器 IC 可以在两种不同的模式下使用(模式1或模式2)。所谓的模式1 配置会在 IC 内部进行传感器信号的解码处理。而模式2 配置则是作为前端设备,连接到外部设备中的 PSI5 解码器(通常是带有专用模块的微控制器)。

该收发器 IC 能够监控所有内部生成的相关电压,例如Vsyncx、Vas和V_psix。

IC 内部的 PSI5 接口通过单独的输入引脚 Vas 供电。如果只需要异步模式,Vas 电压就足够为传感器供电。当需要同步模式时,需要高于 Vas 的电压来生成同步脉冲。该电压 Vsyncx 由每个通道的专用引导电路生成。

对于从电池直接供电的情况,收发器 IC 包含一个由 VASSUP 引脚供电的Vas预调节器:该预调节器可以驱动外部FET,以将VAS电压调节到7.6V或5.3V。如果VASSUP电压较低,则集成了一个由VASSUP供电的电荷泵。

内部的模拟和数字电路由VB供电。VDD引脚上的外部电压用于为数字输出引脚供电;VDD引脚可用于将数字输出从5V输出电平(默认)切换为3.3V输出电平。

PSI5收发器在整个VDD、VB、VASSUP和VAS电源范围内均可正常工作。

内部电压供应(VSYNCx)会根据工作模式自动由收发器IC激活,只要它们需要。

每个收发器接口都可以通过SPI命令进行激活和停用。启动时,接口默认处于关闭状态。

通信接口模块包括两种不同的接口。在模式1中,使用SPI进行数据传输。在模式2中,使用直接接口。来自传感器的数据和传送到传感器的数据将通过逐位传输在收发器IC和微控制器之间进行。数据的评估和帧错误的处理将在集成在微控制器中的PSI5控制器中完成。

收发器1和2为传感器供电,并生成同步脉冲以实现同步数据传输(如果需要)从传感器到收发器,以及从ECU到传感器的数据传输。

从ECU到传感器的数据传输可以通过以下方式进行:

- 使用不同持续时间的同步脉冲(PSI5 2.x标准)

- 屏蔽同步脉冲(PSI5 1.3和2.x标准)

同步脉冲触发可以通过SPI命令生成,通过专用引脚(连接到微控制器中包含的同步脉冲输出块)或通过集成的自动定时器生成。

收发器1和2限制电流和PSIx电压(当VAS电源出现故障时,VAS过高,数据传输电压低于11V或同步脉冲电压低于16.5V,符合PSI5要求)。

从传感器接收到的调制电流信号被检测并进行数字转换。然后,这些传感器数据将:

-

在模式1下,首先通过曼彻斯特解码器模块进行曼彻斯特解码,并进行标记空间误差修正,之后传输到"接收数据缓冲区"模块。新传感器帧中的数据将保存在缓冲区中,然后通过SPI传输到微控制器(µC)。

-

在模式2下,数据直接传输到微控制器。在这种情况下,收发器的输出是未经过误差修正的曼彻斯特编码信号,这部分工作由微控制器负责。

该集成电路(IC)的高压供电来源可以是电池,也可以是由电子控制单元(ECU)提供的稳压电源。为了减少电源电压上的干扰(这些干扰可能会对 PSIx 接口产生负面影响,并导致位错误/误码),可以在电源线上采用 PI 型滤波器( π \pi π 型滤波器)。

配置 1 (标准模式):VB、VASSUP 连接至 VSUP;VAS 和 VSYNCx 由芯片配合外部元件生成(正如您之前上传的框图所示)。

配置 2 (简化模式):VAS、VB、VASSUP 连接至 VSUP;VSYNCx 由自举电路(Bootstrap)生成;不使用外部 MOS 管,VGS 引脚悬空(Open)。

配置 3 (无外部自举电容模式):VB、VASSUP、BH1、BH2 连接至 VSUP;不使用外部电容 CBx;VAS 由芯片预稳压器(Pre-regulator)和外部 MOS 管生成。

配置 4 (外部供电模式):VB 连接至 VSUP;VASSUP 接地(0V,此时电荷泵关闭);VAS 由外部电源供电;VSYNCx 由芯片配合外部元件生成。

当然,以下是对应的中文翻译:

上电时序

当 VDD 高于启动阈值且 VB 可用时,芯片(IC)被开启。

为减少对电源电压的干扰,收发器芯片对其内部电压电源采用分阶段(错峰)启动方式。

当 RESETN 处于低电平时,PSIx 线路被关闭,以降低功耗并提高系统安全性。

该收发器芯片可配置为标准电流模式(4 mA 至 19 mA)或扩展电流模式(4 mA 至 35 mA)。此外,在异步模式下,两个通道都可配置为允许静态电流扩展至最大 45 mA。

同步传感器只有在通过专用引脚或 SPI 触发同步脉冲之后才会发送数据。

根据您提供的 L9663 框图,以下是图中关键术语的中文翻译与功能说明:

- PSI5 通道核心模块 (PSI5 Channels)

PSI#1 main: PSI#1 主模块

current decoder: 电流解码器

high voltage protection: 高压保护

voltage regulation: 电压调节

current limitation: 电流限制

Sync Pulse generator: 同步脉冲发生器(用于触发传感器)

Data Management Logic: 数据管理逻辑

- 诊断与监控 (Diagnostics & Monitors)

PSI1 diagnostics: PSI1 诊断功能

short to high voltage: 对高压短路

overcurrent (stg): 过流(通常指对地短路引起的过流)

leakage to ground: 对地漏电

open load: 负载开路

overtemperature: 过温

VB OV Monitor: 电池电压(VB)过压监控

VAS uv/ov Monitor: VAS 电压欠压/过压监控

- 电源与电压调节 (Power & Voltage Regulation)

VAS pre-regulator: VAS 预稳压器

Soft Start: 软启动

Charge Pump: 电荷泵

VINTA / VINTD regulator: 内部模拟/数字电压调节器

Bandgap (main/monitor): 带隙基准源(主/监控)

- 系统控制与通信 (System Control & Comm)

SPI Module: SPI 通信模块(包含片选 CS、时钟 SCLK、输入 MOSI、输出 MISO)

Direct IF / Interrupt gen: 直接接口/中断发生器

Main oscillator + spread spectrum: 主振荡器 + 扩频技术(用于优化 EMI)

Reset control: 复位控制

Wake Up: 唤醒控制

如果您需要对某个特定引脚(如 VASSUP 或 TM)或更深层的技术名词进行翻译,请随时告诉我。

2.5 频率参考

该设备内置一个精确的振荡器,用于所有内部电路,无需外部连接或组件。其标称时钟频率为16 MHz,准确度为±5%。

如果应用需要更精确的时间参考,可以使用一个独立的引脚 CLKIN。此引脚可以连接外部时钟参考。PSI5收发器IC提供一个集成的 FLL模块,它跟踪此输入信号,以提供高精度的时钟参考(±1%)。这一功能特别适用于需要精确时间槽控制的场合。

CLKIN 上的外部信号可以配置如下(请参考GCR1 SPI寄存器中的CLKIN_CFG位):

1 MHz 方波信号

4 MHz 方波信号

无信号(未连接引脚)

当不使用时,可以将 CLKIN 引脚接地。引脚输入电路实现了一个下拉结构。

默认情况下,跟踪 CLKIN 信号的 FLL 模块是关闭的。

PSI5收发器IC实现了一种安全功能,用于监控设备的时钟参考,无论它是通过FLL模块从 CLKIN 信号派生的,还是内部生成的。在第一种情况下,监控始终是激活的,而在第二种情况下,监控可以通过在ST寄存器中编程(将'1'存储到专用OTP位)启用,另外一个振荡器发生器将用于监控。

当 CLKIN_CFG 被设置时,FLL模块将尝试闭合环路,并使用 T_CKMSK(最大16 ms)作为掩码计数器来计算最大瞬态时间。

在此时间内,无论时钟频率如何,CKER_DETECT 都会被掩蔽,即设备不会检测到时钟错误。

在此时间过后,如果 CLKIN 的频率在正确范围内,环路将被闭合,且时钟频率将在1%的容差范围内;如果 CLKIN 的频率超出了故障检测范围,将在检测时间 T_CKERD 后检测到时钟错误,设备将被重置,并且 CLK_FLT 被设置,使得微控制器可以读取重置源。

T_CKERD 和检测时间期间的瞬态时间取决于 CLKIN 的频率行为;下图显示了内部振荡器相对于外部振荡器的行为。

如果 CLKIN 信号卡住,设备的行为如下图所示:在这种情况下,在检测时间期间,容差仍然保持在1%的容差范围内,直到设备进入复位状态(T_CKERD 最大为 260 µs)。

2.6 复位处理

在复位IC时,考虑了四种不同的源:

POR(上电复位,参见第2.1节)

RESETN 引脚

SW_RESET(软件复位)

CKER_DETECT(时钟错误检测)

当这些复位源被触发时,PSIx线路将被关闭,并且设备寄存器(包括配置寄存器)将被重置为默认值。

除了硬件复位(通过引脚/POR)外,还可以通过软件发起复位(SW_RESET)。

SW_RESET 命令会在满足以下所有条件时发起软复位序列(请参见SPI部分中的DCR寄存器):

解锁状态:这意味着如果未接收到 UNLOCK 命令,SW_RESET 命令将没有效果;

SW_RESET 命令需要在解锁命令的下一个SPI通信中发送。

SW_RESET 会发起软复位序列并重置设备的所有数字部分,除了POR和SR3寄存器中的RST标志。