文章目录

-

- 一、引言

- 二、什么是IP核?

- 三、为什么需要ROM?

- 四、FPGA中的ROM实现方式详解

- [五、如何在Vivado中使用ROM IP核?------详细步骤指南](#五、如何在Vivado中使用ROM IP核?——详细步骤指南)

- 六、实战案例:基于ROM的DDS信号发生器详细实现

- 小结

一、引言

在FPGA设计中,存储器是构建复杂系统的基础模块之一。无论是用于存储初始化数据、缓存中间结果,还是实现特定功能模块(如波形生成器),存储器模型的理解与应用都至关重要。本文将从IP核的概念入手,逐步深入讲解ROM的特性、分类、实现方式及其在实际项目中的应用。

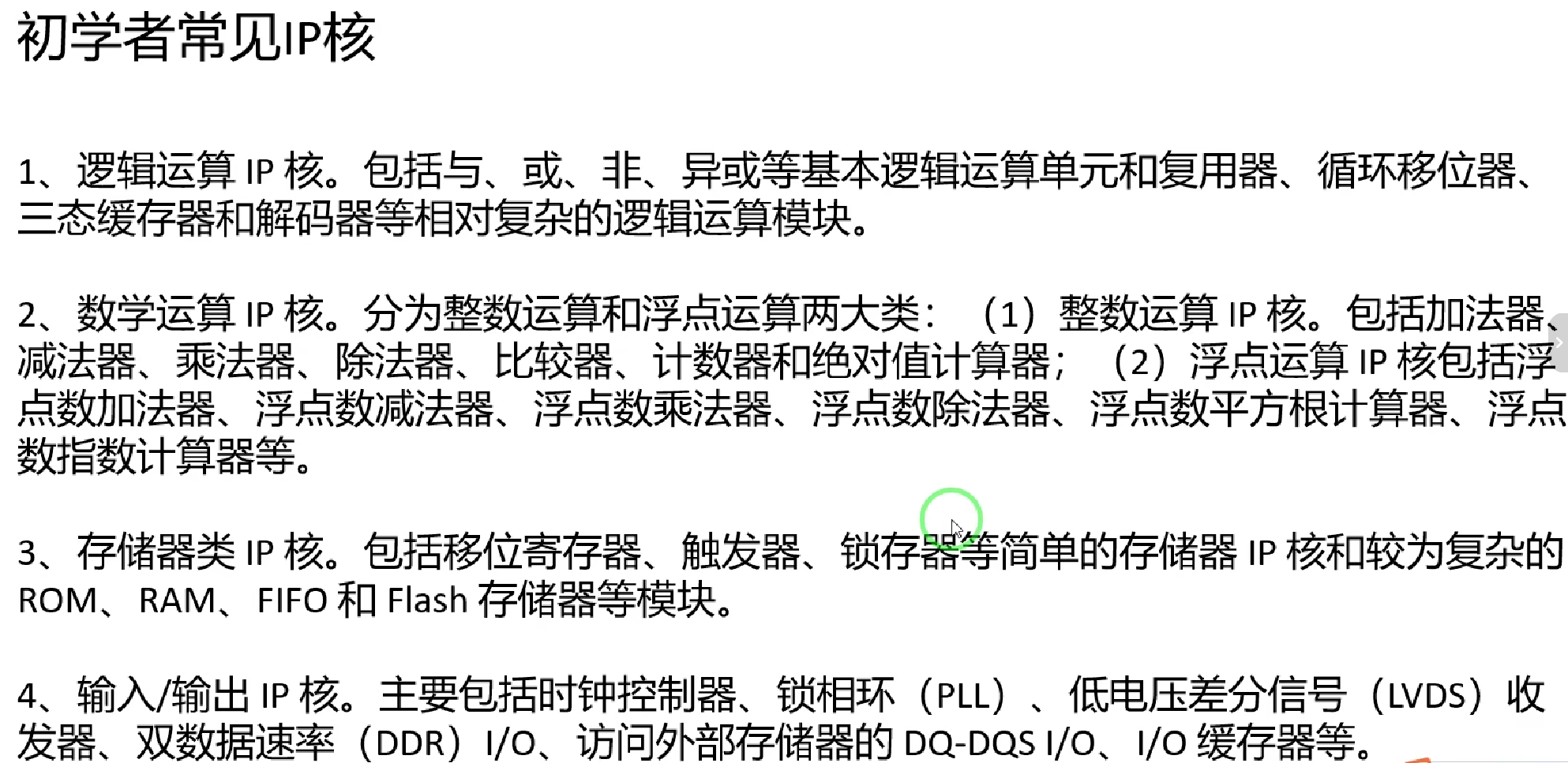

二、什么是IP核?

IP核(Intellectual Property Core)是指芯片中具有独立功能的电路模块的成熟设计,可复用于不同芯片项目中。其核心价值在于:

- 减少设计工作量,缩短开发周期

- 提高设计成功率

- 体现设计者的知识产权属性

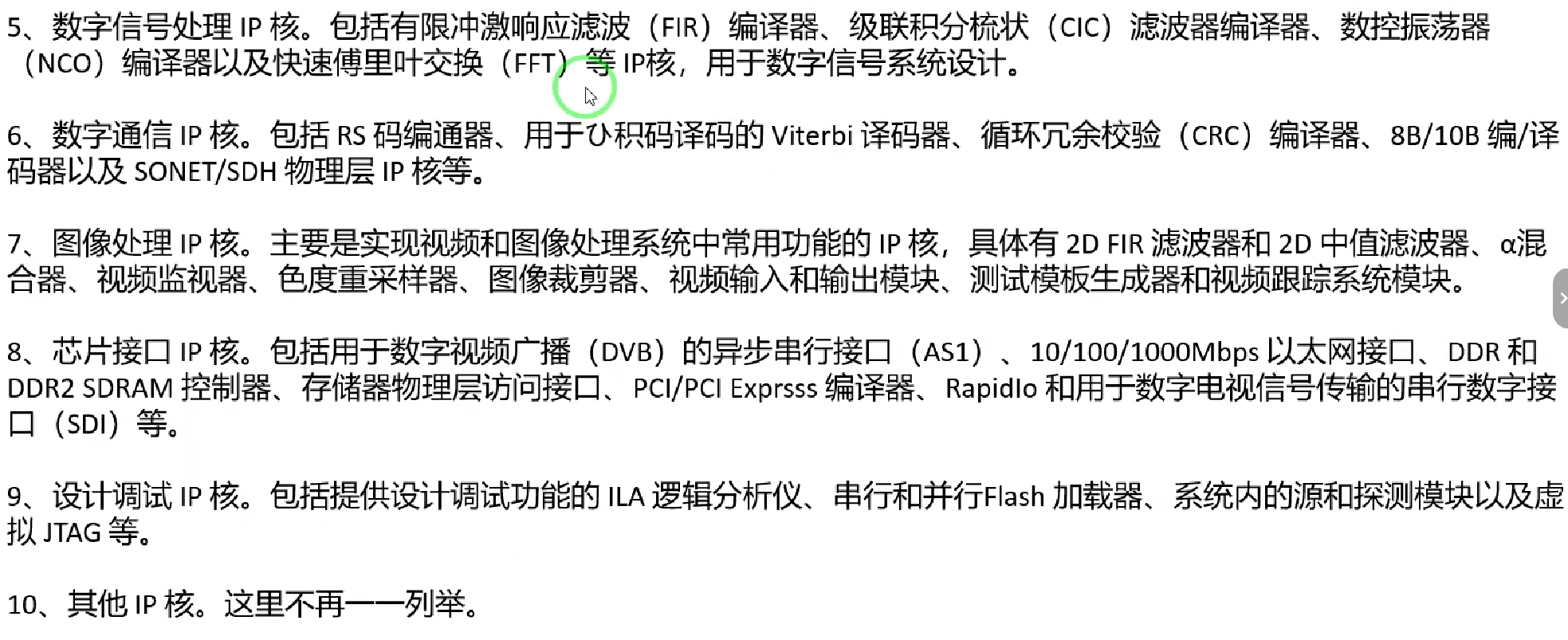

三、为什么需要ROM?

ROM(Read-Only Memory)是一种只读存储器,其数据在写入后不可修改,且断电后数据不丢失。ROM常用于存储固定数据,例如:

- 芯片寄存器的初始值

- DDS信号发生器中的波形数据

- 系统配置参数或查找表

四、FPGA中的ROM实现方式详解

在FPGA中,ROM可以通过两种方式实现,分别是分布式ROM和块存储ROM,它们在使用场景和资源占用上有显著差异。

- 分布式ROM(Distributed ROM)

分布式ROM使用FPGA中的查找表(LUT)资源实现存储功能。每个LUT可配置为一个小型ROM,通常用于存储少量固定数据。

实现原理:利用LUT的可编程特性,将固定数据直接写入LUT的配置位中。

容量特点:单个LUT通常可实现最多64位(6输入)的存储,多个LUT可级联扩展。

适用场景:

- 小容量数据存储(通常小于128字节)

- 需要高度灵活性和动态重构的场景

- 逻辑资源充足但BRAM资源紧张的情况

优势:

- 无需专用存储块,节省BRAM资源

- 可与其他逻辑资源共享LUT资源

- 访问延迟小,通常为组合逻辑延迟

. 块存储ROM(Block RAM ROM)

-

块存储ROM(Block RAM ROM)

块存储ROM使用FPGA中专用的嵌入式存储块(BRAM)实现。这些存储块是FPGA中预置的硬件资源,专门用于存储数据。

实现原理:将BRAM配置为只读模式,通过初始化文件预加载数据。

容量特点:每个BRAM块容量较大(如Xilinx 7系列中每个BRAM为36Kb,可配置为两个独立的18Kb块)。

适用场景:

- 大容量数据存储(几KB到几MB)

- 数据固定且不需修改的应用

- 需要高性能、高带宽的数据访问

优势:

- 容量大,可存储大量数据

- 不占用逻辑资源,不影响其他逻辑功能

- 访问速度稳定,时序可预测

限制:

- 一旦配置为ROM,该BRAM块不能用于其他用途

- 容量固定,可能造成资源浪费

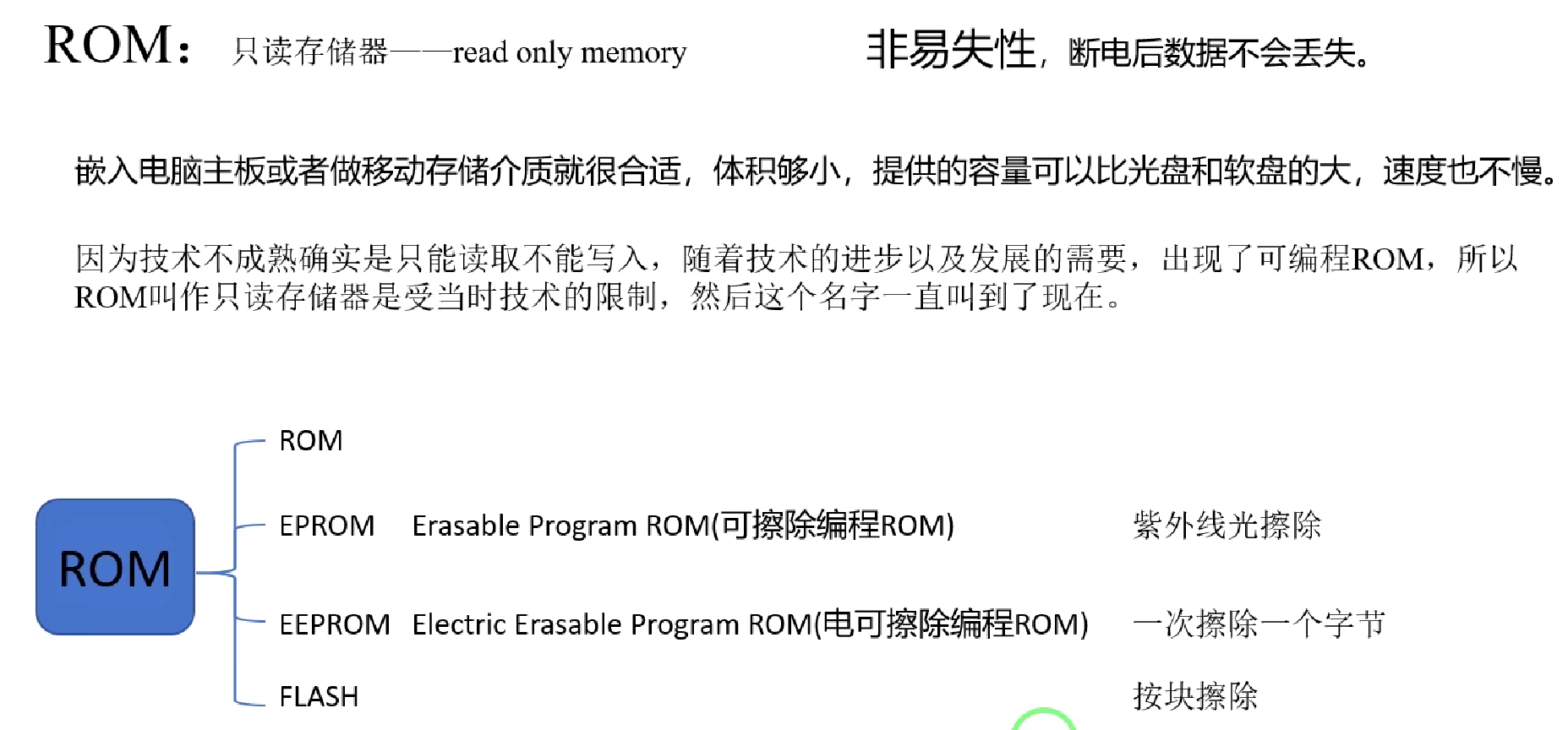

五、如何在Vivado中使用ROM IP核?------详细步骤指南

步骤一:创建ROM IP核

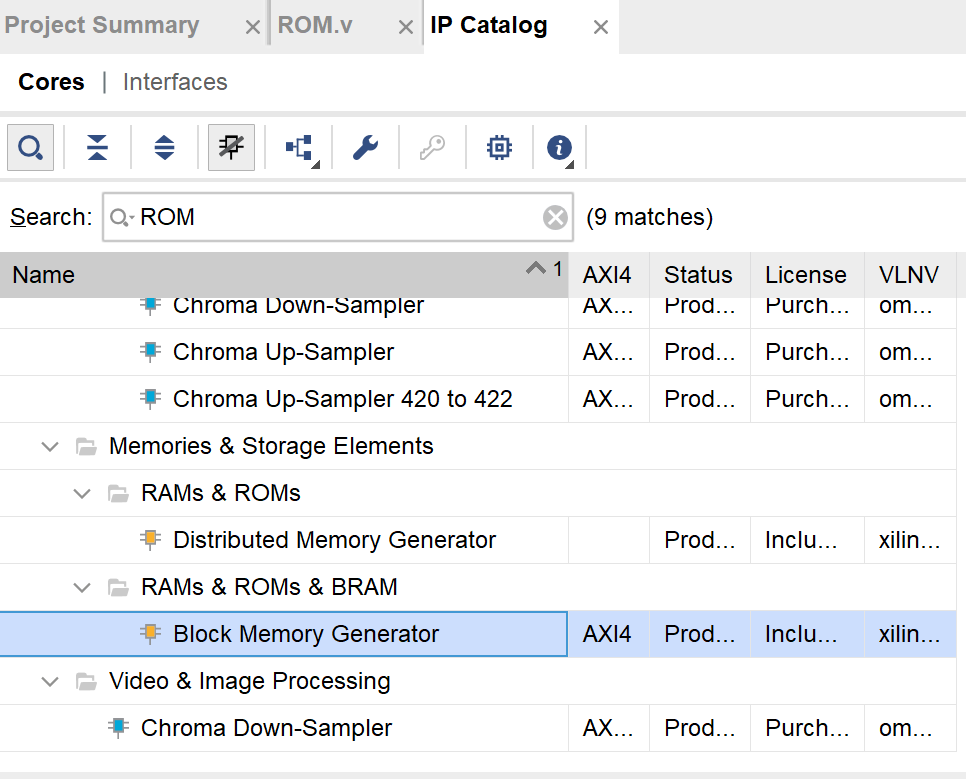

1.打开IP Catalog:在Vivado中,点击"IP Catalog"按钮,打开IP核库界面。

2.搜索ROM IP:在搜索框中输入"Block Memory Generator"或"Distributed Memory Generator"。

3.选择IP类型:双击打开配置界面,在"Basic"选项卡中选择"Memory Type"为"ROM"。

4.配置关键参数:

Port A Options:设置数据位宽(Width)和深度(Depth)

Memory Type:选择"Single Port ROM"

Algorithm Options:可选择"Minimum Area"或"Fixed Primitives"步骤二:配置ROM参数详解

1.接口类型选择:

Native Interface:传统接口,简单易用

AXI4 Interface:标准总线接口,适合SoC系统

2.存储器选项:

Enable Port Type:可选择是否使用使能信号

Output Register:添加输出寄存器可改善时序,但增加延迟

Reset Type:同步复位或异步复位

3.初始化设置:

Load Init File:勾选此项以加载初始化文件

COE File Path:指定COE文件路径

Fill Remaining Memory Locations:设置未初始化地址的填充值

步骤三:创建初始化文件(COE格式)

COE文件是Vivado中常用的存储器初始化文件格式,包含两个主要部分:

c

; 示例:正弦波数据COE文件

memory_initialization_radix = 10; // 数据基数(2,10,16)

memory_initialization_vector =

0,

3212,

6393,

9512,

12540,

15446,

18205,

20787,

23170,

25330,

27246,

28899,

30273,

31357,

32138,

32610,

32767,

32610,

32138,

... // 更多数据点使用Mif精灵生成波形数据:

- 打开Mif精灵软件

- 选择波形类型(正弦、三角、方波等)

- 设置数据位宽(如12位)和深度(如1024点)

- 生成COE文件并保存

步骤四:仿真验证ROM功能

创建测试平台验证ROM功能:

c

module rom_tb;

reg clk;

reg [9:0] addr;

wire [15:0] dout;

// 时钟生成(50MHz)

always #10 clk = ~clk;

// 实例化ROM

rom_ip u_rom (

.clka(clk),

.addra(addr),

.douta(dout)

);

initial begin

// 初始化

clk = 0;

addr = 0;

// 测试地址递增

repeat(1024) begin

@(posedge clk);

addr = addr + 1;

end

// 测试随机地址访问

repeat(100) begin

@(posedge clk);

addr = $random % 1024;

end

$finish;

end

endmodule六、实战案例:基于ROM的DDS信号发生器详细实现

-

DDS原理简介

DDS(Direct Digital Synthesis)技术通过相位累加器、相位-幅度转换和DAC三个主要部分生成任意波形。ROM在其中扮演相位-幅度转换表的角色。

-

系统架构设计

c

module dds_signal_generator(

input clk,

input rst_n,

input [1:0] wave_select, // 波形选择

input [31:0] freq_word, // 频率控制字

output reg [11:0] dac_out // DAC输出

);

// 相位累加器

reg [31:0] phase_acc;

// ROM地址(取相位累加器高位)

wire [9:0] rom_addr;

// ROM数据输出

wire [11:0] sine_data, tri_data, square_data, saw_data;

// 波形选择器

reg [11:0] wave_data;

// 相位累加器更新

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

phase_acc <= 32'd0;

else

phase_acc <= phase_acc + freq_word;

end

// ROM地址生成(取相位累加器高10位)

assign rom_addr = phase_acc[31:22];

// 实例化四个波形ROM

sine_rom u_sine_rom(.clk(clk), .addr(rom_addr), .dout(sine_data));

triangle_rom u_tri_rom(.clk(clk), .addr(rom_addr), .dout(tri_data));

square_rom u_square_rom(.clk(clk), .addr(rom_addr), .dout(square_data));

sawtooth_rom u_saw_rom(.clk(clk), .addr(rom_addr), .dout(saw_data));

// 波形选择

always @(*) begin

case(wave_select)

2'b00: wave_data = sine_data;

2'b01: wave_data = tri_data;

2'b10: wave_data = square_data;

2'b11: wave_data = saw_data;

default: wave_data = sine_data;

endcase

end

// 输出寄存器

always @(posedge clk) begin

dac_out <= wave_data;

end

endmodule- ROM数据生成方法

以正弦波为例,生成COE文件的MATLAB代码:

c

% 生成1024点12位正弦波数据

depth = 1024;

width = 12;

t = linspace(0, 2*pi, depth);

sine_wave = sin(t);

% 归一化到0-4095(12位范围)

sine_data = round((sine_wave + 1) * (2^(width-1)-1));

% 写入COE文件

fid = fopen('sine_wave.coe', 'w');

fprintf(fid, 'memory_initialization_radix=10;\n');

fprintf(fid, 'memory_initialization_vector=\n');

for i = 1:depth-1

fprintf(fid, '%d,\n', sine_data(i));

end

fprintf(fid, '%d;\n', sine_data(end));

fclose(fid);小结

通过本文的详细讲解,你应该对FPGA中的ROM有了深入理解。ROM不仅是简单的存储器,更是实现复杂功能(如DDS)的关键组件。