文章目录

- [1. BJT VS MOS(共射&共源)](#1. BJT VS MOS(共射&共源))

-

- [1.1 共源示例](#1.1 共源示例)

- [1.2 共射示例](#1.2 共射示例)

- [1.3 总结](#1.3 总结)

- [2. BiCMOS技术 & 制造工艺流程](#2. BiCMOS技术 & 制造工艺流程)

-

- 2.1:衬底准备与隐埋层形成 (Step 1 - Step 5)

-

- [Step 1: 基材准备 (P-Substrate)](#Step 1: 基材准备 (P-Substrate))

- [Step 2: 初始氧化 (Oxide Layer Deposition)](#Step 2: 初始氧化 (Oxide Layer Deposition))

- [Step 3: 开口窗口 (Opening in Oxide)](#Step 3: 开口窗口 (Opening in Oxide))

- [Step 4: 重掺杂 N 型隐埋层 (Buried Layer Implant)](#Step 4: 重掺杂 N 型隐埋层 (Buried Layer Implant))

- [Step 5: P 型外延层生长 (P-Epitaxy Growth)](#Step 5: P 型外延层生长 (P-Epitaxy Growth))

- 2.2:隔离与阱区形成 (Step 6 - Step 7)

-

- [Step 6: 二次氧化与双开口 (Re-oxidation & Double Openings)](#Step 6: 二次氧化与双开口 (Re-oxidation & Double Openings))

- [Step 7: N 阱形成 (N-Well Diffusion)](#Step 7: N 阱形成 (N-Well Diffusion))

- 2.3:栅极结构与有源区定义 (Step 8 - Step 9)

-

- [Step 8: 有源区开口 (Three Openings for Active Devices)](#Step 8: 有源区开口 (Three Openings for Active Devices))

- [Step 9: 栅极制造 (Thinox & Polysilicon Patterning)](#Step 9: 栅极制造 (Thinox & Polysilicon Patterning))

- 2.4:源漏与晶体管终端形成 (Step 10 - Step 11)

-

- [Step 10: N 型重掺杂 (N+ Implantation)](#Step 10: N 型重掺杂 (N+ Implantation))

- [Step 11: P 型重掺杂 (P+ Implantation)](#Step 11: P 型重掺杂 (P+ Implantation))

- 2.5:互连与封装准备 (Step 12 - Step 14)

-

- [Step 12: 厚氧化层覆盖 (Thick Oxide Deposition)](#Step 12: 厚氧化层覆盖 (Thick Oxide Deposition))

- [Step 13: 接触孔刻蚀 (Contact Hole Patterning)](#Step 13: 接触孔刻蚀 (Contact Hole Patterning))

- [Step 14: 金属化与端子命名 (Metallization & Termination)](#Step 14: 金属化与端子命名 (Metallization & Termination))

- CG

1. BJT VS MOS(共射&共源)

- 模拟电路中放大器的"共"字取自对输入和输出信号是"公共"的部分(共源极 = 电压放大(反相),共漏极 = 电压跟随(缓冲),共栅极 = 高频/电流放大)。共射极和共源极电路起到类似的作用。两者都是"反相电压放大器",但由于BJT和MOS制作工艺和驱动方式(电压 vs 电流)不同,应用存在差异。

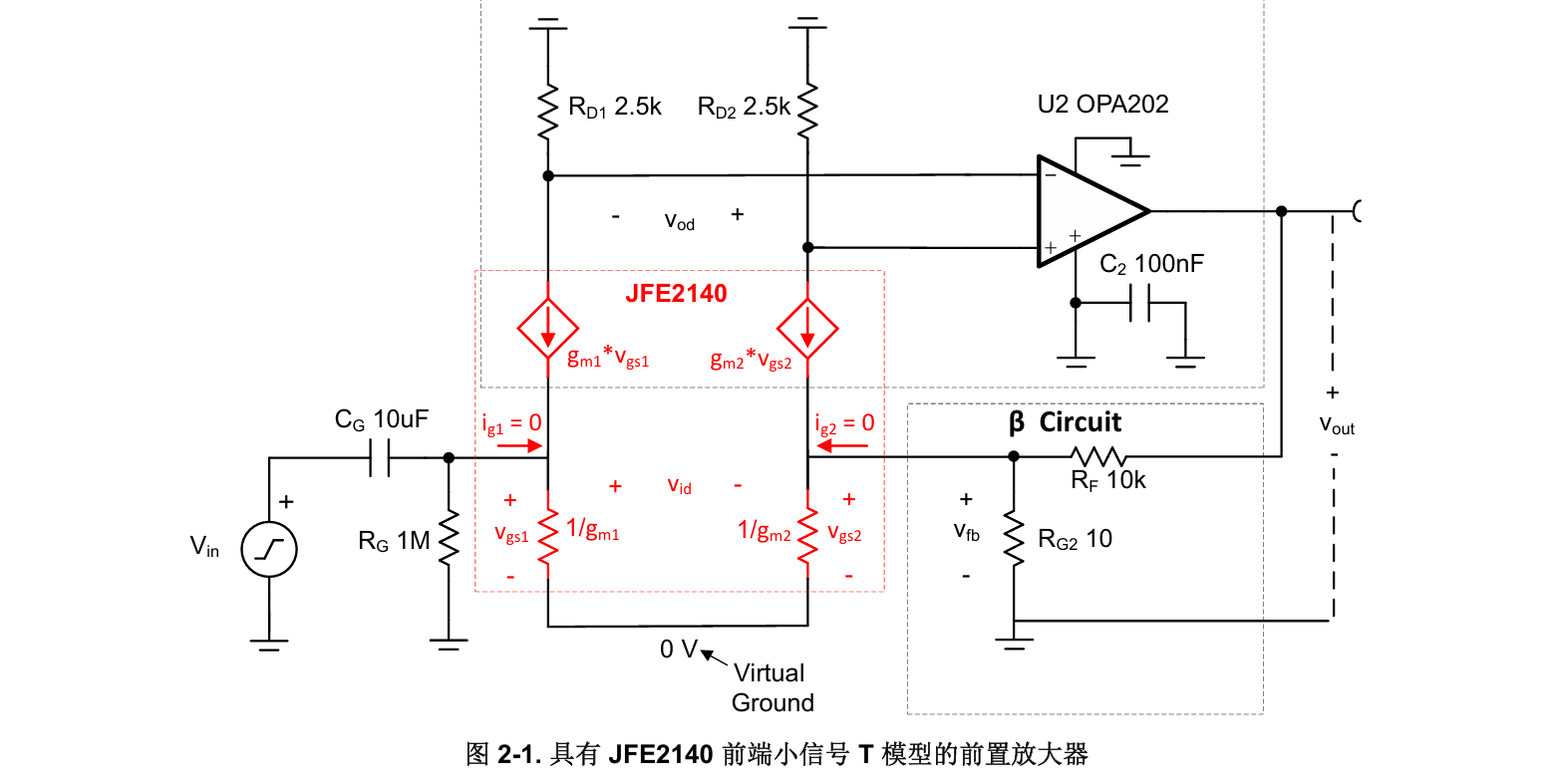

1.1 共源示例

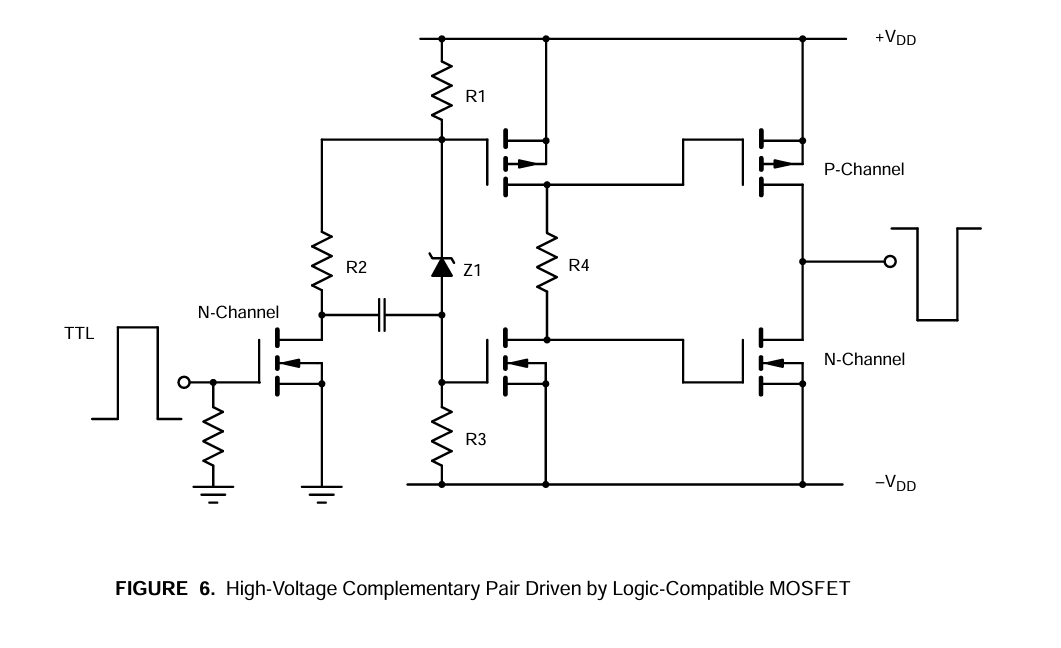

- 在现代功率开关应用中,更多用MOS管(特别是功率 MOSFET)。以下是一个高压互补MOS管驱动电路 (High-Voltage Complementary Pair Driven by Logic-Compatible MOSFET),属于一种典型的功率开关电路。它的作用是将低压逻辑信号(如TTL)转换为可以驱动高压负载的功率输出信号,主要由三部分构成:

- 输入级:N沟道MOS管作为缓冲级,直接接收TTL信号,实现低压逻辑与高压功率级的隔离和阻抗匹配。

- 驱动级:通过电容耦合、稳压二极管(Z1)和电阻网络(R1、R2、R3、R4),将输入信号转换为适合驱动后级的电平,为高压管提供足够的栅极驱动电压。

- 功率输出级:由P沟道和N沟道高压MOS管组成互补推挽结构,能够在高压电源(+V_DD、-V_DD)下输出大电流,驱动高压负载(如高压继电器、高压LED阵列或其他高压功率器件)。

-

第一级的核心作用是:将低压 TTL 控制信号,转换并放大为一个能够有效控制高压偏置网络(Z1)的开关信号,从而实现整个电路在 ±VDD 高压域下的可靠、高效切换。(输出 Output 被钳位在 +VDD 或 -VDD,这两个值是由外部电源决定的,与输入电压的具体数值(只要高于或低于某个阈值)无关。)

-

共射极:输入 10mV 正弦波 → 输出 -1V 正弦波(放大 100 倍,反相),你的电路:输入 5V → 输出 +15V;输入 0V → 输出 -15V(无放大,只是电平搬移) F.6

-

在这个电路里,第一级共源放大使用N沟道MOS管作为输入级,主要有以下几个优势:

-

逻辑电平兼容:它可以直接与TTL等低压逻辑电平无缝对接,无需额外的电平转换电路。MOS管的栅极输入阻抗极高,对TTL输出的负载很轻,不会拉低逻辑电平,也避免了电流驱动不足的问题。

-

高输入阻抗:MOS管的栅极几乎不吸收直流电流,输入阻抗非常高。这意味着前级的TTL电路几乎不需要为它提供驱动电流,有效降低了前级的负载,同时也减少了信号传输中的损耗。

-

快速开关与低功耗:MOS管是电压驱动型器件,开关速度快,适合高频应用。在截止状态下几乎没有静态电流,导通时的功耗也相对较低,有助于提升整体电路的效率和响应速度。

-

信号隔离与保护:结合后续的电容耦合和稳压二极管Z1,这一级可以有效隔离输入逻辑电路与后级高压功率电路。它能防止高压侧的噪声或浪涌反向窜入低压控制端,保护前级TTL电路不受损坏。

-

电平驱动能力:可以将低压的TTL信号转换为适合驱动后级高压互补MOS管的电平,为后级提供足够的摆幅和驱动能力,确保高压功率管能够可靠地导通和关断。

-

1.2 共射示例

-

差分放大器的一半 = 带恒流源负载的共射极电路。如果把差分放大器的另一半去掉,把发射极的恒流源换成一个普通电阻,它就退化成了一个带发射极负反馈的共射极放大电路。正因为本质上是共射极,所以它继承了共射极电压增益高、电流增益高的优点;同时因为它是 "差分" 的,所以它弥补了共射极漂移大、抗干扰差的缺点。

1.3 总结

- BJT 共射极(CE):适合需要高增益、低噪声、中等输入阻抗的分立模拟电路(如音频、传感器)。

- MOS 共源极(CS):适合高输入阻抗、低功耗、大规模集成的IC 和现代电子系统(如手机、SoC、RF 芯片)。

2. BiCMOS技术 & 制造工艺流程

- BiCMOS技术通过融合双极晶体管和CMOS彻底革新了集成电路。这种创新方法挑战了传统晶体管设计的局限。BiCMOS于1983年推出,标志着半导体工程领域的一个关键时刻.

- 结构化的 BiCMOS 工艺 :在同一个 P 型衬底上,同时制造出 NPN 型 BJT 、NMOS 和 PMOS 晶体管(BiCMOS就是同时实现BJT和MOS)

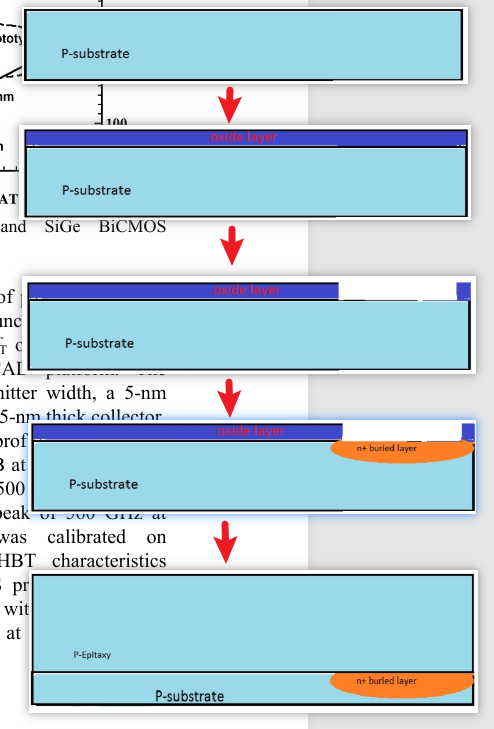

2.1:衬底准备与隐埋层形成 (Step 1 - Step 5)

- 为高性能 BJT 晶体管准备好低寄生电容的集电区。

Step 1: 基材准备 (P-Substrate)

- 操作 :选取高纯度的 P型硅衬底 作为起始材料。

- 目的:提供机械支撑和电学基础。

Step 2: 初始氧化 (Oxide Layer Deposition)

- 操作 :在 P 型衬底表面生长一层二氧化硅( S i O 2 SiO_2 SiO2)。

- 目的 :作为后续掺杂步骤的掩膜,保护不需要掺杂的区域。

Step 3: 开口窗口 (Opening in Oxide)

- 操作:通过光刻和蚀刻,在氧化层上开一个小孔。

- 目的:暴露下方的硅衬底,为注入杂质做准备。

Step 4: 重掺杂 N 型隐埋层 (Buried Layer Implant)

- 操作 :通过开口,向 P 型衬底中重掺杂 N 型杂质(如磷)。

- 目的 :形成 N+ 隐埋层 (Buried Layer) 。

- 技术点:这是 BiCMOS 工艺区别于纯 CMOS 的关键步骤。该层用于降低 BJT 集电极的串联电阻,提高器件的开关速度和频率特性。

Step 5: P 型外延层生长 (P-Epitaxy Growth)

- 操作 :在整个表面(包括隐埋层和氧化层)生长一层 P 型外延层。

- 目的 :

- 这层 P 型外延层将成为 BJT 的基区 和 NMOS 的体区。

- 隐埋层被夹在衬底和外延层之间,形成了 BJT 集电极的一部分。

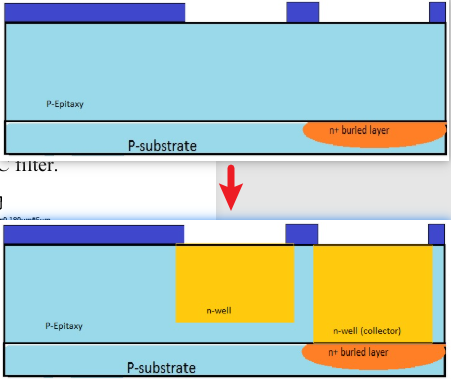

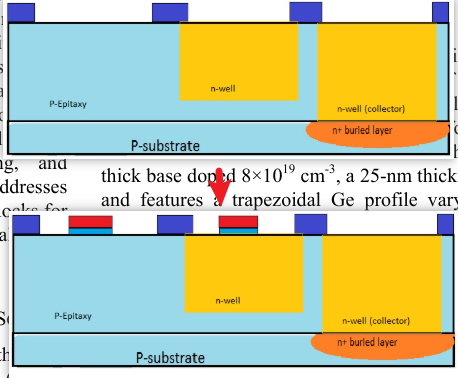

2.2:隔离与阱区形成 (Step 6 - Step 7)

- 为不同类型的器件划分独立的"区域",防止相互干扰。

Step 6: 二次氧化与双开口 (Re-oxidation & Double Openings)

- 操作 :再次在整个表面覆盖氧化层,并光刻出两个开口。

- 目的:定义出 PMOS 和 BJT 集电区的位置。

Step 7: N 阱形成 (N-Well Diffusion)

- 操作 :通过开口扩散 N 型杂质,形成 N-Well(N 阱)。

- 目的 :

- 在 N 阱中可以制造 PMOS 晶体管(因为 PMOS 必须工作在 N 型半导体中)。

- 该 N 阱也作为 BJT 的集电区 (Collector)。

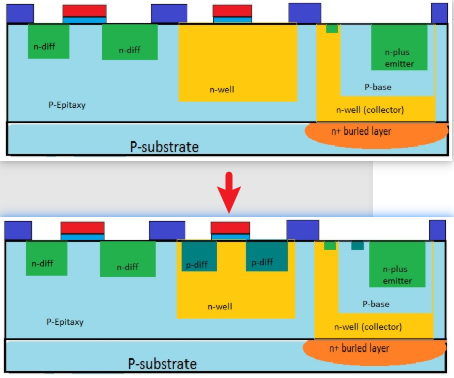

2.3:栅极结构与有源区定义 (Step 8 - Step 9)

- CMOS 制造的核心步骤,同时也为 BJT 确定了基区范围。

Step 8: 有源区开口 (Three Openings for Active Devices)

- 操作 :光刻出三个开口。

- 目的 :分别定义出 NMOS 、PMOS 和 BJT 的有源区域(即将进行晶体管制造的区域)。

Step 9: 栅极制造 (Thinox & Polysilicon Patterning)

- 操作 :

- 生长一层极薄的氧化层(Thinox,即栅氧化层)。

- 沉积多晶硅(Polysilicon)。

- 光刻并蚀刻,形成 NMOS 和 PMOS 的栅极 (Gate)。

- 目的 :

- 建立电压控制的核心结构。

- 注意:BJT 没有栅极,此步骤主要是为 CMOS 器件服务,同时多晶硅层也可作为后续掺杂的阻挡层。

2.4:源漏与晶体管终端形成 (Step 10 - Step 11)

- 过离子注入,完成所有晶体管的"发射极/源极"和"集电极/漏极"制造。

Step 10: N 型重掺杂 (N+ Implantation)

- 操作:注入高浓度 N 型杂质。

- 形成区域 :

- BJT 的发射极 (Emitter):在 P 型外延层(基区)中注入 N+。

- NMOS 的源极和漏极 (Source/Drain):在 P 型外延层中注入 N+。

- N 阱接触 (N-Well Contact):在 BJT 集电区(N 阱)注入 N+,方便后续金属连接。

Step 11: P 型重掺杂 (P+ Implantation)

- 操作:注入高浓度 P 型杂质。

- 形成区域 :

- PMOS 的源极和漏极 (Source/Drain):在 N 阱中注入 P+。

- BJT 的基极接触 (Base Contact):在 P 型基区注入 P+,降低接触电阻。

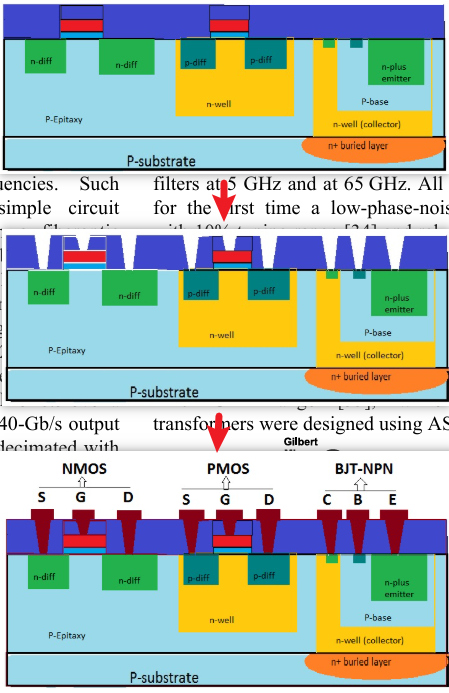

2.5:互连与封装准备 (Step 12 - Step 14)

- 将孤立的器件连接成完整的电路。

Step 12: 厚氧化层覆盖 (Thick Oxide Deposition)

- 操作:沉积一层较厚的氧化层(通常称为场氧化层或 ILD,层间介质)。

- 目的 :作为金属互连层的绝缘层,防止导线短路。

Step 13: 接触孔刻蚀 (Contact Hole Patterning)

- 操作 :在厚氧化层上光刻并蚀刻出接触孔 (Cuts/Vias)。

- 目的:暴露出需要连接的晶体管端子(如 BJT 的 B/C/E,MOS 的 G/S/D)。

Step 14: 金属化与端子命名 (Metallization & Termination)

- 操作 :

- 沉积金属层(铝或铜)。

- 光刻蚀刻形成导线,通过接触孔连接各个器件。

- 引出引脚并命名。

- 目的 :完成电路的互连 (Interconnect),形成最终的 BiCMOS 芯片结构。

CG

- https://www.elprocus.com/bicmos-technology-fabrication-and-applications/

- SiGe BiCMOS for Analog, High-Speed Digital and Millimetre-Wave Applications Beyond 50 GHz

- https://www.tutorialspoint.com/bicmos-technology-fabrication-process-and-applications

- P型晶圆

- IHP 先进半导体技术

- EPIC(电势集成电路)是一种结合电子与光子技术的集成电路,在医疗监护、通信等领域展现重要价值。其非接触式传感特性被用于心电图穿戴装置设计,通过高阻抗和电容耦合实现心电信号采集

- 微机电系统(MEMS, Micro-Electro-Mechanical System),也叫做微电子机械系统、微系统、微机械等,指尺寸在几毫米乃至更小的高科技装置

- 功率工艺 Si / SiC / GaN MOSFET / IGBT

- 化合物半导体 GaAs / GaN HEMT / HBT