一、MOS概述

1.1 什么是MOS管

MOS 是 MOSFET 的缩写。MOSFET 金属-氧化物半导体场效应晶体管。

简称金氧半场效晶体管 (Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET)。

记住 MOS 管有 三个引脚名称:G:gate 栅极;S:source 源极;D:drain 漏极。

简单来说,三极管是电流控制的阻值的电阻,而 MOS 管是电压控制阻值的电阻。

1.2 NMOS 和 PMOS 区分

下图中,左侧是PMOS (PNP 形) ,右侧是NMOS (NPN 形)。箭头向外是 P,朝内是 N。

比较巧妙的记忆办法是放 P 朝外所以是 PMOS。内的拼音是 nei,所以 NMOS 代表内。

1.3 导通方向与导通条件

NMOS 下 G 极高电平导通,低电平断开 ;PMOS 反之,G 极低电平导通,高电平断开。

导通方向与寄生二极管方向相反。

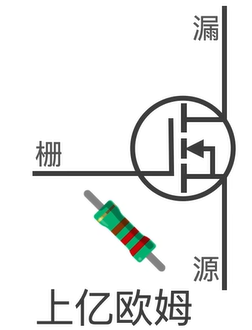

在 MOS 管的栅极和源极中,等效于很大的电阻,所以我们对栅极施加电压并不会消耗电流:

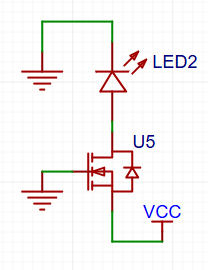

**如果我们顺着寄生二极管方向使用 mos 管,将是一直导通的,**如下图 LED 灯会常亮不受控制:

1.3 MOS 管原理

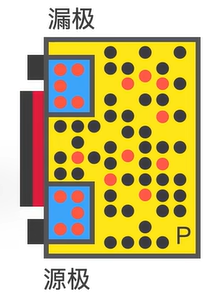

NMOS (NPN 形半导体) 结构如下:

源极和漏极是 N 形半导体,中间夹着 P 型半导体。在 P 型半导体中有一个金属板。

P 型半导体中,电子可以任意方向流动,等价于导体:

下图中,黑色的是空穴,红色的是自由电子,当我们给栅极金属板通电后,自由电子便被吸引过来,下MOS 管便被导通了:

详细的 NMOS (NPN 形) 结构如下:

1.4 寄生二极管

因为工艺原因,一般的 mos 管会自带有一个寄生二极管。 判断规则是,NMOS 中 S 指向 D。PMOS 中 D 指向 S。 从图可以看出 NMOS 和 PMOS 寄生二极管方向不一样:

- NMOS 是由 S 极 → D 极

- PMOS 是由 D 极 → S 极。

寄生二极管和普通二极管一样,正接会导通,反接截止。

- 对于 NMOS,当 S 极接正,D 极接负,寄生二极管会导通,反之截止

- 对于 PMOS,当 D 极接正,S 极接负,寄生二极管导通,反之截止

某些应用场合,也会选择走寄生二极管,以增大 DS 之间的压降 (体二极管的压降是比 MOS 的导通压降大很多的),同时也要关注体二极管的过电流能力。

当满足 MOS 管的导通条件时, MOS 管的 D 极和 S 极会导通,这个时候体二极管是截止状态,因为 MOS 管的导通内阻极小,一般 mΩ 级别,流过 1A 级别的电流,也才 mV 级别,所以 D 极和 S 极之间的导通压降很小,不足以使寄生二极管导通,这点需要特别注意。

二、MOS 的夹断区、恒流区、可变电阻区

2.1 夹断区

= 阈值电压

= 栅源电压

在此区域中,没有形成反型沟道、漏源之间断开、id ≈ 0 (只有微小漏电流)。

2.3 恒流区

= 阈值电压

= 栅源电压

= 栅源电压

在此区域内,随着漏源电压 Vds 的增大,漏极电流 Id 仅略微增大,因此可将 Id 看作是受栅源电压Vgs 控制的电流源,我们根据公式可知:

= 漏极电流

= 栅源电压

= 阈值电压

= 电子移动速度能力常数

可见,在此区域其电流不受到 Vds 电压控制,仅仅是 Vgs 控制。

2.3 可变电阻区

MOS 管工作在可变电阻区。在此区域内,MOS 管相当于一个可变电阻,其阻值受栅源电压 Vgs 控制:

= MOS 的等效导通电阻 (D 和 S 之间的电阻)

= 阈值电压

= 栅源电压

= 漏极电流

= 栅源电压

= 漏极电压

= 阈值电压

= 电子移动速度能力常数

2.4 输入特性曲线分析

三、MOS 雪崩

3.1 什么是 MOS 雪崩

当漏源电压 VDS 超过器件耐压时,PN 结被强电场击穿,产生大量载流子倍增,电流突然暴增的现象。

它发生在漏极---体区的 PN 结,也就是 MOS 内部的体二极管区域。

对 N 沟道 MOS 来说:漏极区域是 N+,体区是 P。形成一个反向偏置 PN 结。当:

= 漏极电压

= 漏极-体区击穿电压

这个 PN 结被击穿。

当 VDS 超过击穿电压后,MOS 不再是关断而是进入击穿区,像一个齐纳二极管一样钳位电压此时,电压稳定在某个值,电流继续流,器件内部发热。

3.2 为什么叫雪崩?

因为电流增长方式像雪球一样:

- 电压升高

- 电场变强

- 少量电子被加速

- 撞击晶格 → 产生新的电子空穴对

- 新电子再被加速

- 再撞击 → 再产生更多电子

四、米勒平台

4.1 米勒平台是什么

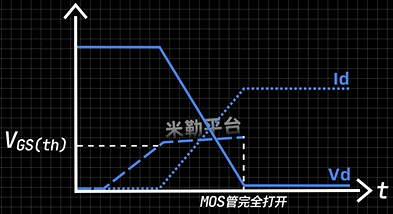

米勒平台 (Miller Plateau) 是指:

在 MOSFET 开通过程中,栅极电压上升到某个区间时,会出现一段电压几乎不再上升的平台区。

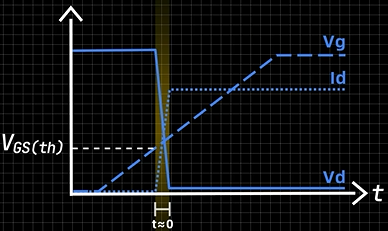

如下图所示,Vgs 的波形并没有比较平稳的上升,而是在上升一段时间会出现一个台阶状的东西,这个我们称之为米勒平台:

Vgs 波形

Vgs 波形

在 MOS 开通时:

- VGS 从 0V 开始上升

- 达到阈值电压 Vth (开始导通)

- 漏极电流开始上升

- 漏极电压开始下降

**就在第 4 步:**VGS 会停在一个平台区。这段电压就是,米勒平台电压。

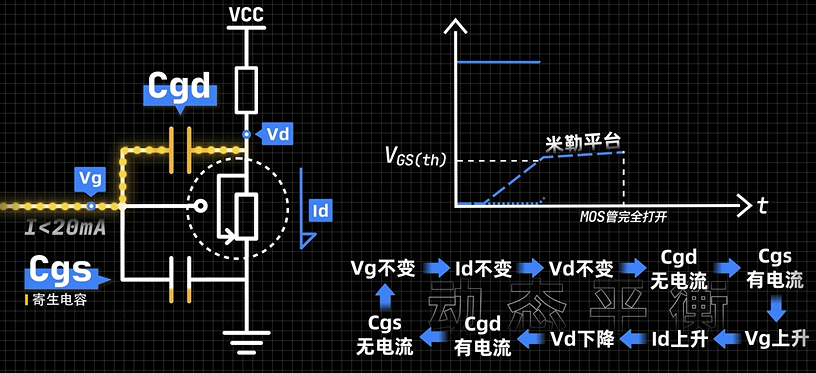

4.2 原因分析

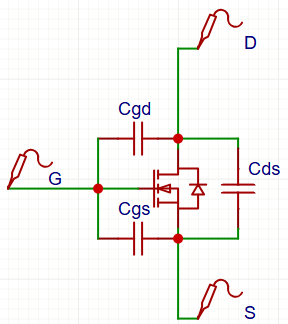

因为工艺问题,MOS 存在三个寄生电容:

如果我们只考虑 Cgs 的影响,我们的波形会是这样子:

= 缓慢上升至峰值 (给 Cga 充电)

= 在 Vgs 达到 Vth 后快速上升 (因为开管导通)

= 在 Vgs 达到 Vth 后快速下降 (因为开管导通)

如果我们加入了 Cgd 情况就完全不一样了:

在 MOS 处于恒流区和可变电阻区时,Vd 的电压开始变化,根据电容的充放公式:

= 电容的电容量 (F)

= 流过电容的电流 (A)

= 电容两端的电压 (V)

= 电压随时间变化的速率,即电压的导数

此时,开始有电流给 Cgd 充电,因为这个原因,所以导致了米勒平台。

更完整的米勒平台示例如下:

五、MOS 管参数详解

3.1 Nexperia 2N7002 数据手册

一般描述

采用沟槽型 (Trench) MOSFET 工艺的 N 沟道增强型场效应管,塑封封装。

特点与优势

- 适用于逻辑电平驱动

- 开关速度非常快

- 表面贴装封装

- Trench MOSFET 工艺

应用

- 逻辑电平转换

- 高速线驱动

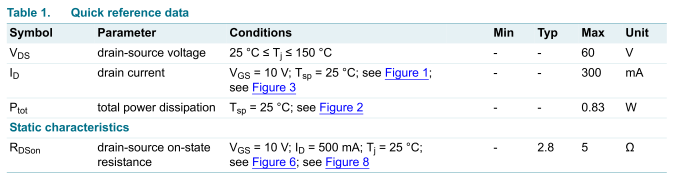

3.2 快速参考数据 (Quick reference data)

3.2.1 VDS (漏源电压)

- 定义:漏极到源极之间的最大电压

- 条件:在结温 (Tj) 为 25℃ 到 150℃ 的范围内

- 数值:最大 60V,表示在这个电压范围内工作时 MOSFET 是安全的

3.2.2 ID (漏极电流)

- 定义:MOSFET 中流过漏极到源极的电流

- 条件:栅极到源极的电压 (VGS) 为 10V,封装表面温度 (Tsp) 为 25℃

- 数值:最大 300 mA,表示在此条件下,漏极电流最大为 300毫安

3.2.3 Ptot (总功耗)

- 定义:MOSFET 在工作时消耗的总功率

- 条件:封装表面温度为 25℃

- 数值:最大 0.83W,表示该 MOSFET 在额定条件下消耗的最大功率为 0.83 瓦特

3.2.4 RDS (on)

- 定义:当 MOSFET 完全打开 (导通状态) 时,漏源之间的电阻

- 条件:栅极电压 (VGS) 为 10V,漏极电流 (ID) 为 500mA

- 数值:典型值 2.8Ω,最大值 5Ω

- 这表示在导通时,电阻通常为 2.8Ω,但在最坏情况下可高达 5Ω。较低的导通电阻可以减少功耗,提高效率

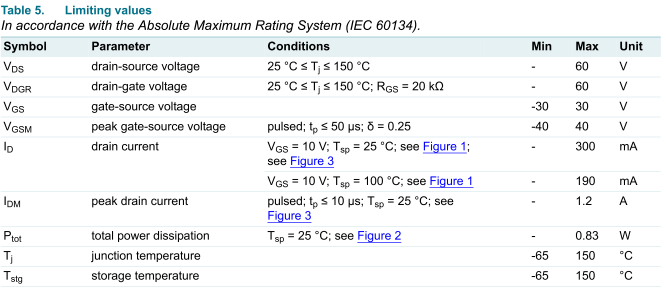

3.3 极限值 (Limiting values)

3.2.1 VDS 最大漏源电压

- 定义:漏极 (D) 到源极(S) 之间允许承受的最大电压

- 条件:结温 (Tj) 在 -65℃ ~ 150℃ 范围内

- 数值:最大 60V

- 表示漏源之间电压不能超过 60V,否则可能发生击穿损坏

3.2.2 VDGR 漏栅电压

- 定义:漏极 (D) 到栅极 (G) 之间允许的最大电压

- 条件:Tj 在规定范围内,RGS = 20kΩ

- 数值:最大 60V

- 表示漏极与栅极之间的电压不能超过 60V,否则可能影响栅极结构安全

3.2.3 VGS 栅源电压

- 定义:栅极 (G) 到源极 (S) 之间允许的最大电压

- 条件:直流或正常工作状态

- 数值:±30V

- 表示栅源电压不能超过 +30V 或 -30V,否则可能击穿栅氧化层

3.2.4 VGSM 峰值栅源电压

- 定义:栅源之间允许承受的短时间脉冲最大电压

- 条件:脉冲宽度 ≤ 50µs,占空比 0.25

- 数值:±40V

- 表示在短时间瞬态冲击下可承受 ±40V,但不能长期维持

3.2.5 ID 最大连续电流

- 定义:在 25℃ 条件下,允许连续流过漏极的最大电流

- 条件:VGS = 10V,封装焊点温度 Tsp = 25℃

- 数值:300mA

- 表示在此条件下可持续通过 300mA 电流而不超过热限制

3.2.6 ID 高温最大连续电流

- 定义:在较高温度下允许的最大连续漏极电流

- 条件:Tsp = 100℃

- 数值:190mA

- 表示温度升高后,允许电流下降

3.2.7 IDM 峰值电流

- 定义:允许的短时间脉冲最大漏极电流

- 条件:脉冲宽度 ≤ 10µs,Tsp = 25℃

- 数值:1.2A

- 表示瞬间可以通过 1.2A,但不能持续

3.2.8 Ptot 最大功耗

- 定义:MOSFET 内部允许的最大总功率损耗

- 条件:Tsp = 25℃

- 数值:0.83W

- 表示器件发热功率不能超过 0.83W,否则结温会超过安全范围

3.2.9 Tj 结温

- 定义:芯片内部 PN 结的工作温度范围

- 条件:正常工作状态

- 数值:-65℃ ~ 150℃

- 表示芯片内部温度必须在此范围内

3.2.10 存储温度

- 定义:器件未通电时允许的存储环境温度范围

- 条件:无电工作状态

- 数值:-65℃ ~ 150℃

- 表示运输、仓储环境必须在此范围内

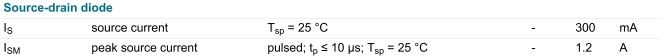

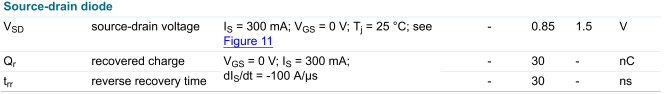

源漏二极管 (Source-drain diode)

3.2.11 IS 连续电流

- 定义:源极电流(通过体二极管时)的最大连续电流

- 条件:Tsp = 25℃

- 数值:300 mA

- 表示当 MOSFET 的体二极管导通时,可以连续通过 300mA 电流而不超过热限制。这里的 IS 实际是体二极管的电流能力,不是正常沟道导通电流。

3.2.12 ISM 峰值电流

- 定义:源极电流的最大脉冲值 (体二极管瞬时电流)

- 条件:脉冲宽度 ≤ 10µs,Tsp = 25℃

- 数值:1.2 A

- 表示在极短时间内,体二极管可以承受 1.2A 的电流冲击,但不能持续。

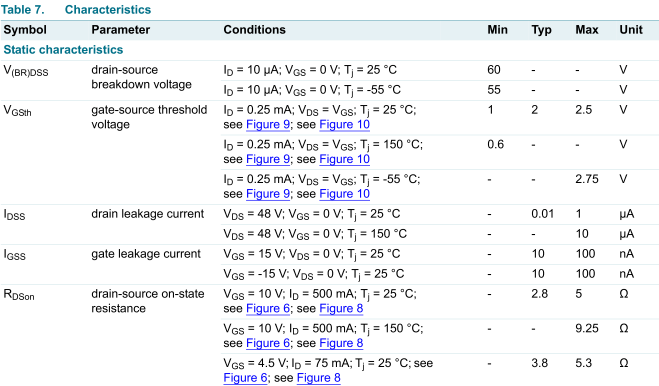

3.4 特点 (Characteristics)

3.4.1 V(BR)DSS 漏源击穿电压

- 定义:在 VGS = 0 时,漏源之间发生击穿的电压

- 测试条件:ID = 10µA,VGS = 0

- 数值:最小 60V

- 当栅极不加电压 (关断状态) 时,漏源电压升到 60V 才会开始击穿

3.4.2 VGS(th) 栅极阈值电压

- 定义:MOSFET 刚刚开始导通时的栅源电压。

- 测试条件:ID = 0.25mA,VDS = VGS

- 数值:最小 1V、典型 2V、最大 2.5V

3.4.3 IDSS 漏极漏电流

- 定义:关断时(VGS=0)漏源之间的漏电流

- 条件:25℃ 最大 1µA、150℃ 最大 10µA

- 关断状态下仍然会有极小电流流过。温度越高,漏电越大

3.4.4 IGSS 栅极漏电流

- 定义:栅极的漏电流

- 条件:VGS=±15V

- 数值:最大 ±100nA

- 栅极是绝缘结构,电流极小。但不是完全为 0

3.4.5 RDS(on) 导通电阻

- 定义:MOS 完全导通时的漏源电阻。

- 测试条件与数值 (栅压越高 → 电阻越小,温度越高 → 电阻越大)

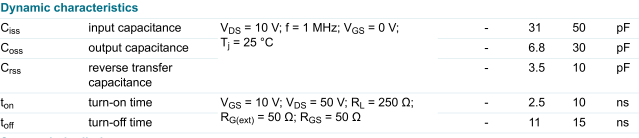

动态特性 (Dynamic characteristics)

3.4.6 Ciss 输入电容

- 定义:栅极看到的等效电容

- 数值:31pF

- 影响:决定驱动电流需求和开关速度

公式:

也就是说,电容越大需要更大驱动电流。

3.4.7 Coss 输出电容

- 定义:漏源之间的等效电容

- 数值:6.8pF

- 影响:决定开关损耗和 dv/dt 行为

3.4.8 Crss 反向传输电容

- 定义:漏极到栅极的耦合电容 (米勒电容)

- 数值:3.5pF

- 影响:产生米勒平台、影响开关速度、可能导致误导通

3.4.9 Ton 开通时间

- 定义:从栅极加电到电流完全导通的时间

- 数值: ton = 2.5ns

- 数值:典型 2.5ns

- 说明:这是一个非常快的开关管

3.4.10 Toff 关断时间

- 定义:栅极撤掉电压到完全关断的时间

- 数值:toff = 11ns

源漏 (体) 二极管 (Source-drain diode)

3.4.11 VSD 正向压降

- 定义:体二极管导通时的压降

- 条件:IS=300mA

- 数值:典型 0.85V

- 说明:当电流反向流动时,会走体二极管路径

3.4.12 trr 反向恢复时间

- 定义:二极管从导通变为关断所需时间

- 数值:30ns

四、应用案例

3.1 简单开关应用

NMOS 中 Rgs 电阻下拉使其在没有信号时工作在夹断区:

= 阈值电压

= 栅源电压

PMOS 中 Rgs 电阻上拉使其在没有信号时工作在夹断区:

= 阈值电压

= 栅源电压

3.1 推挽电路

推挽晶体管电路是一种电子电路,使用以特定方式连接的有源器件,可以在需要时交替提供电路并从连接的负载吸收电流,用于向负载提供大功率,也被称为推挽放大器。

3.2 缓启动开关电路

缓启动开关电路,在电路基础上,加一个电容就可以了,利于电容电压不能突变的特性,也就是G从高电压到ov的时间会长一点,起到V0UT缓启动的目的,防止大的浪涌电流损坏VOUT后端负载。

3.3 反相器复位电路

VUSB 是 usb 口的外部电,VDD_node_A 是整个系统所有的供电(除CH340外,可以去看看)。

其中 Q1 是PMOS 低电平导通,并且常接下拉。常导通状态。

也就是说,按下 SW1 后 PMOS 不导通。系统全部掉电。其 SW1 不摁下是开路的,按下暂时短路。

3.3 H桥电机驱动电路

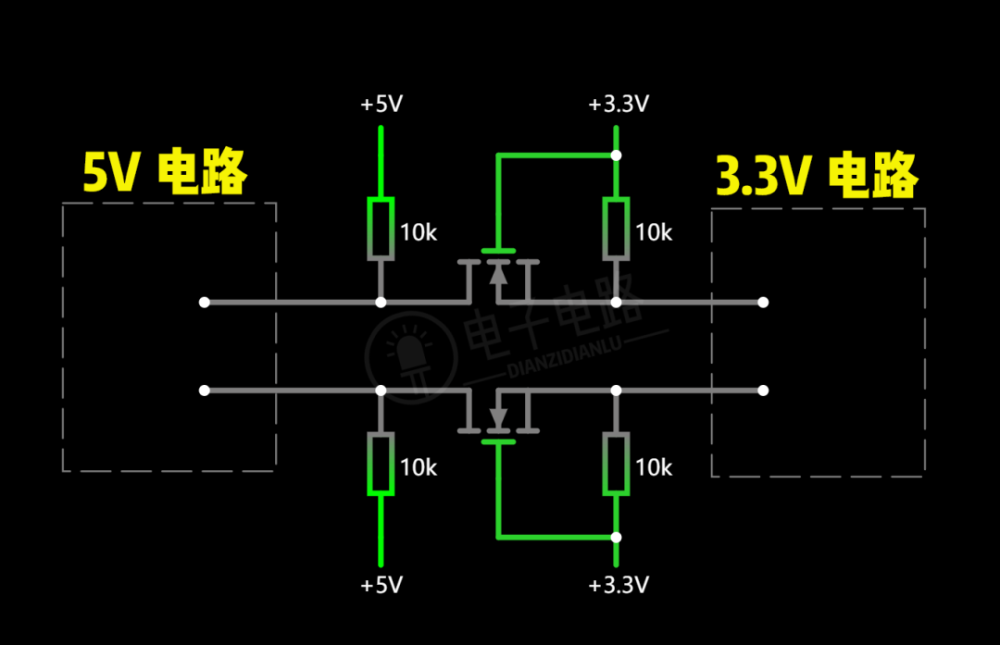

4.5 电平转换电路