AGM32包含MCU+2K CPLD,价格也比较好,记录CPLD开发流程,本次只用Supra软件,使用native编译,不使用quartus.

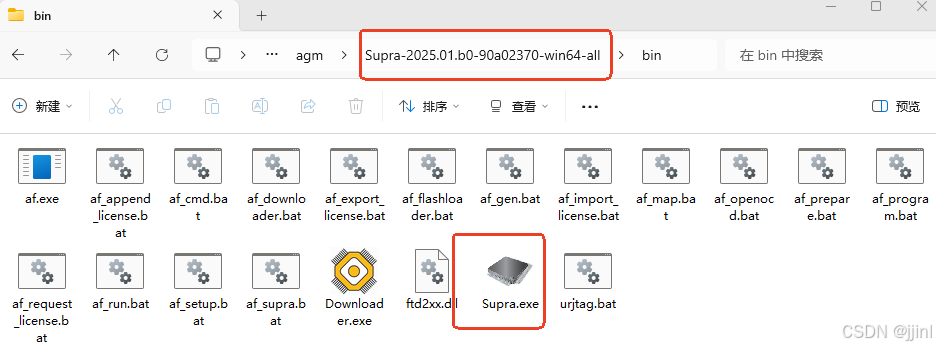

软件版本:Supra-2025.01.b0-90a02370-win64-all

软件到官网下载.

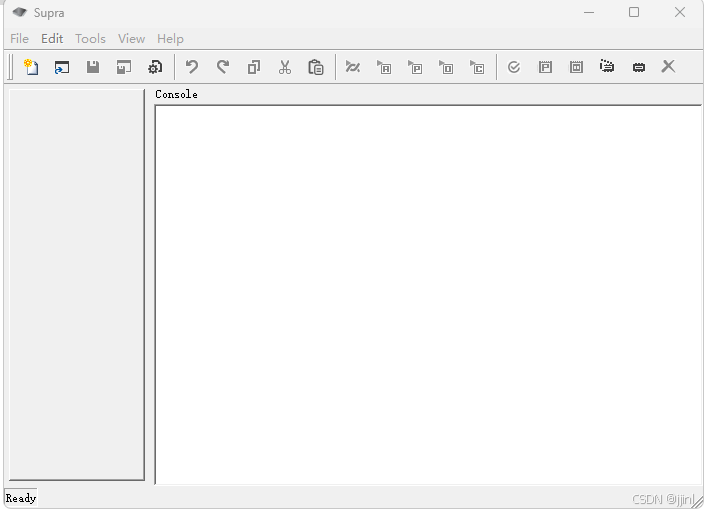

1.解压软件,运行Supra

弹出的界面比较简洁

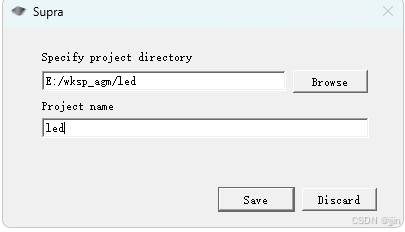

创建工程,选择File菜单--> Project --> New Project,在弹出的对话框中选择工程文件夹目录和工程名字,我这里创建一个led工程,我开发板上有4个led可用于测试。输入完毕后点击save即可,在弹出对话框点击OK即可

准备verilog代码文件,led.v,内容如下:

verilog

module led(

input sys_clk,

input sys_rst,

output [3:0] led

);

reg [24:0] cnt;

always @(posedge sys_clk or negedge sys_rst)

if(~sys_rst)

cnt <= 25'h0;

else

cnt <= cnt + 25'h1;

assign led[0] = cnt[24];

assign led[1] = cnt[23];

assign led[2] = cnt[22];

assign led[3] = cnt[21];

endmodule准备管脚分配文件 led.ve ,内容如下,管脚分配按照原理图进行修改。对于cpld模块中管脚如果不指定方向,默认为INOUT,文档是这样说的。

SYSCLK 100

HSECLK 8

BUSCLK 50

sys_clk PIN_2:INPUT

sys_rst PIN_11:INPUT

led[0] PIN_10:OUTPUT

led[1] PIN_9:OUTPUT

led[2] PIN_8:OUTPUT

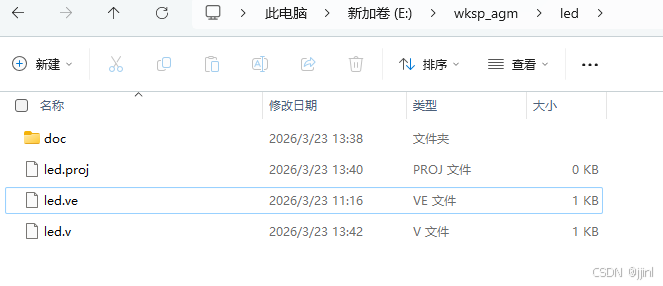

led[3] PIN_62:OUTPUT最终项目文件结构如下:

现在开始编译这个工程。

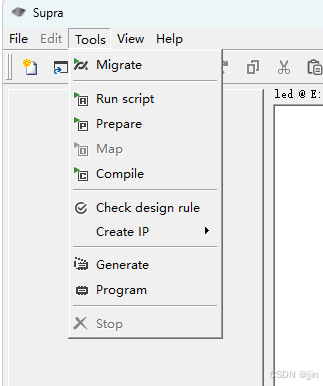

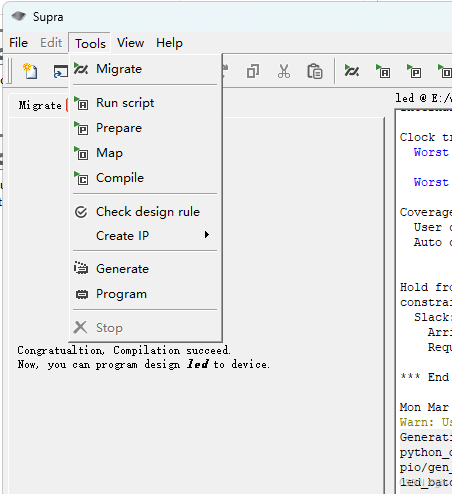

首先选择Tools -->Migrate 选项

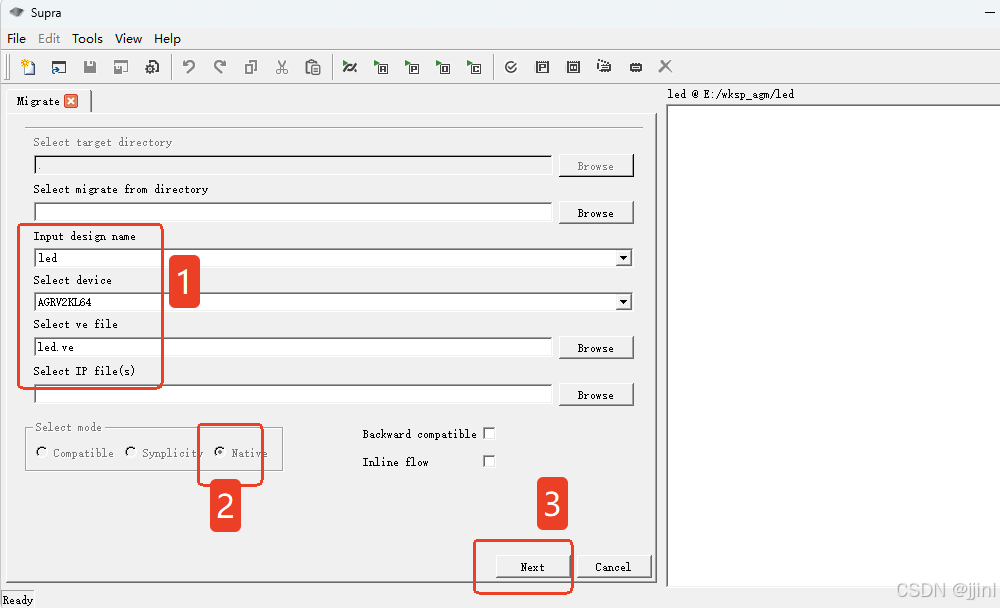

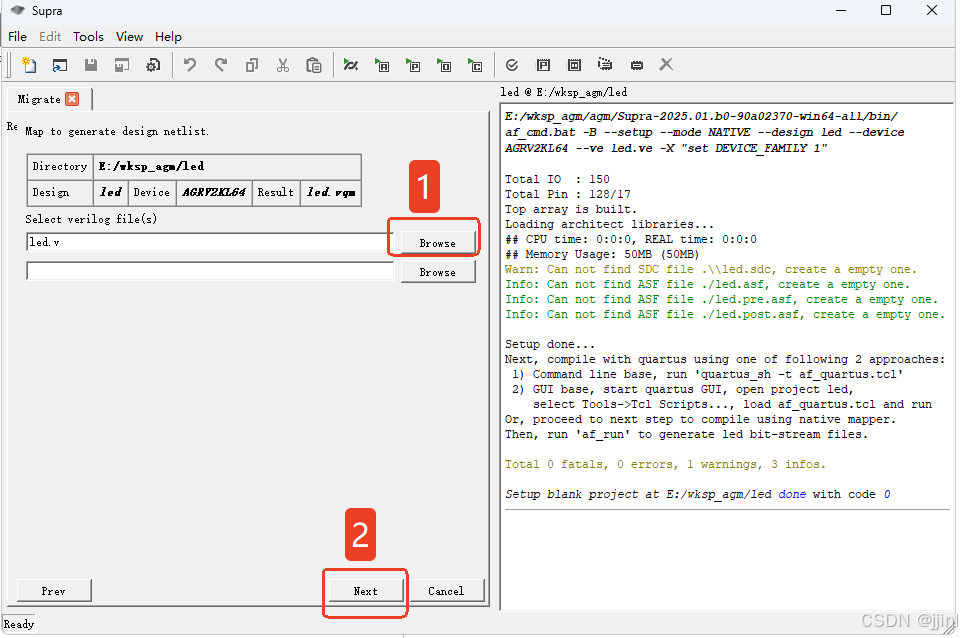

之后会出现如下界面,按照图中标识顺序填写或者检查,Input design name,输入你的顶层模块名字,根据芯片封装选择设备AGRV2KLxxx,注意选芯片型号时,还可以继续往下滚动,下拉列表不能一次把所有型号显示完!!!,?Select ve file,选择刚刚编写的ve文件,检查模式是否为Native,最后点击Next,最右边会显示命令调用过程。

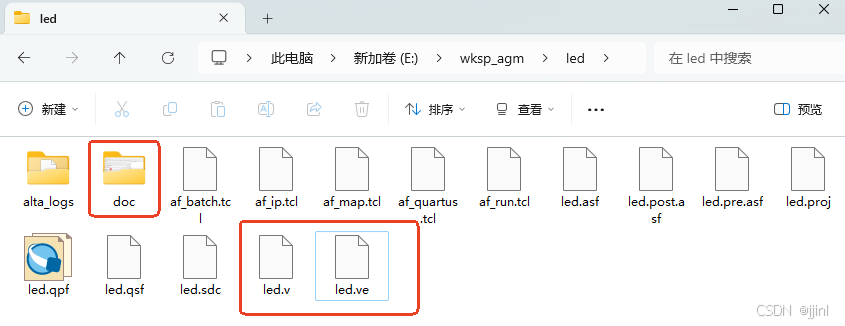

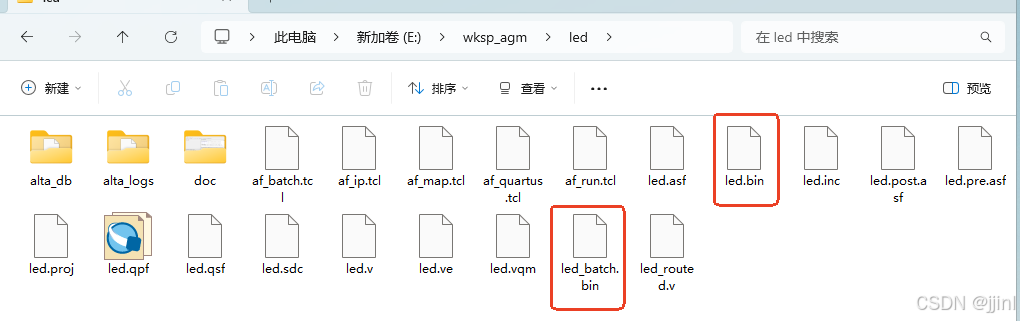

点击Next会生成多个文件,如下图,图中框选是原来的文件,未框选的是新生成

软件配置界面如下,选择verilog文件,点击Next

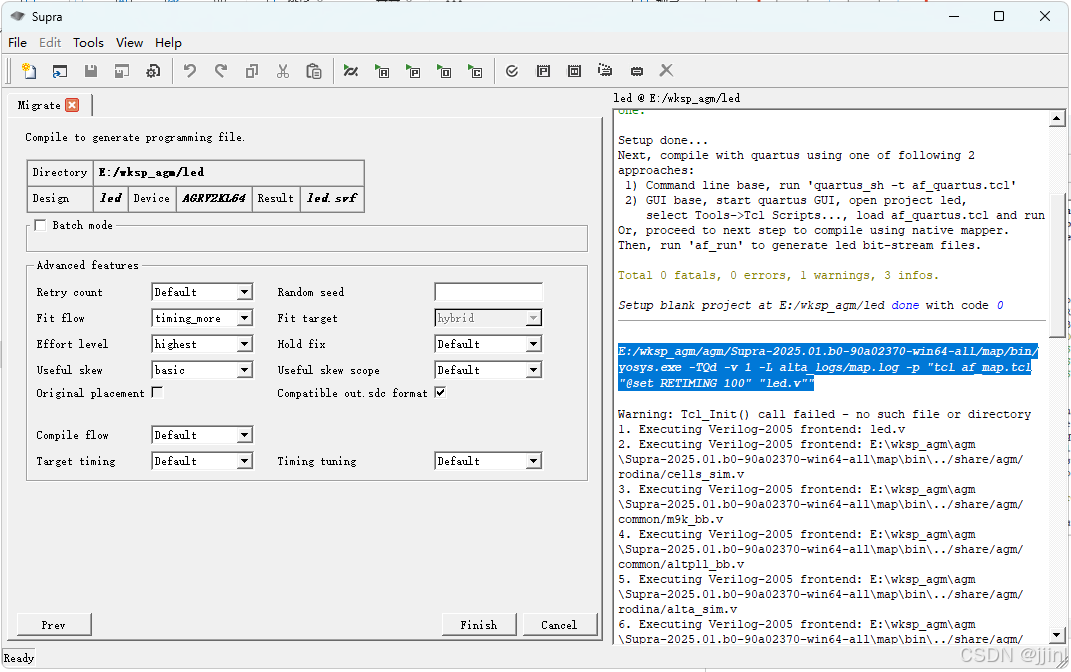

在新的界面中选择finish

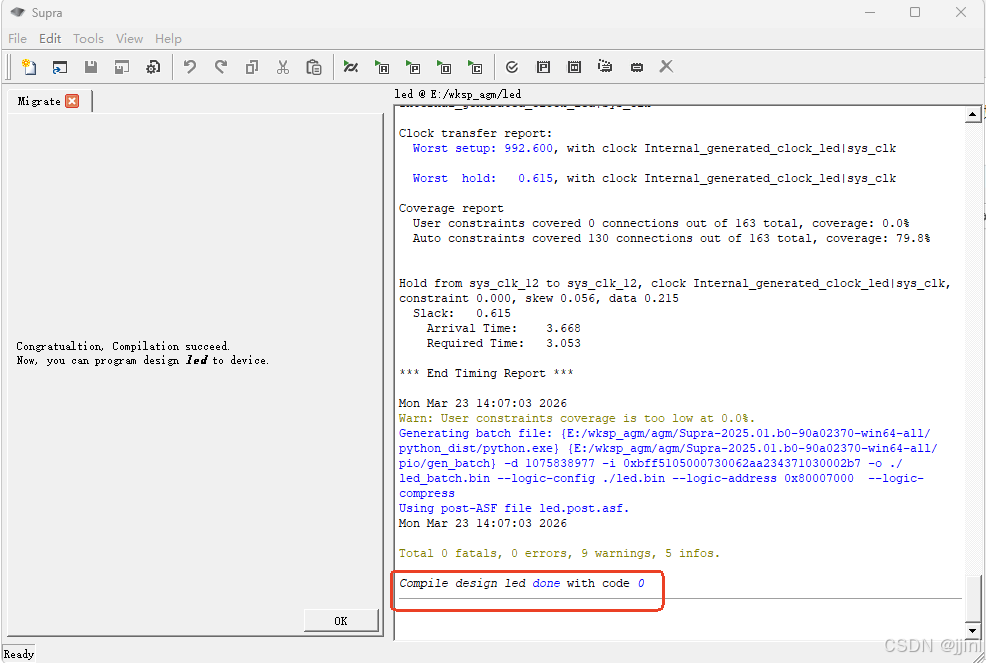

如果最终看到 Compile design led done with code 0 则认为综合成功

最终生成烧写文件led.bin 和led_batch.bin

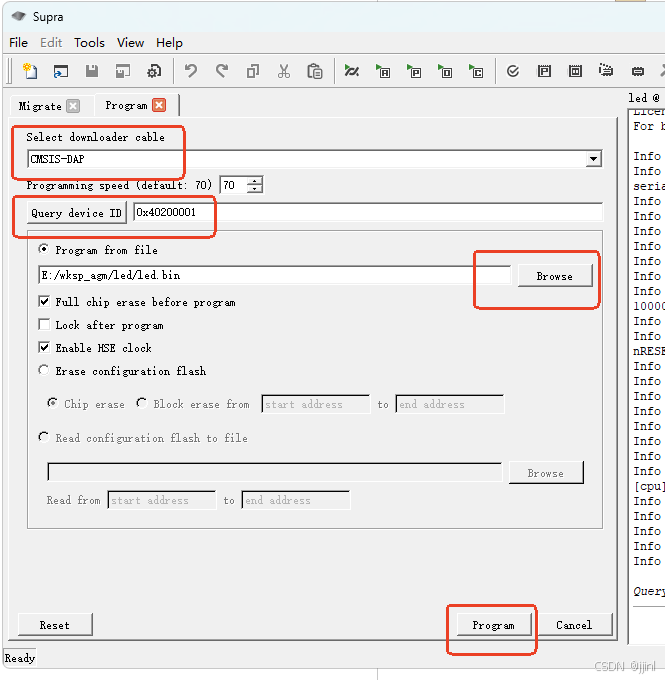

烧写过程,点击菜单Tools --> Program

烧写界面如下,选择不同的下载器,下载文件后缀不一样,这里综合出来的只有bin文件,选usbblaster下载器无法下载bin文件,对开发板上电,并连好下载器,点击Query device ID,直到后面出现设备ID为止,标明下载器连接正常,选择下载文件,点击Program即可实现cpld代码下载。