一、背景概述

AD9144 是 ADI 经典四通道16位、2.8GSPS高速DAC芯片,支持灵活的JESD204B接口配置,广泛应用于无线通信、精密仪器仪表、雷达信号生成、电子对抗等工业与军工场景。

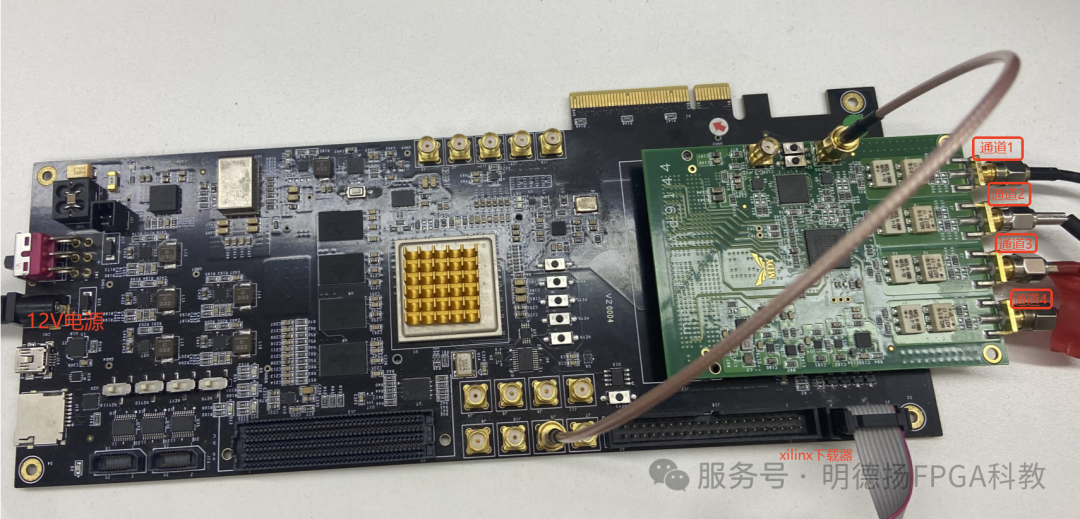

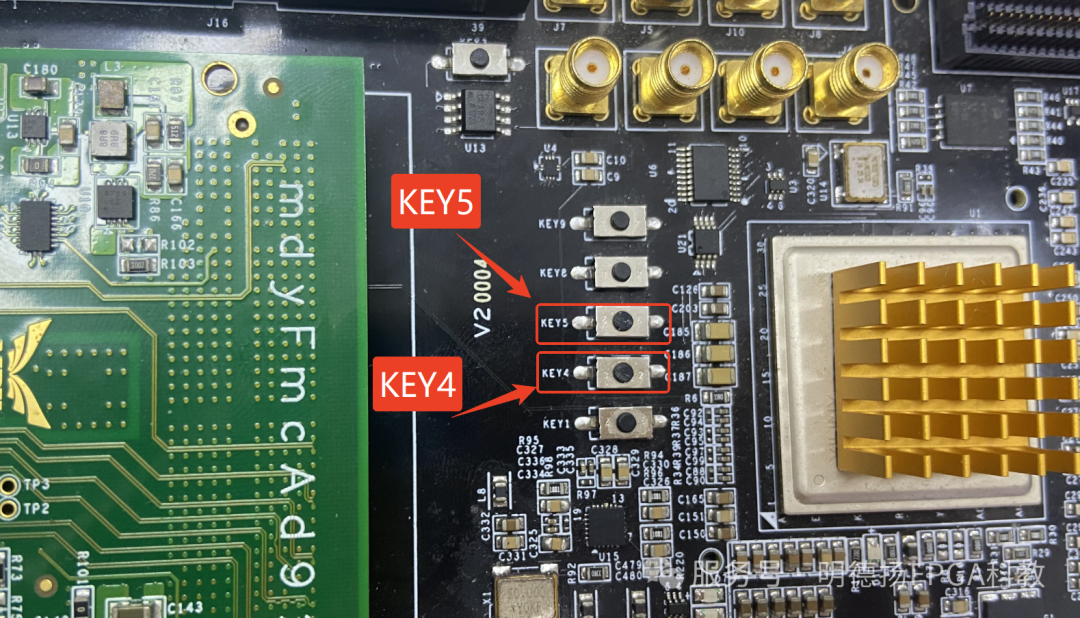

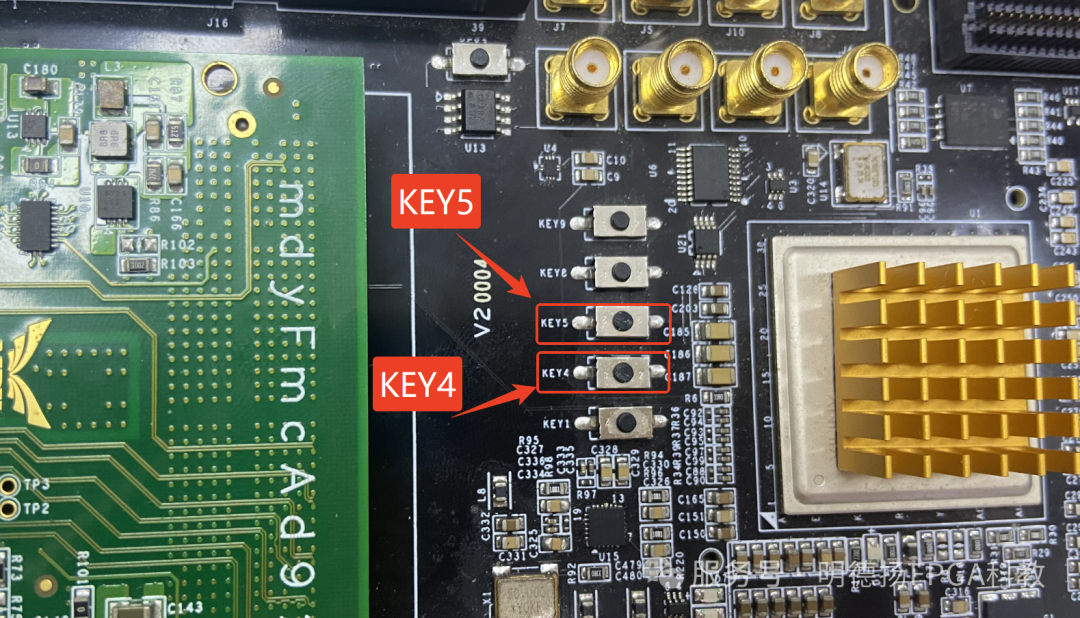

本次我们基于Xilinx K7-325 自研FPGA开发板MP5620Xilinx Kintex-7高速信号处理学习板 + 自研AD9144功能模块AD9144-FMC-EBZ ADI数据转接板四通道数模转换器评估板子模块转换,完成多工况、多模式完整上板验证。验证板如图一所示:

图一:K7-325开发板+AD9144模块

二、实测目标

本次多种模式实测核心目标如下:

-

验证硬件兼容性:实测确认自研AD9144模块可稳定适配主流FPGA平台,实现端到端完整高速数据链路传输;

-

验证多场景适配能力:搭配多种JESD204B差异化配置,覆盖高低不同采样率、多/少通道、不同Lane资源组合的各类工程需求;

-

验证信号输出性能:在多组工作参数下,持续测试波形纯净度、输出稳定性与频率调节能力,充分验证模块电源完整性、时序设计与高速信号质量;

-

降低客户开发门槛:全部例程均经过上板实测落地,提供成熟工程参考与配置方案,帮助客户快速移植、缩短调试周期、加快项目落地。

三、上板效果

我们以K7-325为核心主控平台,依托标准JESD204B协议架构,搭配专属时钟链路与时序优化设计,全覆盖 "8种主流工作模式" 逐一完成上电调试、链路同步、波形采集实测。全面校验不同通道数量、Lane链路配置、采样率及插值倍率组合下的系统稳定性、协议兼容性与动态输出性能,为不同行业项目选型、方案快速移植提供可直接复用的工程参考。

下面为大家逐一展示8种工作模式的配置详情、验证要点及适用场景效果演示:

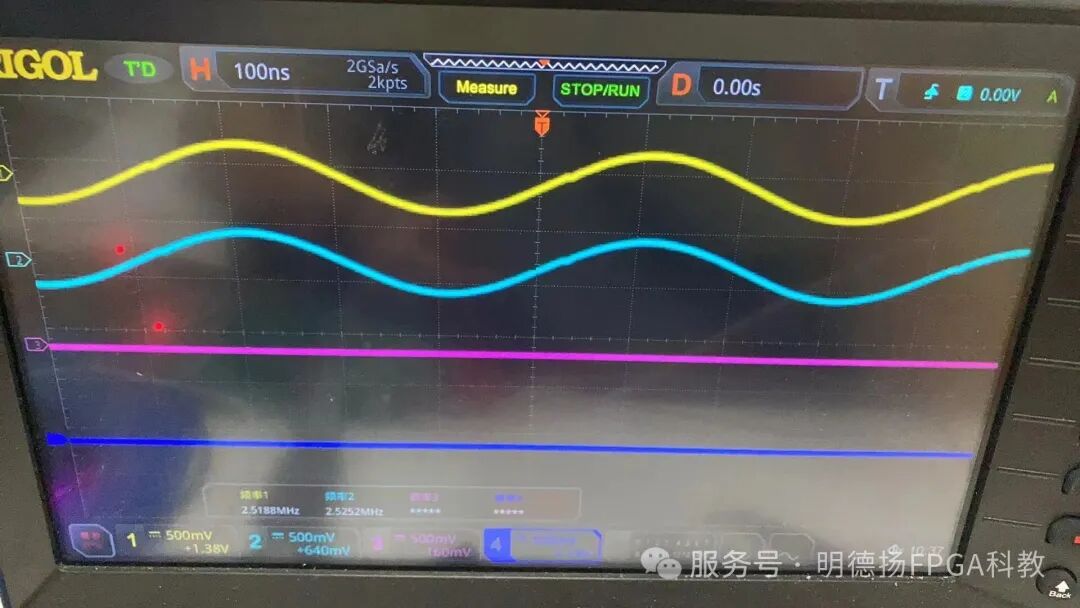

3.1模式二:

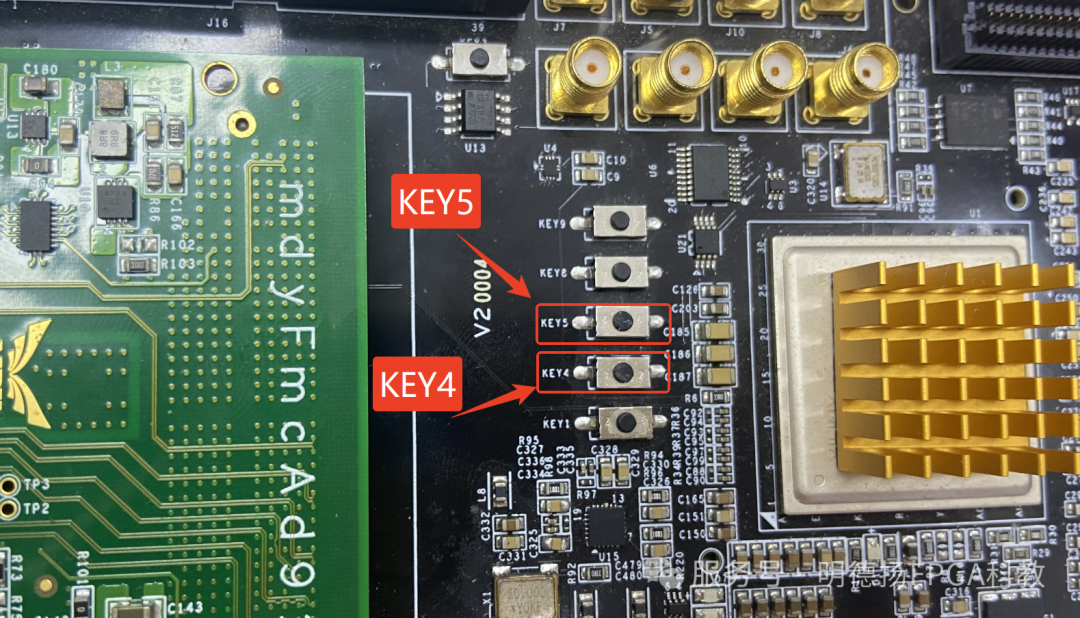

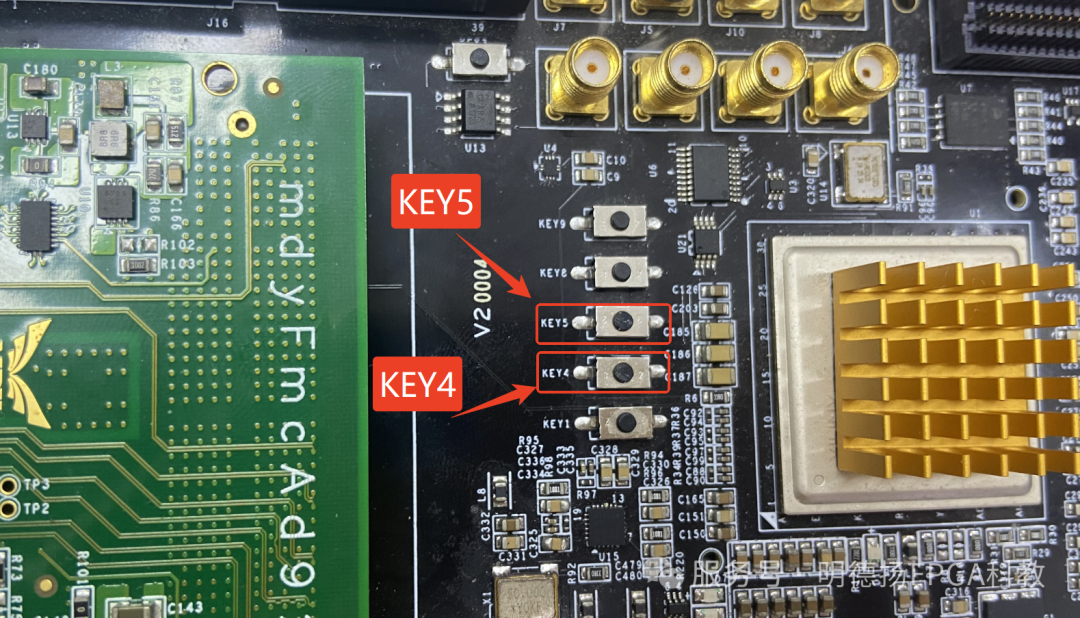

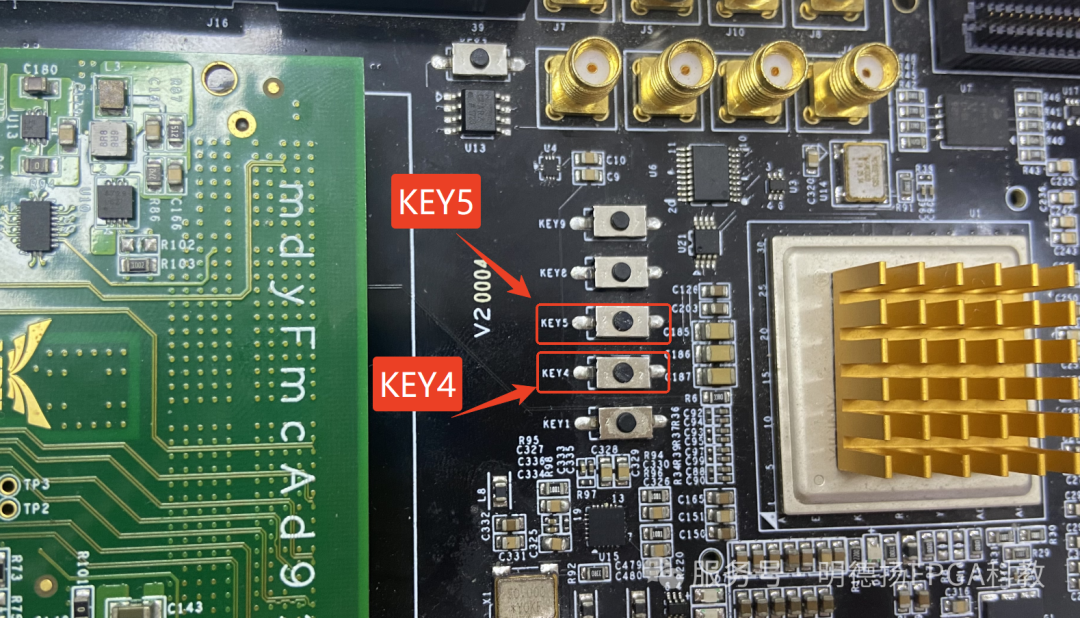

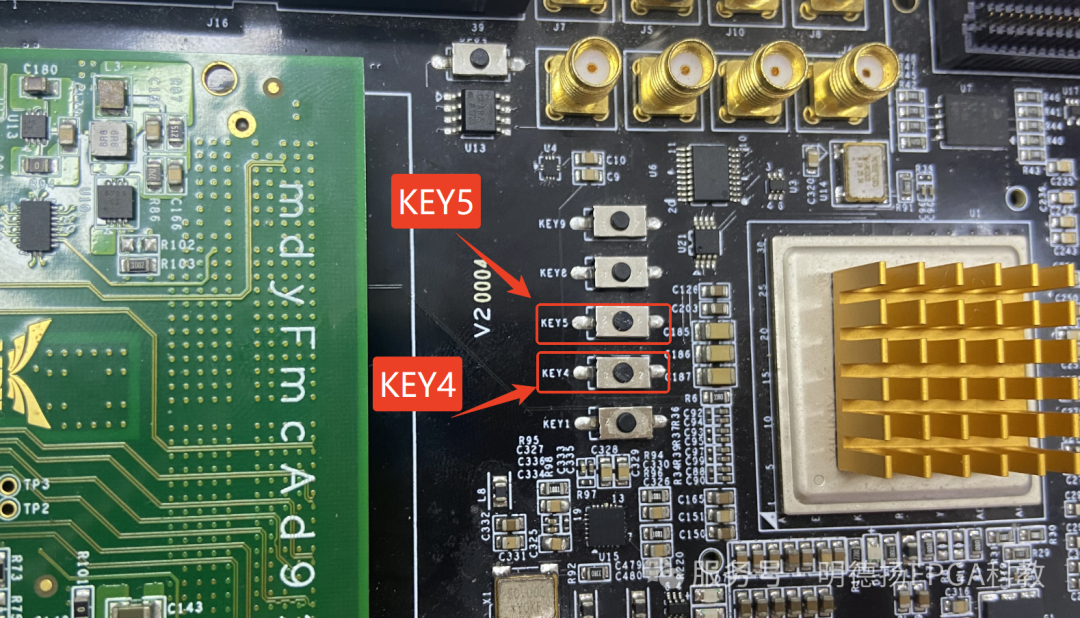

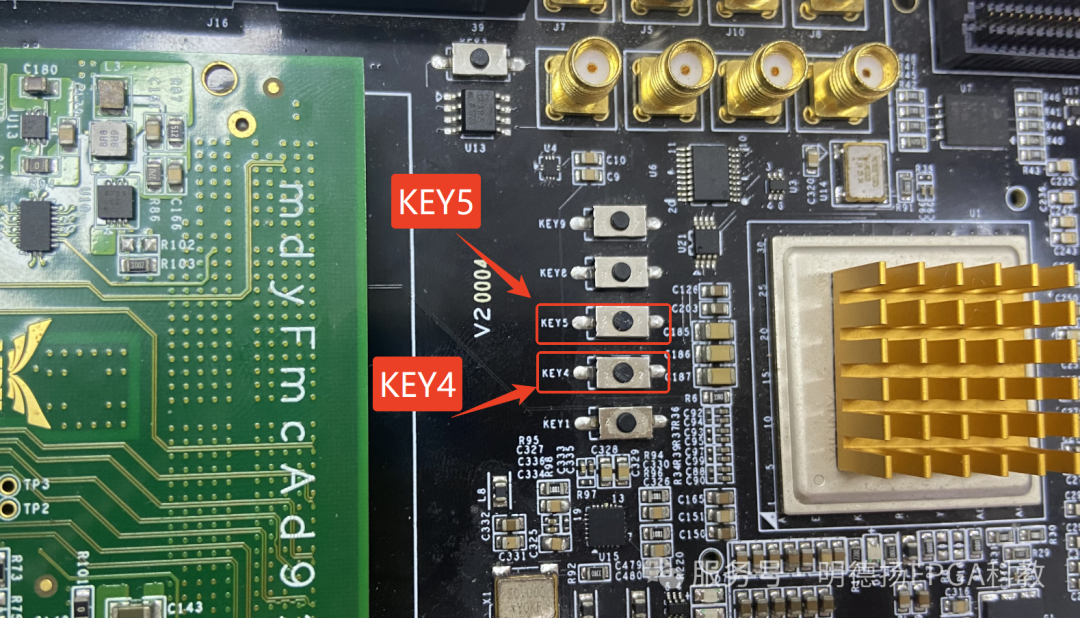

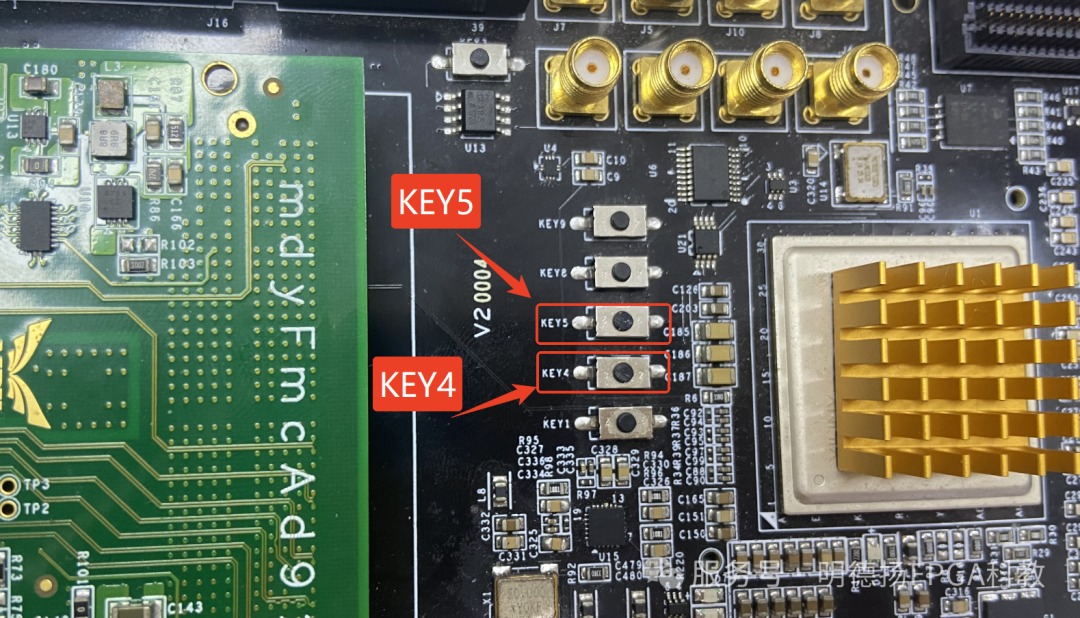

测试现象:下载完成之后,按下MP5620的KEY4键进行AD9516和AD9144的配置,配置完成之后示波器会有波形显示。按KEY5键,频率每次会在之前的基础上×2。

3.1.1参数配置

AD9144模式2 参数配置:MODE=2。

M:4

L:4

S:1

F:2

AD9144采样率Fs为160M, 16bit

总lane线速率=(Fs/S)*F*L*8 =(160/1)*2*4*8=10240Mbps

每个lane线速率=10240/4=2560Mbps=2.56Gbps

8b10b编码之后线速率=2.56*1.25=3.2Gbps

设K=32,R=4

LMFC=(Fs/S/K)=160M/1/32= 5.0M

Sysref = LMFC/R=5.0M/4 = 1.25M

JESD204 TX_DATA时钟=160M/2= 80M

3.1.2实验效果

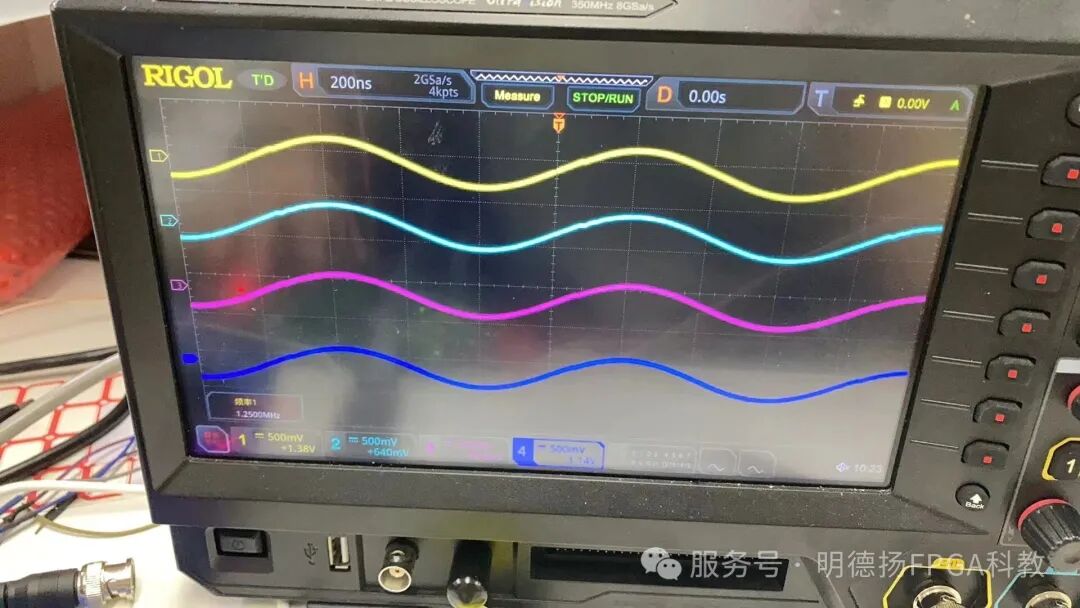

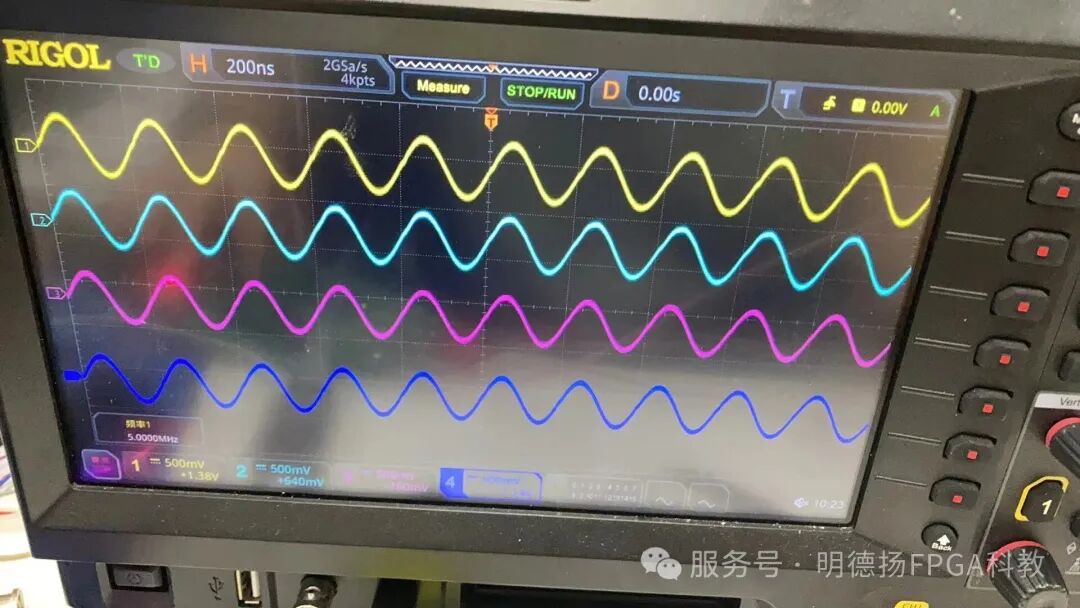

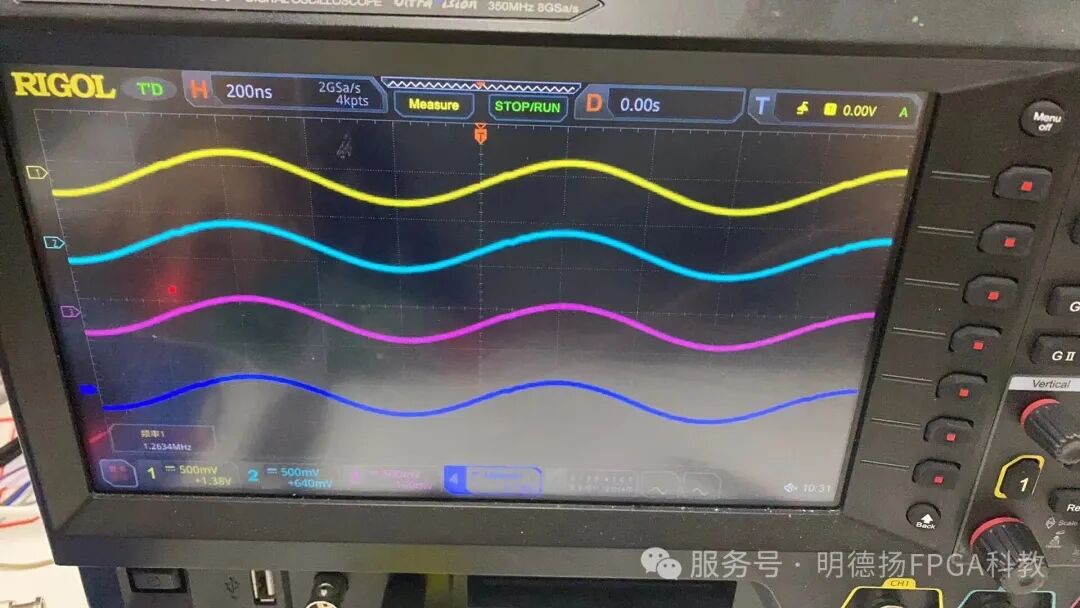

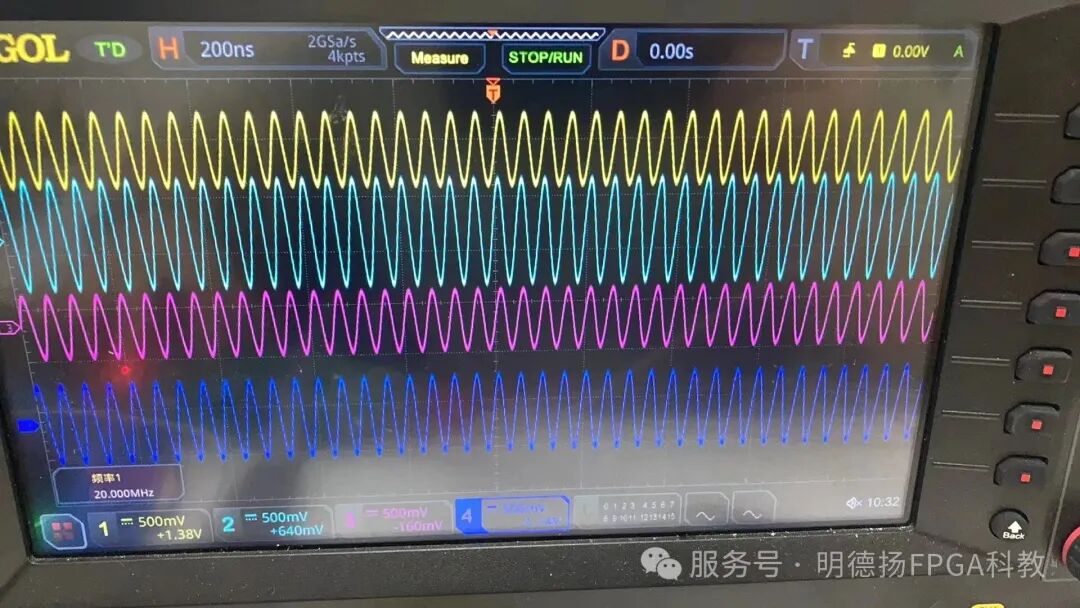

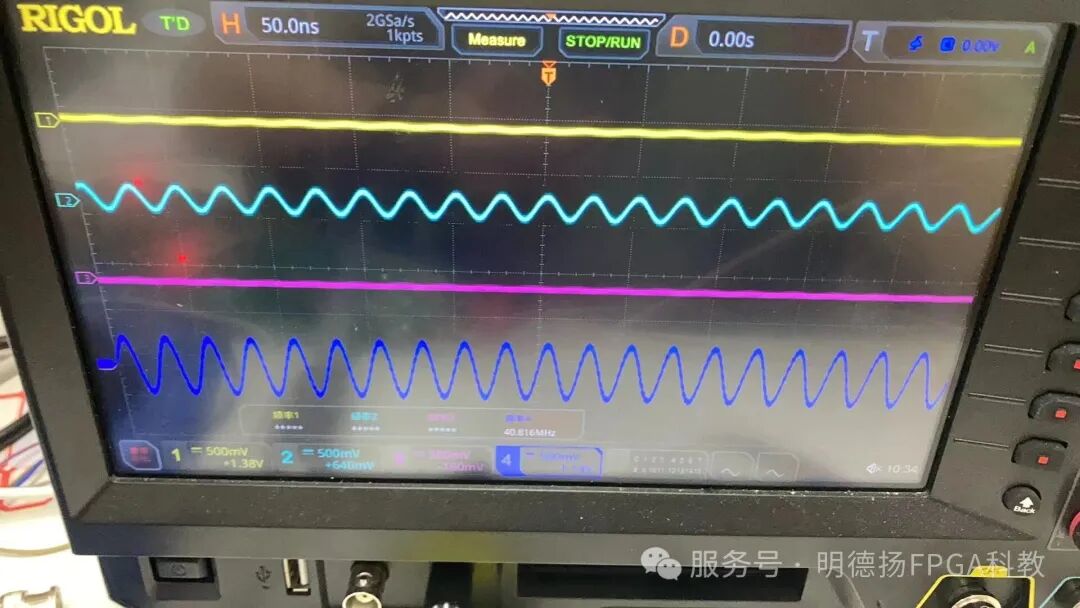

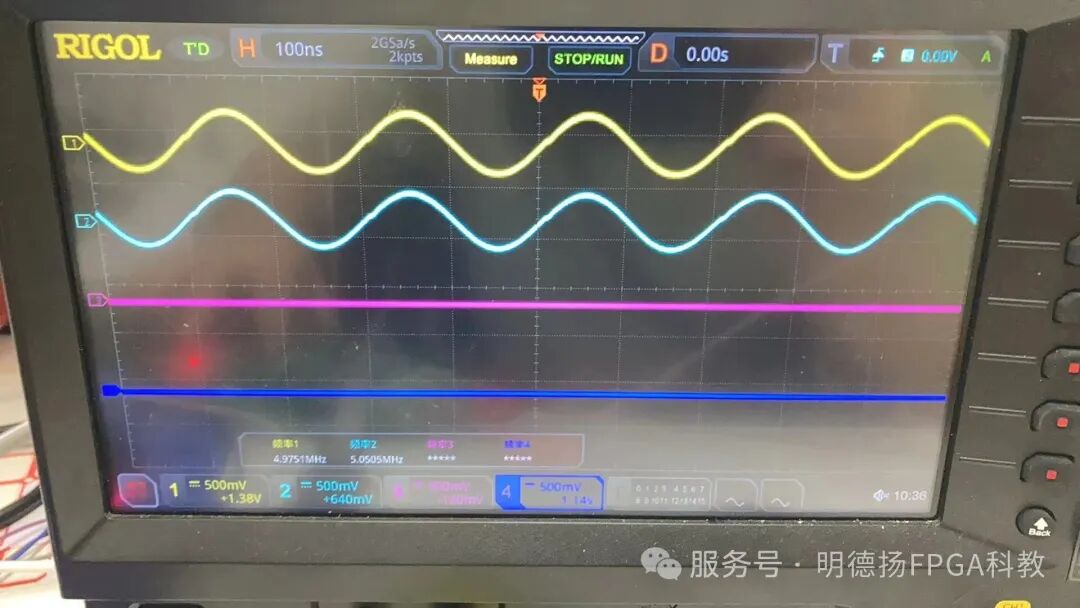

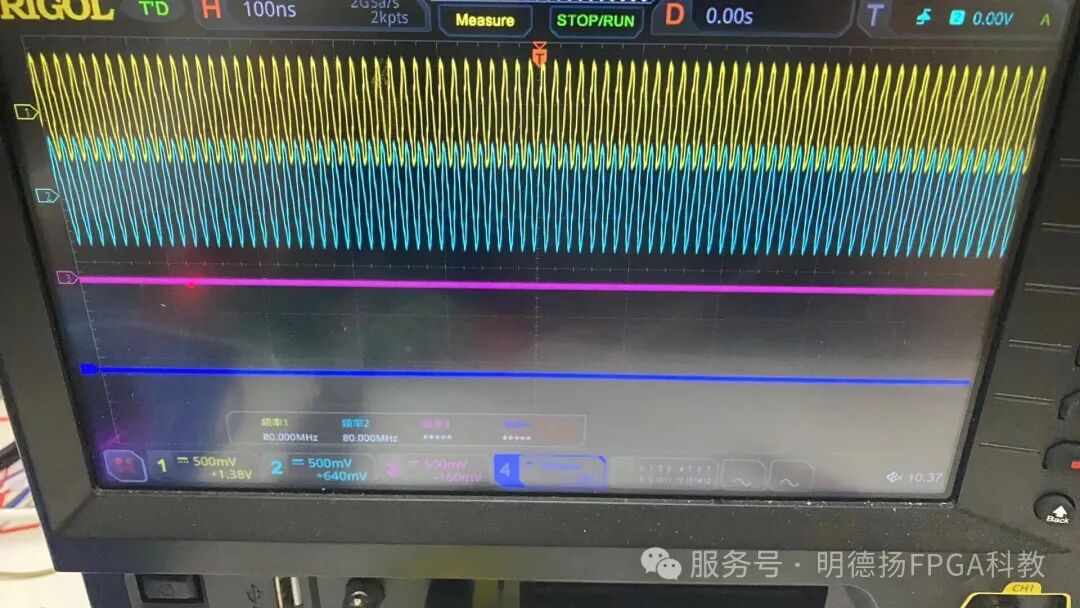

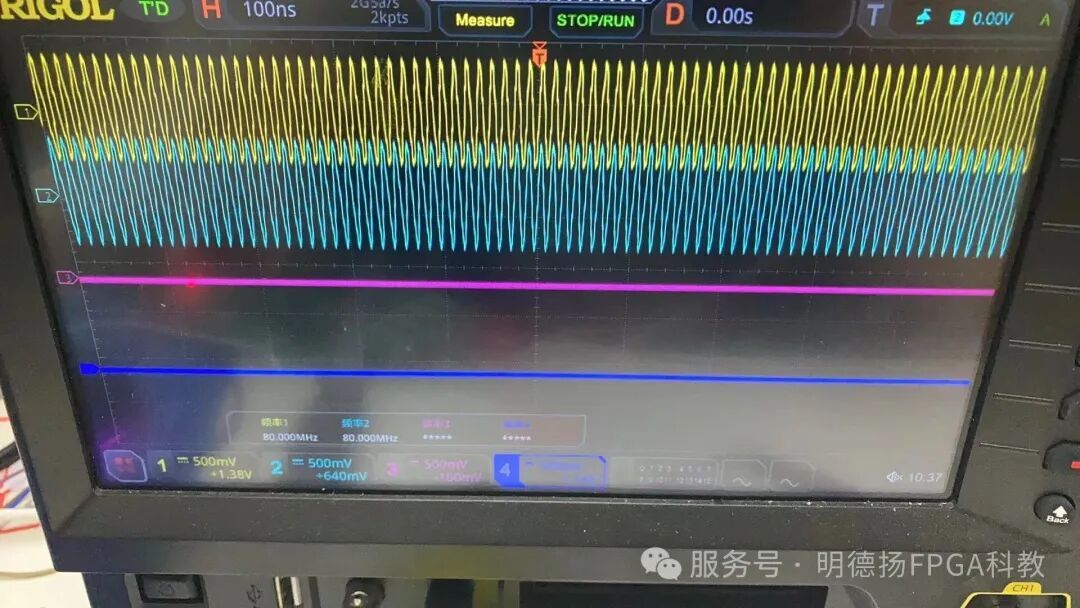

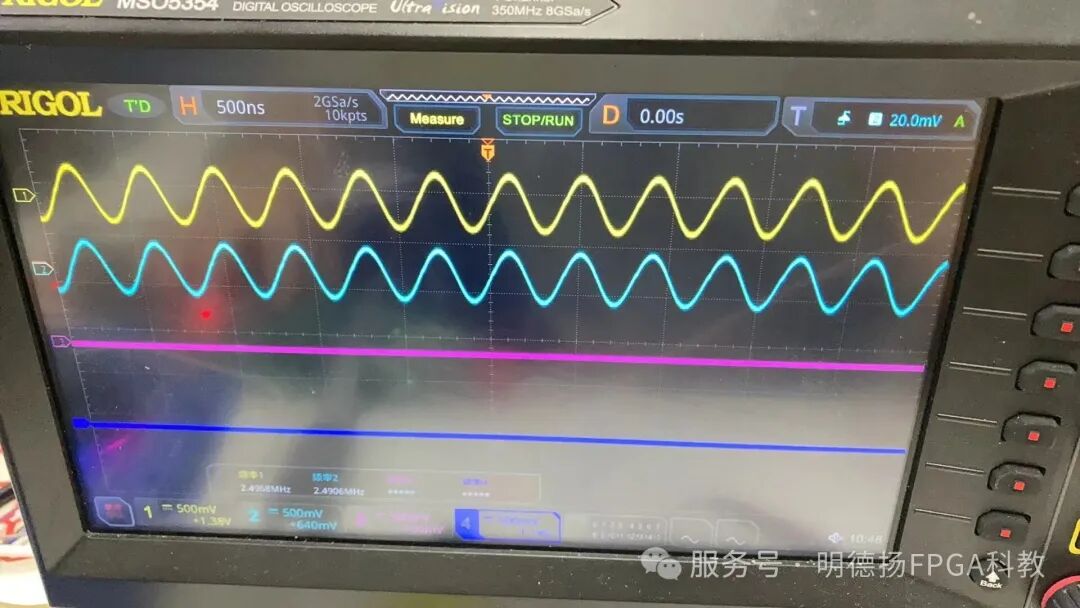

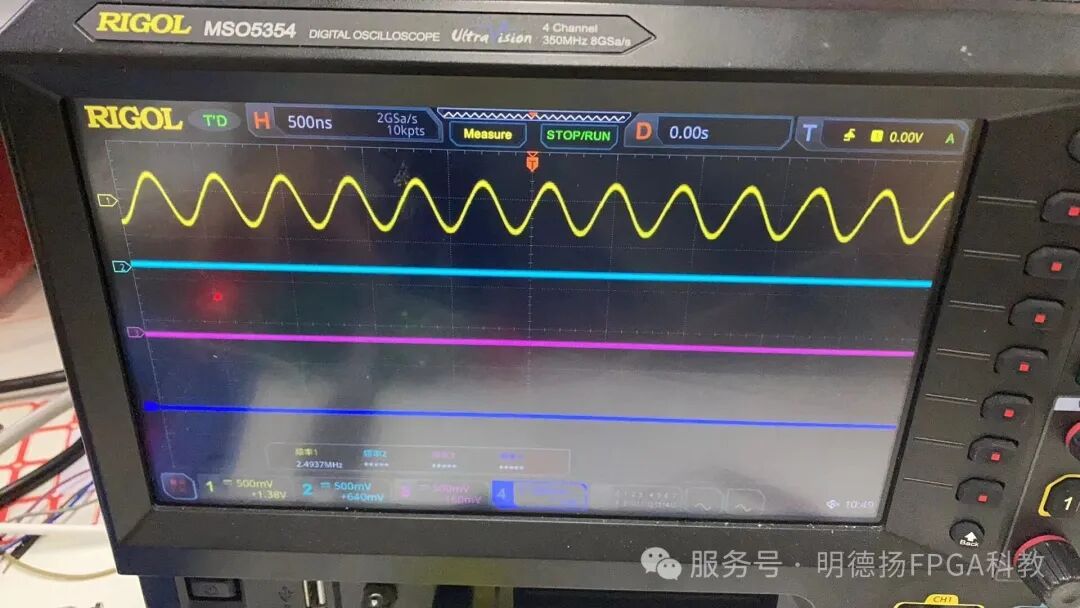

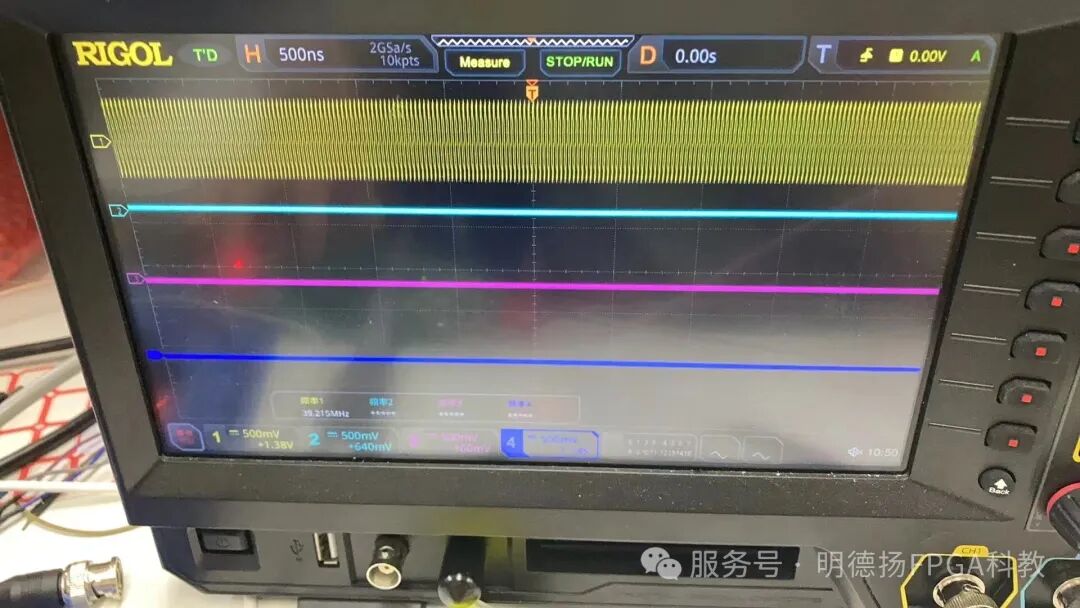

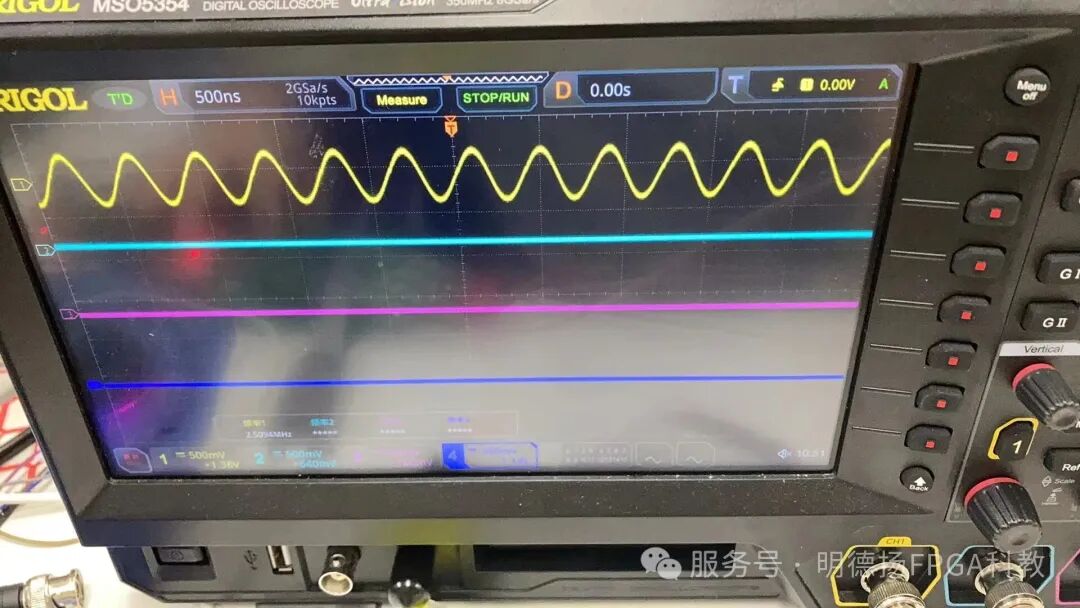

按下KEY4 配置AD9144和AD9516

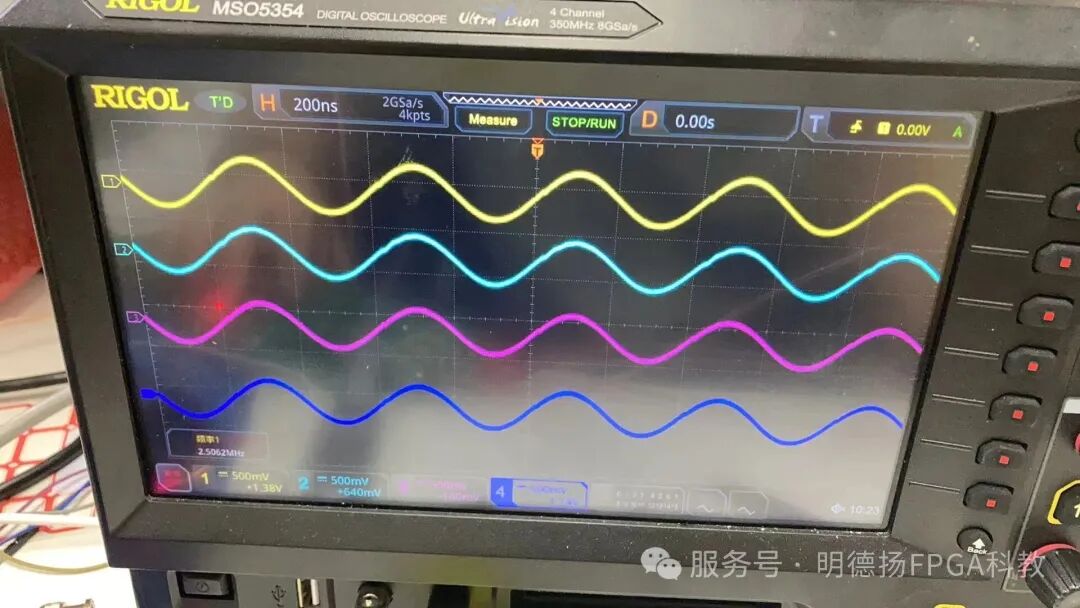

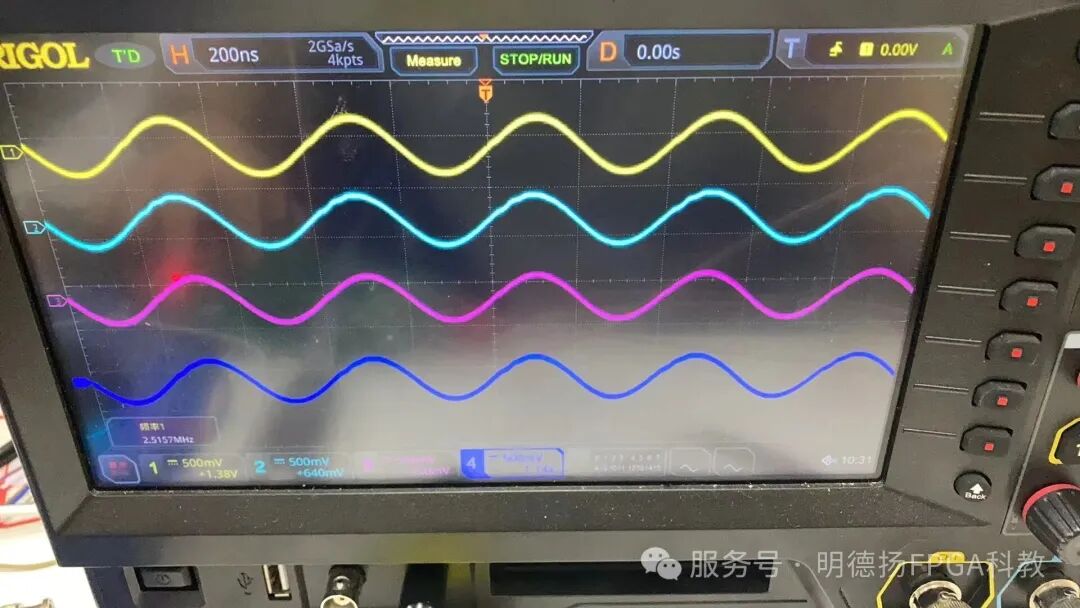

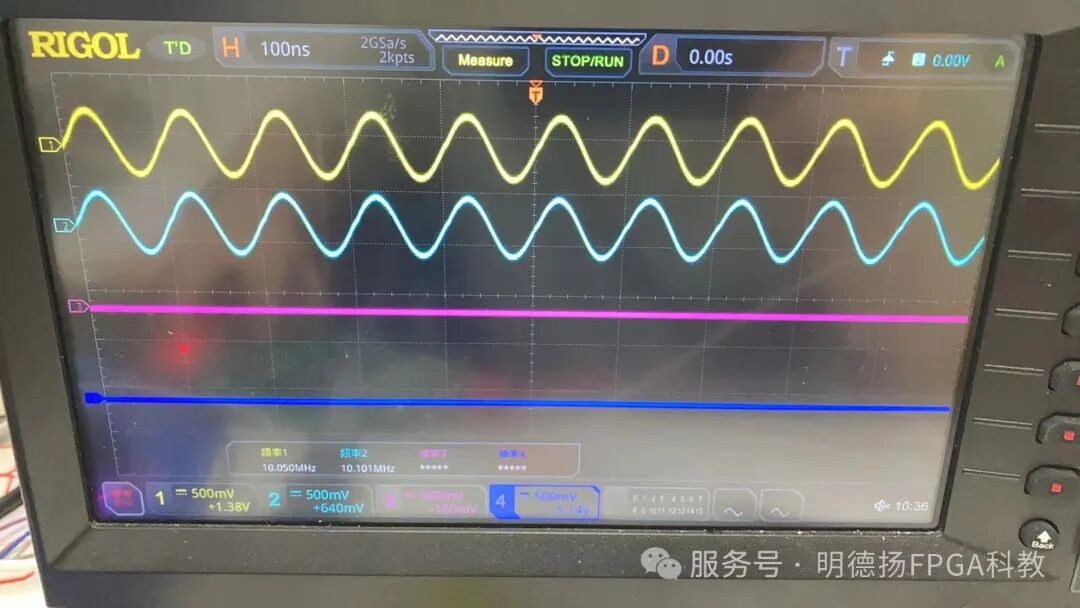

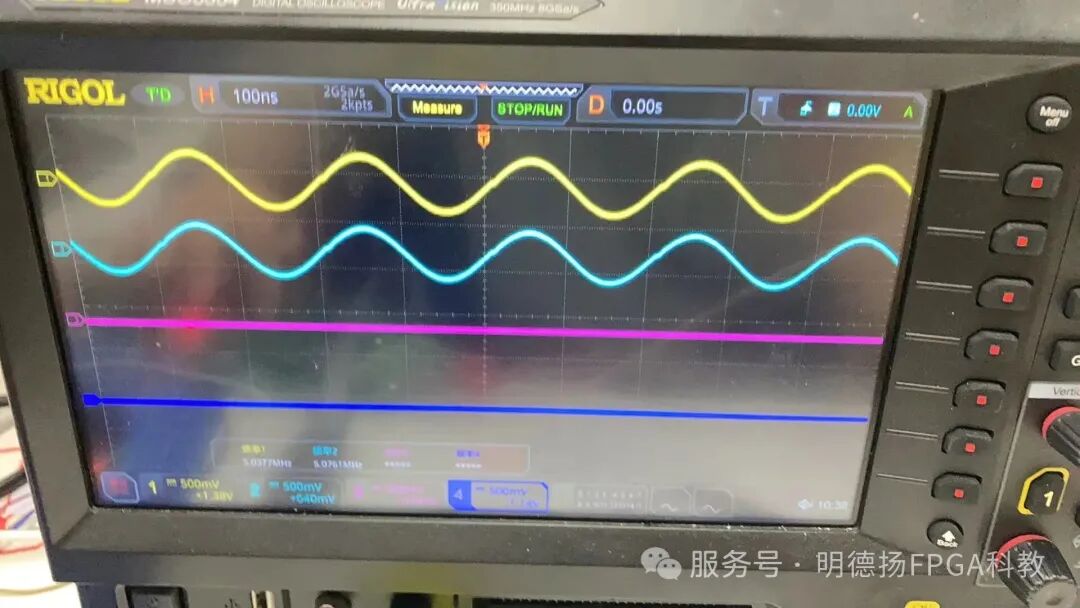

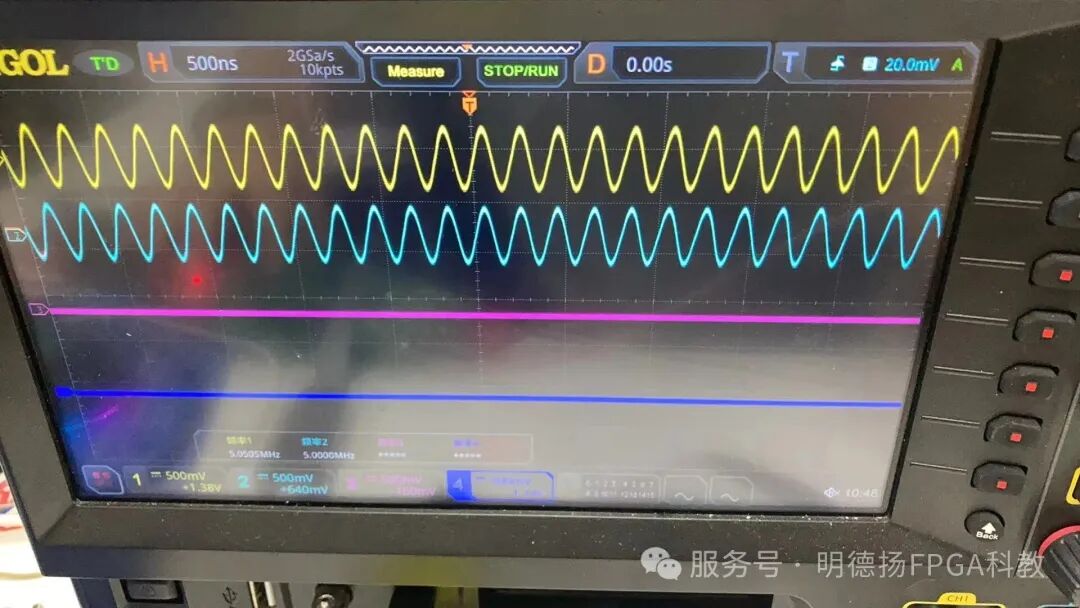

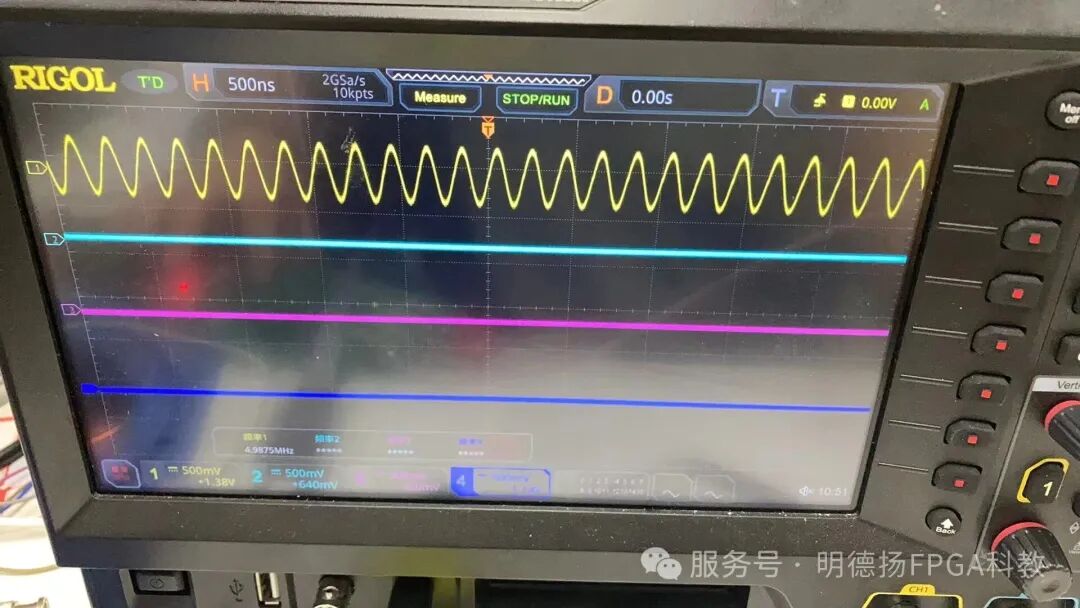

再按KEY5改变频率

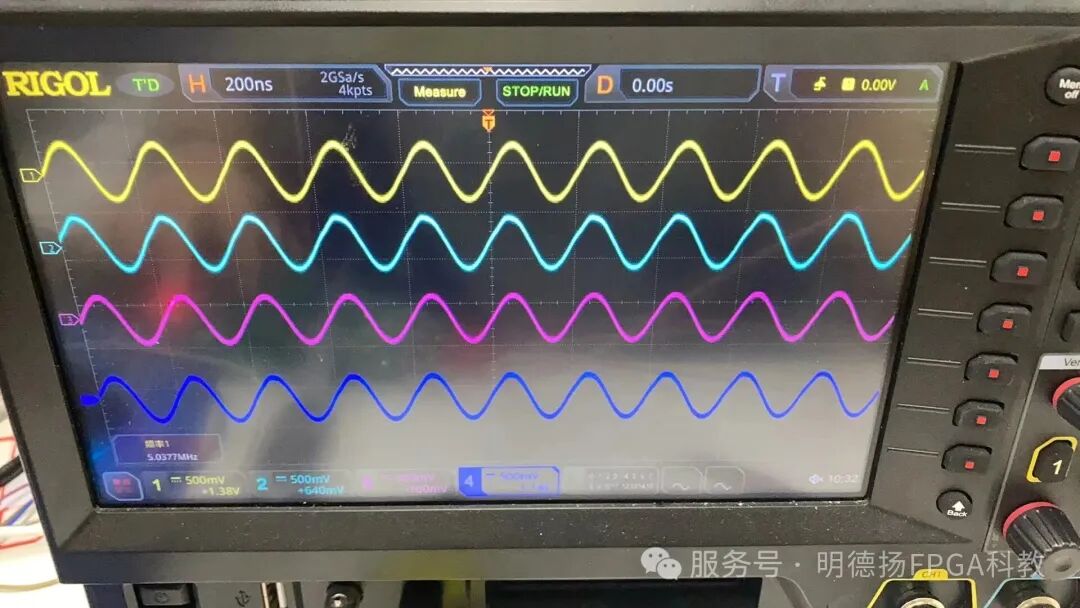

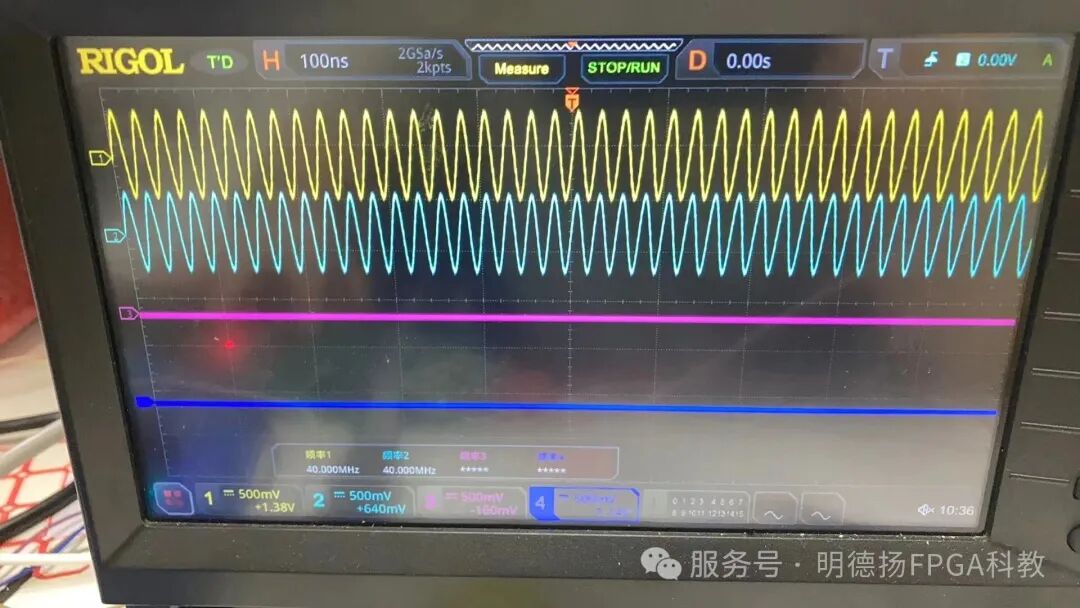

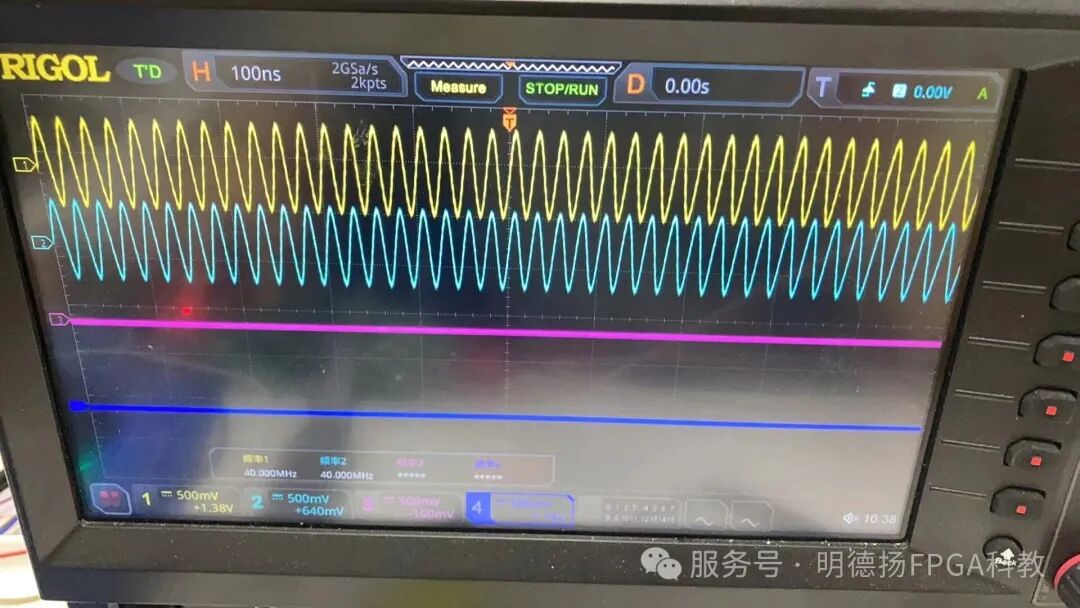

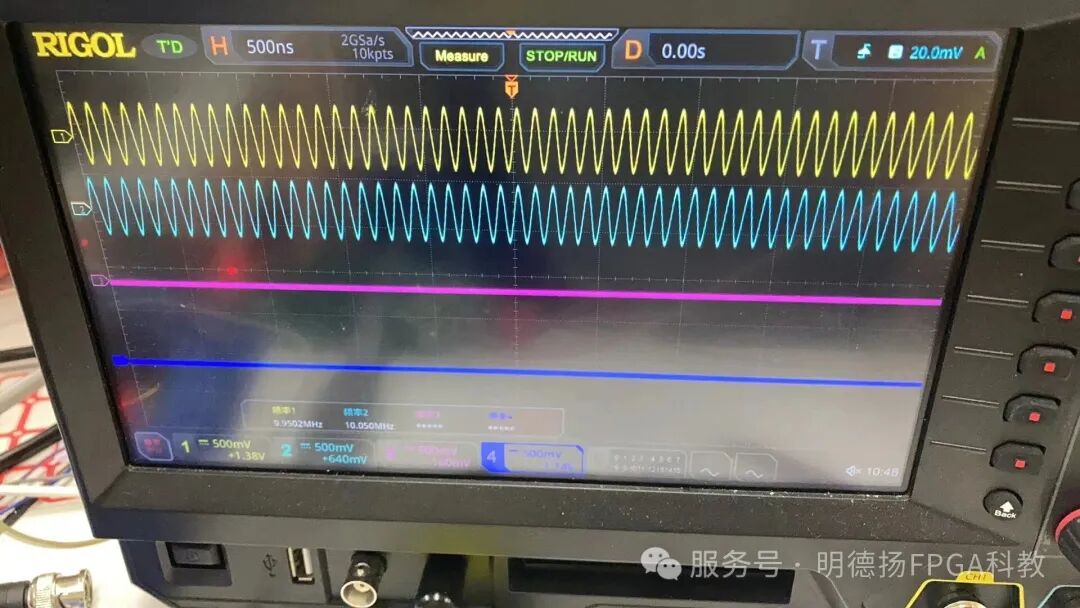

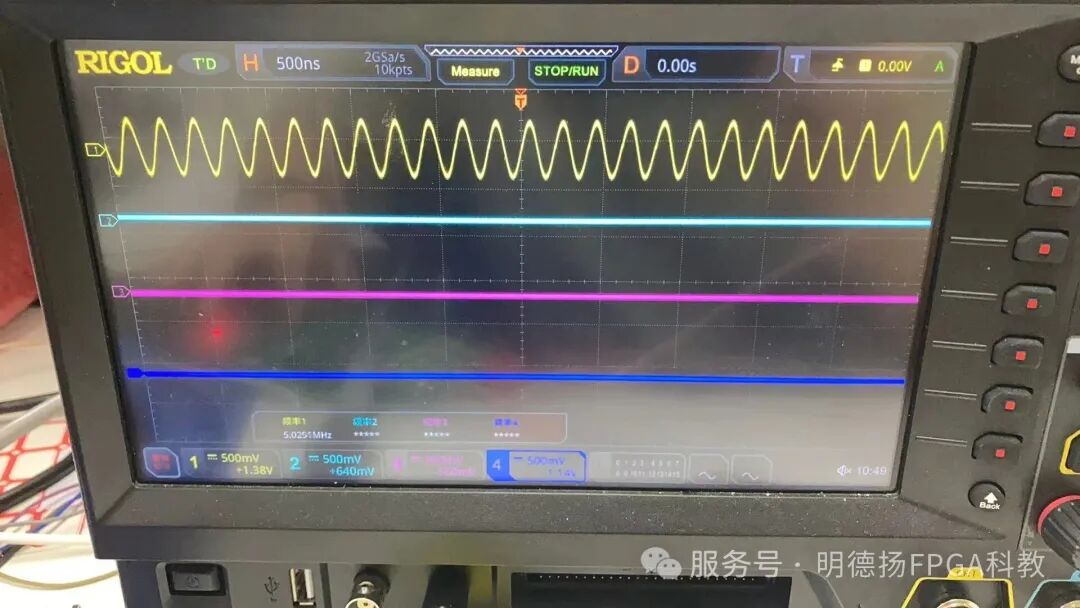

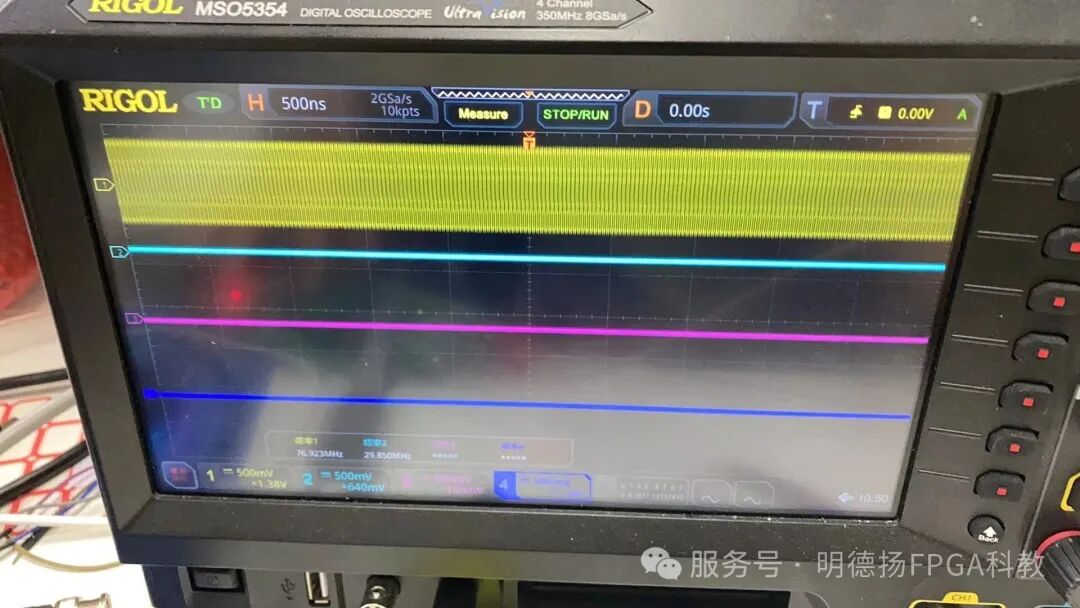

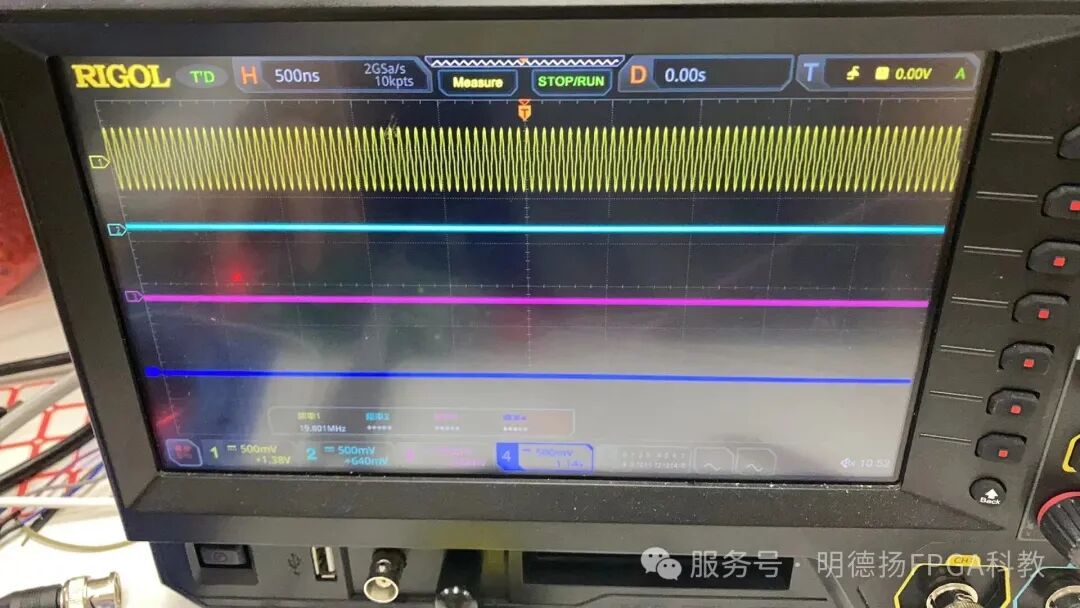

再按KEY5改变频率

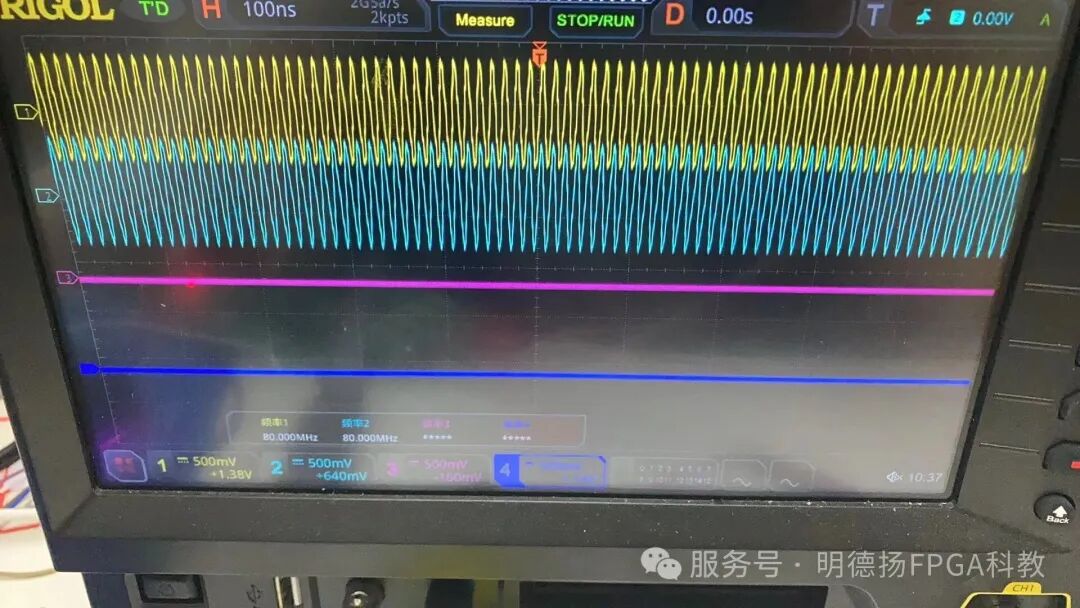

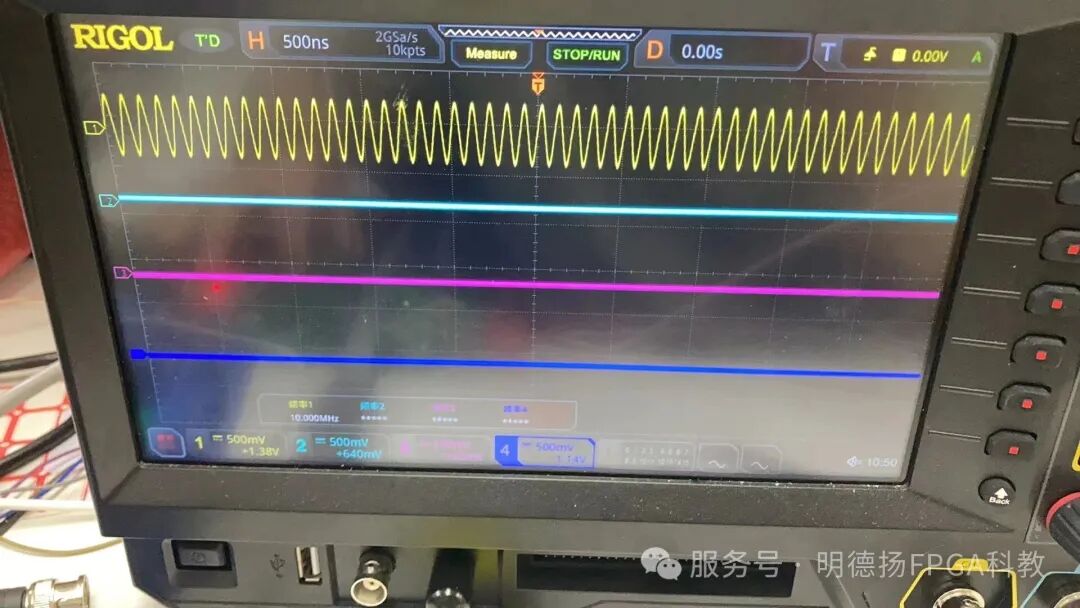

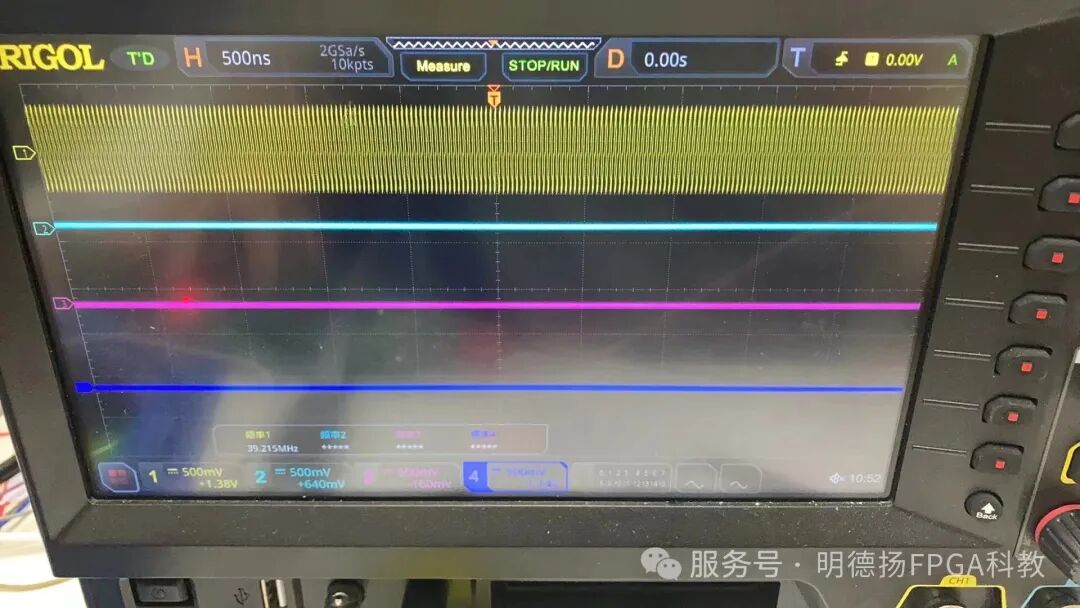

再按KEY5改变频率

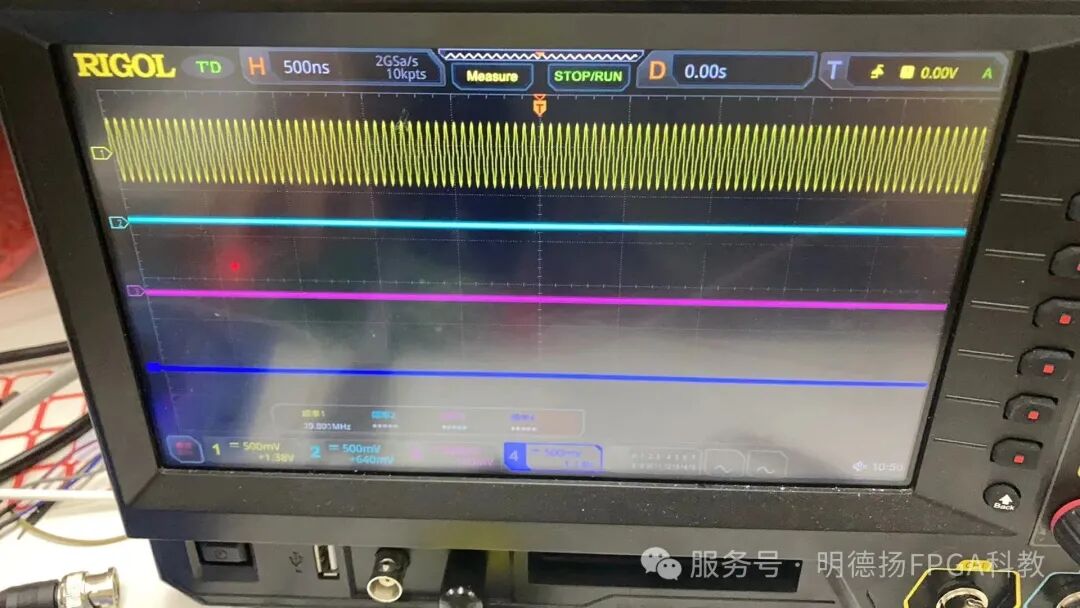

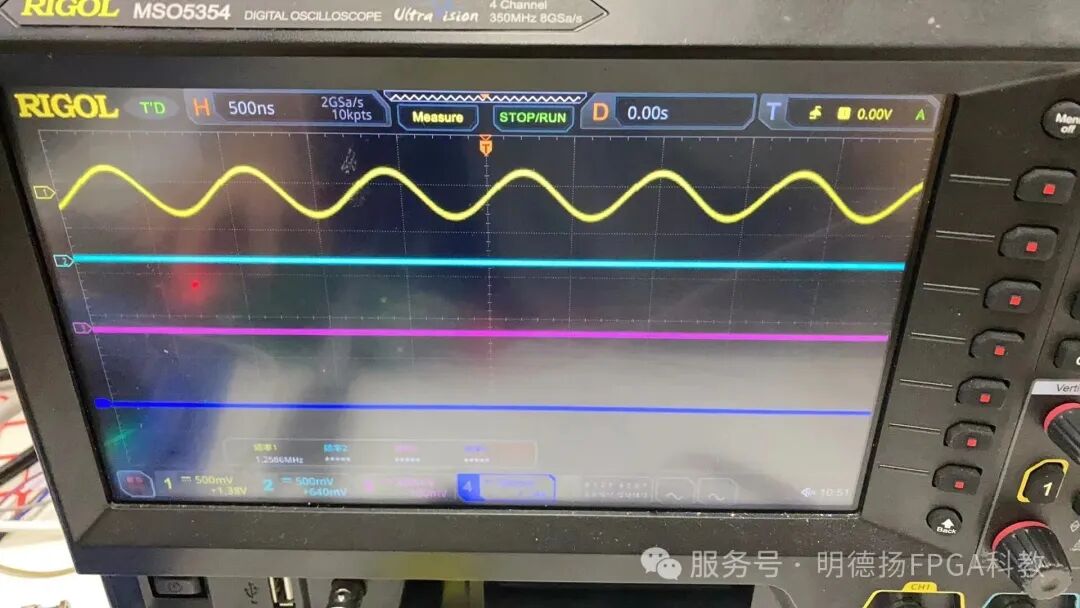

再按KEY5改变频率

再按KEY5改变频率

3.2模式三:

测试现象:下载完成之后,按下MP5620的KEY4键进行AD9516和AD9144的配置,配置完成之后示波器会有波形显示。按KEY5键,频率每次会在之前的基础上×2。

3.2.1参数配置

AD9144模式3 参数配置:MODE=3。

M:4

L:2

S:1

F:4

AD9144采样率Fs为80M, 16bit

总lane线速率=(Fs/S)*F*L*8 =(80/1)*4*2*8=5120Mbps

每个lane线速率=5120/2=2560Mbps=2.56Gbps

8b10b编码之后线速率=2.56*1.25=3.2Gbps

设K=16,R=4

LMFC=(Fs/S/K)=80M/1/16= 5M

Sysref = LMFC/R=5M/4 = 1.25M

JESD204 TX_DATA时钟=80M/1= 80M

计算参考 AD9144 MODE 3的lane数据重组章节

AD9514各通道输出的关系:

AD9154 OUT1:device clock

AD9154 OUT6: AD9144 SYSREF CLK

AD9154 OUT7: FPGA SYSREF CLK

AD9154 OUT9: FPGA gtx 输入时钟

AD9144 Ref clk:3.2G/40=80M

3.2.2实验效果

按下KEY4 配置AD9144和AD9516

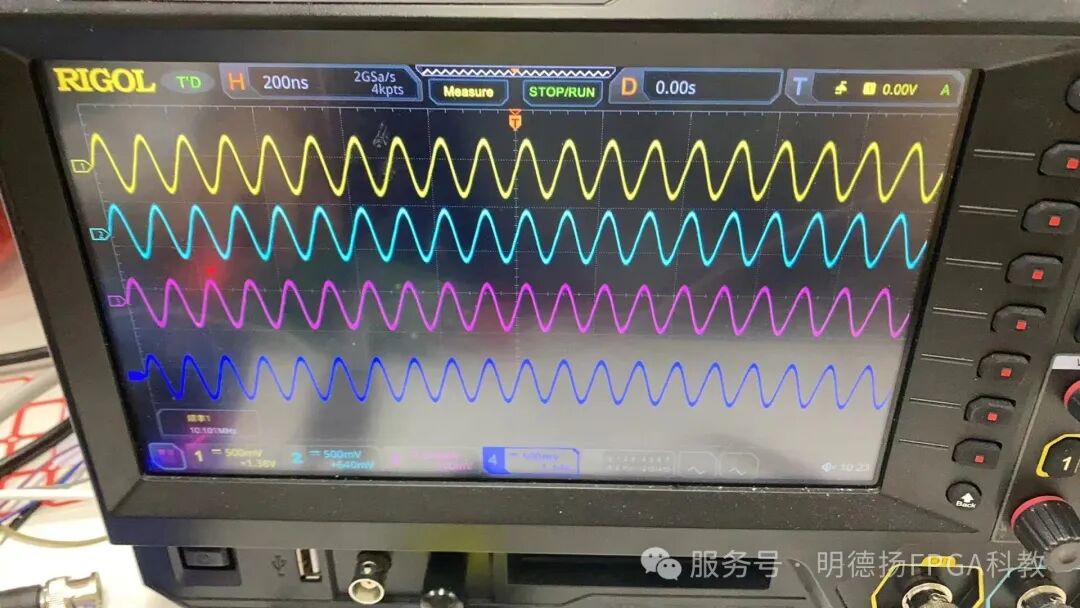

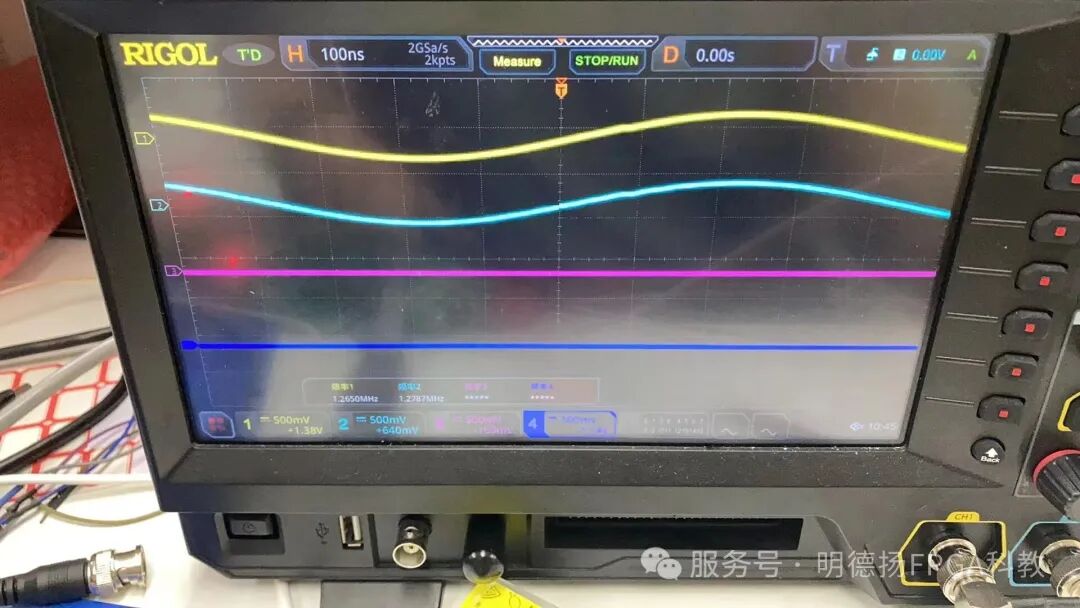

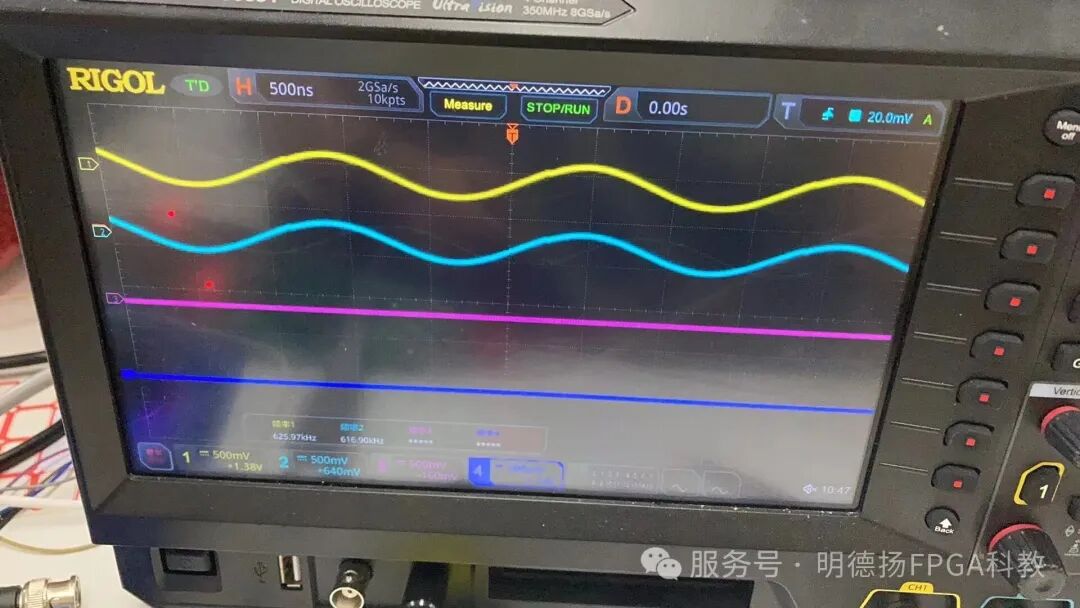

再按KEY5改变频率

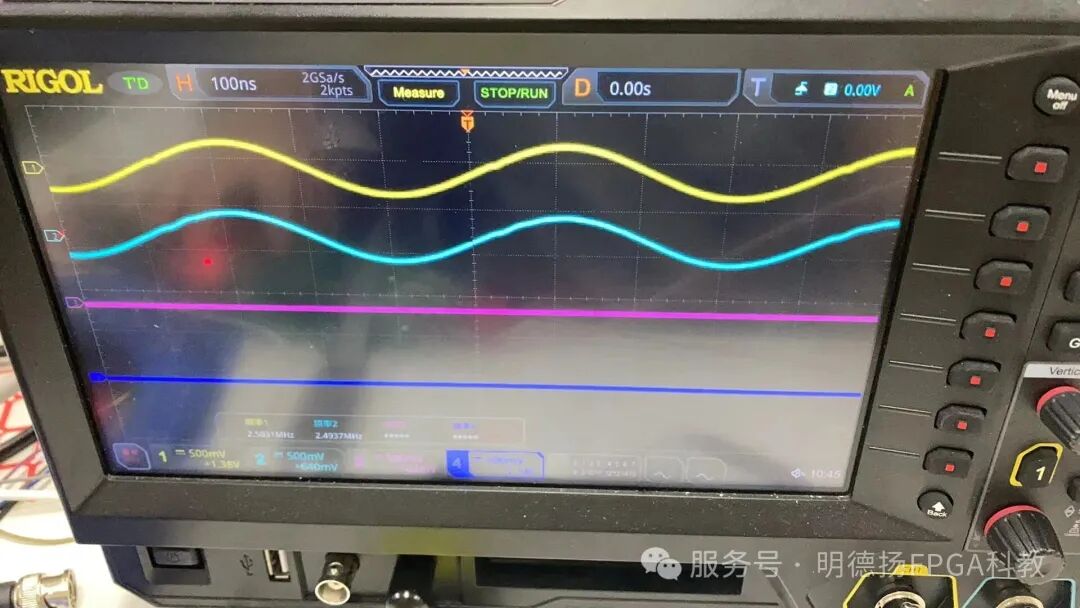

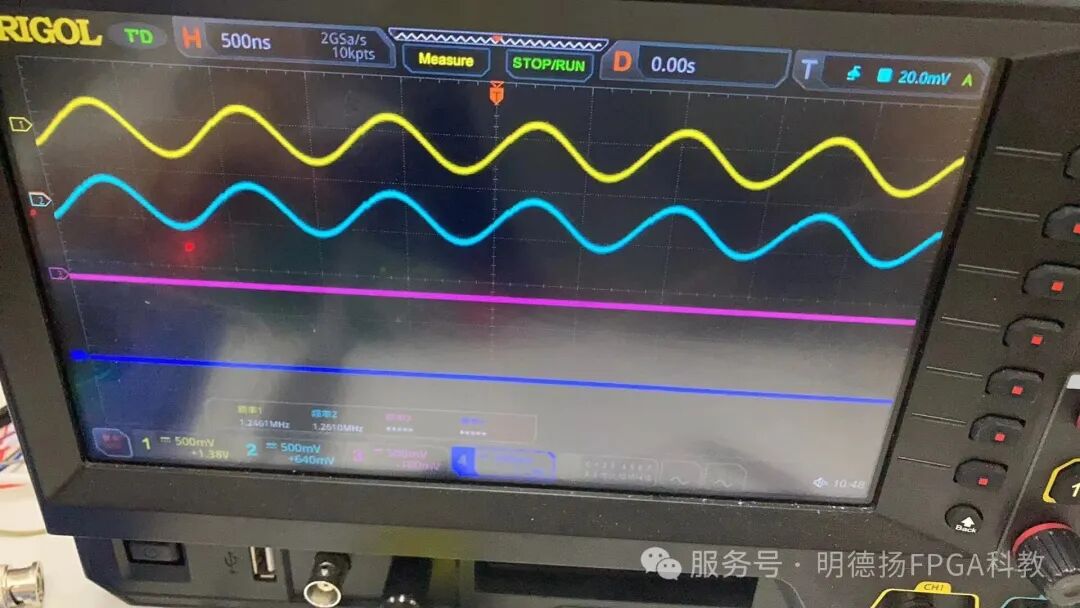

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

3.3模式四:

测试现象:下载完成之后,按下MP5620的KEY4键进行AD9516和AD9144的配置,配置完成之后示波器会有波形显示。按KEY5键,频率每次会在之前的基础上×2。

AD9144 640M采样率,内插为2,AD9144各通道的输入采样率为320M。

3.3.1参数配置

AD9144模式4 参数配置:MODE=4。

M:2

L:4

S:1

F:1

AD9144采样率Fs为320M, 16bit

总lane线速率=(Fs/S)*F*L*8 =(320/1)*1*4*8=10240Mbps

每个lane线速率=10240/4=2500Mbps=2.56Gbps

8b10b编码之后线速率=2.56*1.25=3.2Gbps

设K=32,R=4

LMFC=(Fs/S/K)=320M/1/32= 10M

Sysref = LMFC/R=10M/4 = 2.5M

JESD204 TX_DATA时钟=320M/4= 80M

计算参考 AD9144 MODE 4的lane数据重组章节

AD9514各通道输出的关系:

AD9154 OUT1:device clock

AD9154 OUT6: AD9144 SYSREF CLK

AD9154 OUT7: FPGA SYSREF CLK

AD9154 OUT9: FPGA gtx 输入时钟

AD9144 Ref clk:3.2G/20=160M

3.3.2实验效果

按下KEY4 配置AD9144和AD9516

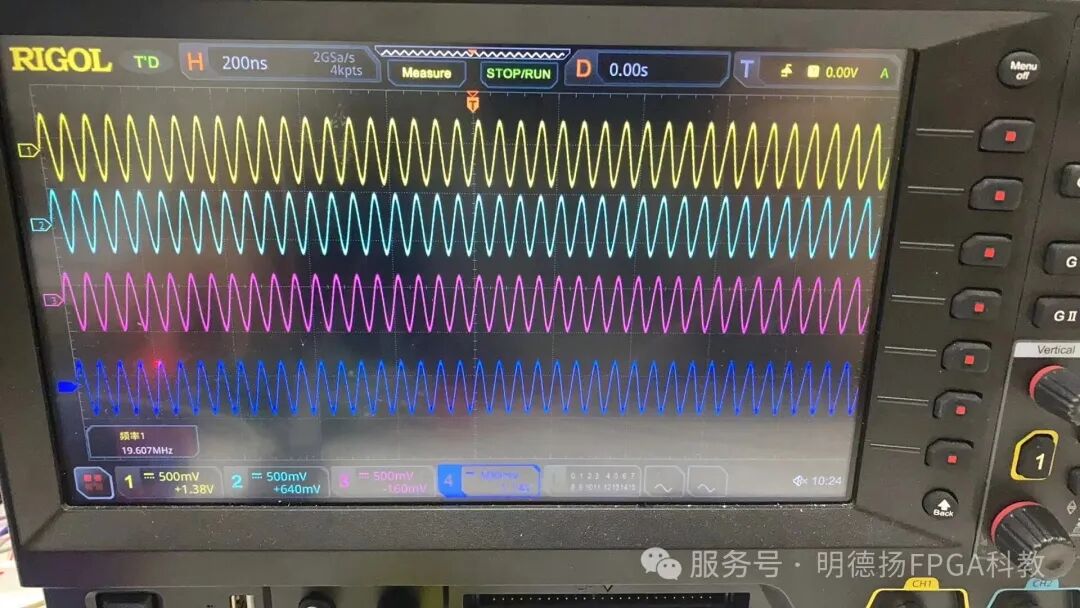

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

3.4模式五:

测试现象:下载完成之后,按下MP5620的KEY4键进行AD9516和AD9144的配置,配置完成之后示波器会有波形显示。按KEY5键,频率每次会在之前的基础上×2。

D9144 640M采样率,内插为2,AD9144各通道的输入采样率为320M。

3.4.1参数配置

AD9144模式5 参数配置:MODE=5。

M:2

L:4

S:2

F:2

AD9144采样率Fs为320M, 16bit

总lane线速率=(Fs/S)*F*L*8 =(320/2)*2*4*8=10240Mbps

每个lane线速率=10240/4=2500Mbps=2.56Gbps

8b10b编码之后线速率=2.56*1.25=3.2Gbps

设K=32,R=4

LMFC=(Fs/S/K)=320M/2/32= 5M

Sysref = LMFC/R=5M/4 = 1.25M

JESD204 TX_DATA时钟=320M/4= 80M

AD9514各通道输出的关系:

AD9154 OUT1:device clock

AD9154 OUT6: AD9144 SYSREF CLK

AD9154 OUT7: FPGA SYSREF CLK

AD9154 OUT9: FPGA gtx 输入时钟

AD9144 Ref clk:3.2G/20=160M

3.4.2实验效果

按下KEY4 配置AD9144和AD9516

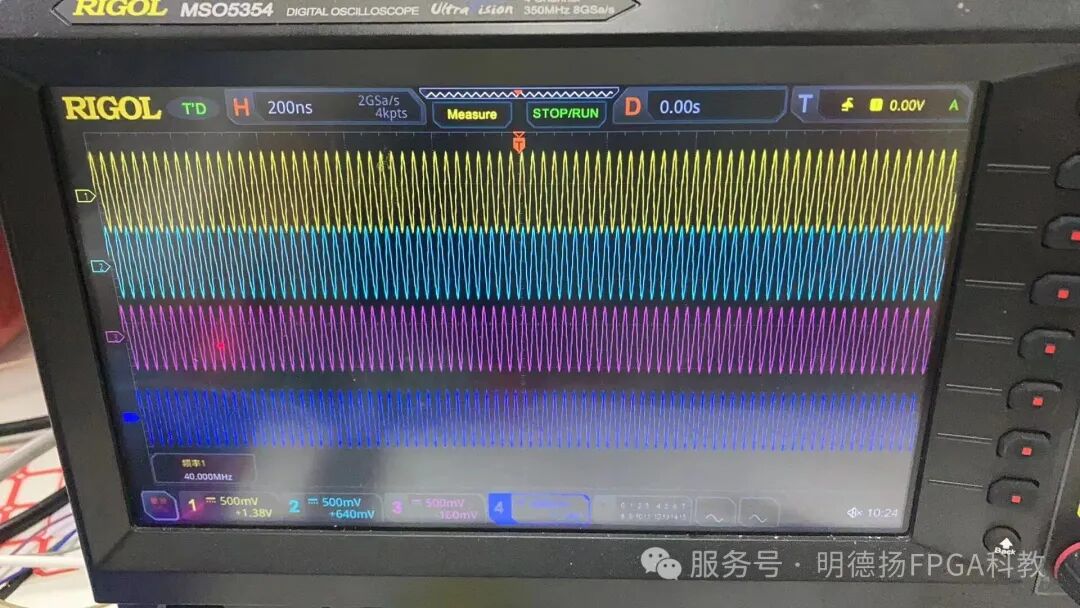

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

3.5模式六:

测试现象:下载完成之后,按下MP5620的KEY4键进行AD9516和AD9144的配置,配置完成之后示波器会有波形显示。按KEY5键,频率每次会在之前的基础上×2。

AD9144 640M采样率,内插为4,AD9144各通道的输入采样率为160M。

3.5.1参数配置

AD9144模式6 参数配置:MODE=6。

M:2

L:2

S:1

F:2

AD9144采样率Fs为160M, 16bit

总lane线速率=(Fs/S)*F*L*8 =(160/1)*2*2*8=5120Mbps

每个lane线速率=5120/2=2500Mbps=2.56Gbps

8b10b编码之后线速率=2.56*1.25=3.2Gbps

设K=32,R=4

LMFC=(160/S/K)=160M/1/32= 5M

Sysref = LMFC/R=5M/4 = 1.25M

JESD204 TX_DATA时钟=160M/2= 80M

计算参考 AD9144 MODE 6的lane数据重组章节

AD9514各通道输出的关系:

AD9154 OUT1:device clock

AD9154 OUT6: AD9144 SYSREF CLK

AD9154 OUT7: FPGA SYSREF CLK

AD9154 OUT9: FPGA gtx 输入时钟

AD9144 Ref clk:3.2G/20=160M

3.5.2实验效果

按下KEY4 配置AD9144和AD9516

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

3.6模式七:

测试现象:下载完成之后,按下MP5620的KEY4键进行AD9516和AD9144的配置,配置完成之后示波器会有波形显示。按KEY5键,频率每次会在之前的基础上×2。

AD9144 640M采样率,内插为8,AD9144各通道的输入采样率为80M。

3.6.1参数配置

AD9144模式7 参数配置:MODE=7。

M:2

L:1

S:1

F:4

AD9144采样率Fs为80M, 16bit

总lane线速率=(Fs/S)*F*L*8 =(80/1)*4*1*8=2560Mbps

每个lane线速率=2560/1=2500Mbps=2.56Gbps

8b10b编码之后线速率=2.56*1.25=3.2Gbps

设K=16,R=4

LMFC=(160/S/K)=80M/1/16= 5M

Sysref = LMFC/R=5M/4 = 1.25M

JESD204 TX_DATA时钟=80M/1= 80M

AD9514各通道输出的关系:

AD9154 OUT1:device clock

AD9154 OUT6: AD9144 SYSREF CLK

AD9154 OUT7: FPGA SYSREF CLK

AD9154 OUT9: FPGA gtx 输入时钟

AD9144 Ref clk:3.2G/40=80M

3.6.2实验效果

按下KEY4 配置AD9144和AD9516

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

3.7模式九:

测试现象:下载完成之后,按下MP5620的KEY4键进行AD9516和AD9144的配置,配置完成之后示波器会有波形显示。按KEY5键,频率每次会在之前的基础上×2。

AD9144 640M采样率,内插为2,AD9144各通道的输入采样率为320M。

3.7.1参数配置

AD9144模式9 参数配置:MODE=9。

M:1

L:2

S:1

F:1

AD9144采样率Fs为320M, 16bit

总lane线速率=(Fs/S)*F*L*8 =(320/1)*1*2*8=5120Mbps

每个lane线速率=5120/2=2560Mbps=2.56Gbps

8b10b编码之后线速率=2.56*1.25=3.2Gbps

设K=32,R=4

LMFC=(Fs/S/K)=320M/1/32= 10M

Sysref = LMFC/R=10M/4 = 2.5M

JESD204 TX_DATA时钟=320M/4= 80M

计算参考 AD9144 MODE 9的lane数据重组章节

AD9514各通道输出的关系:

AD9154 OUT1:device clock

AD9154 OUT6: AD9144 SYSREF CLK

AD9154 OUT7: FPGA SYSREF CLK

AD9154 OUT9: FPGA gtx 输入时钟

AD9144 Ref clk:3.2G/20=160M

3.7.2实验效果

按下KEY4 配置AD9144和AD9516

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

3.8模式十:

测试现象:下载完成之后,按下MP5620的KEY4键进行AD9516和AD9144的配置,配置完成之后示波器会有波形显示。按KEY5键,频率每次会在之前的基础上×2。

AD9144 640M采样率,内插为4,AD9144各通道的输入采样率为160M。

3.8.1参数配置

AD9144模式10 参数配置:MODE=9。

M:1

L:1

S:1

F:2

AD9144采样率Fs为160M, 16bit

总lane线速率=(Fs/S)*F*L*8 =(160/1)*1*2*8=2560Mbps

每个lane线速率=2560/1=2560Mbps=2.56Gbps

8b10b编码之后线速率=2.56*1.25=3.2Gbps

设K=32,R=4

LMFC=(160/S/K)=320M/1/32= 10M

Sysref = LMFC/R=10M/4 = 2.5M

JESD204 TX_DATA时钟=160M/2= 80M

计算参考 AD9144 MODE 10的lane数据重组章节

AD9514各通道输出的关系:

AD9154 OUT1:device clock

AD9154 OUT6: AD9144 SYSREF CLK

AD9154 OUT7: FPGA SYSREF CLK

AD9154 OUT9: FPGA gtx 输入时钟

AD9144 Ref clk:3.2G/20=160M

3.8.1实验效果

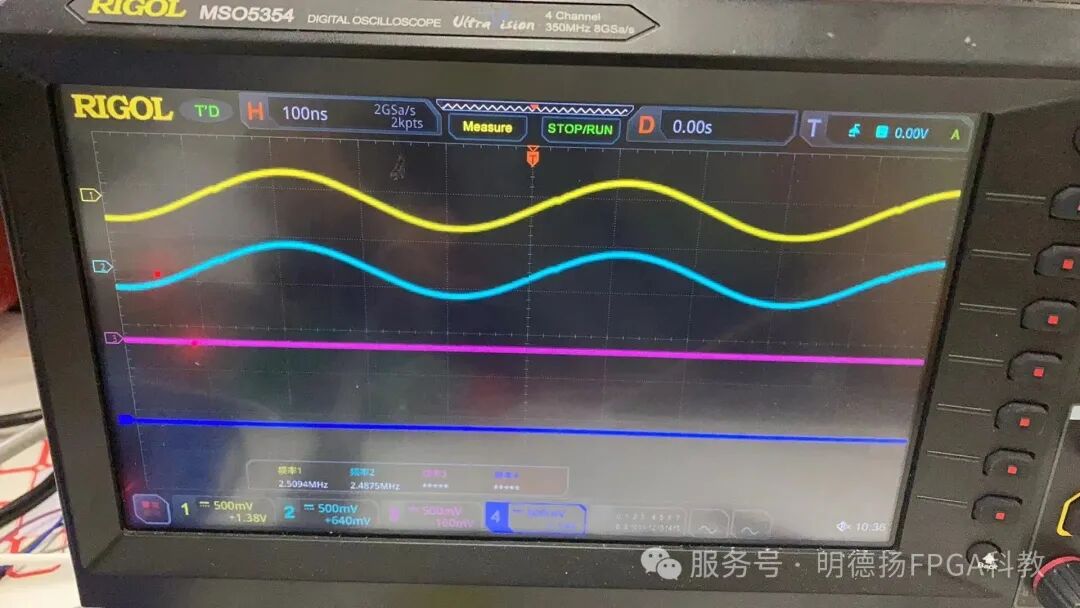

按下KEY4配置AD9144和AD9516

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

再按KEY5改变频率

四、总结

以上即为 AD9144 八大工作模式实测验证内容,多维度参数配置全覆盖,有效解决高速 JESD204B 开发调试难点。