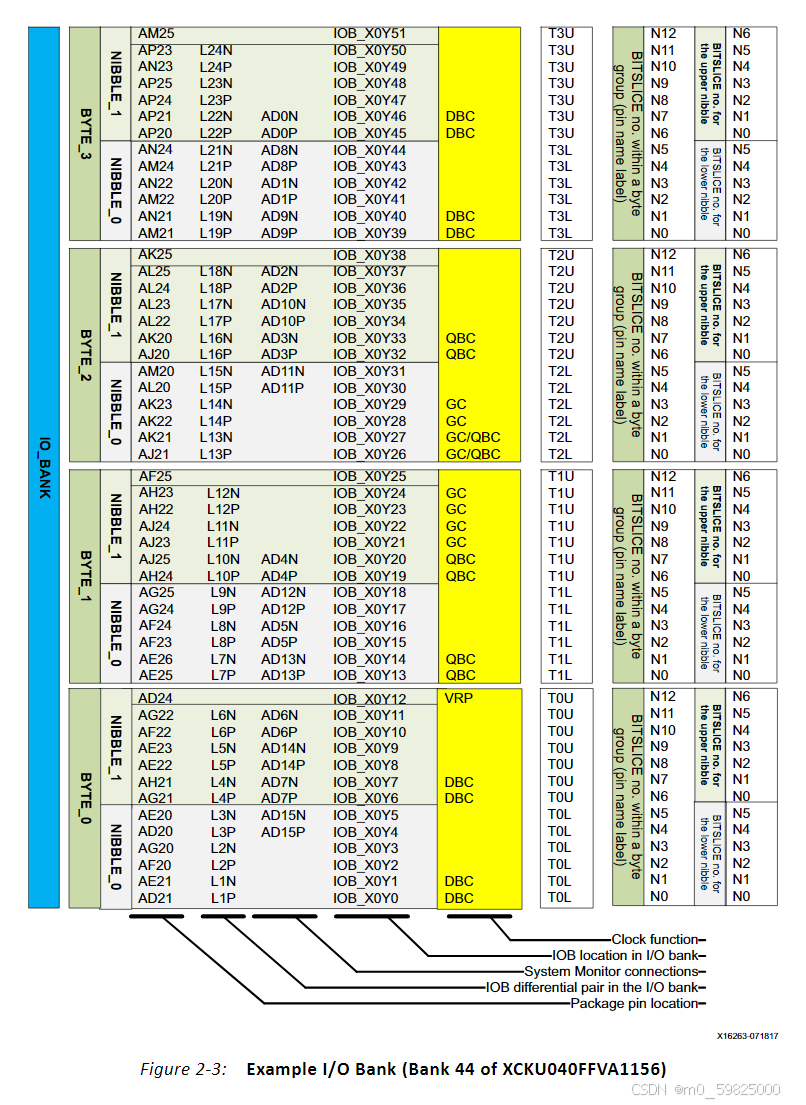

在了解DDR4引脚分配设计规则之前先了解一下BANK中的一些规则,图片摘自UG571 P149:

1.每个BANK中的每个BYTE被分为N0到N12

2.每个BYTE中没分为T0、T1、T2、T3,而每个字通道内又在后面添加U和L来进行区分,T0L, T0U, T1L, T1U, T2L, T2U, T3L, T3U

在了解每个BANK的引脚分配规则后再来了解DDR4的引脚设计规则,DDR4 Pin Rules在文档PG150 P102中,大概规则如下:

1.DQS、DQ、DM/DBI设计规则

a.使用X8或X16器件(X16指数据位的位宽,如MT40A256M16GE_083E-IT中M16表示X16),DQS必须接到一个Byte中专用的时钟管脚上,TxU中N6和N7。DQ必须接到同一Byte中除了N1和N12的其他引脚中

b.使用X4器件,DQS必须连接到低字节中的N0、N1或高字节中的N6、N7。DQ必须接到同一Byte中除了N1和N12的其他引脚中,DM/DBI在X4器件中不被支持

d.X16器件中两个DQ组必须与两个相邻的Byte连接

2.X4器件必须成对使用,不允许有奇数个X4器件。一个Byte中两个子字节必须都由X4的DQ/DQS组来使用。每个Byte中两个X4的子字节必须使用两个从最小的数开始数的一对。例如一个Byte中只能是连接0和1或者2和3,但不能连接1和2

3.带有DQS的Byte被视为数据通道。如果数据引脚与其他的控制/地址引脚属于同一个BANK,引脚N1和N12可以被用于连接控制/地址引脚

4.地址/控制脚可以在同一个BANK内的任意的13个引脚上

5.VRP引脚在数据速率低于2133Mb/s时可以当作普通IO口来使用,否则需要串联240欧姆下拉电阻使用DCI阻抗控制

6.CK脚必须连接到与地址/控制引脚相同的BANK内的任意一个PN差分对上

7.Reset_N可以连接到任意一个引脚上,只要满足时序要求和IO标准为LVCMOS12。该引脚应该被下拉以便于DRAM在上电时引脚是低电平的状态,建议使用4.7K电阻进行下拉

8.BANKs可以被两个控制器共同使用

a.每个Byte通道都专用与特定的控制器(Reset_N引脚除外)

b.一个控制器中的Byte通道不能被放到另一个控制器中,例如有控制器A和B,AABB可以被允许,但是不允许有ABAB

如果两个控制器共用一个Bank,那么他们就不能分别进行复位操作,必须使用一个复位输入

9.所有的IO BANK在存储接口中必须使用同一列

10.对于采用 SSI 技术的设备而言,内存接口所使用的所有 I/O 通道都必须位于同一列的相同 SLR(存储器层)中

11.接口最大高度支持5个连续的BANK,最大支持80bit的接口

12.禁止跳过BANK使用

13.存储接口中输入时钟MMCM必须接入GCIO pair

14.Vref引脚在使用DDR4的时候必须通过一个500R或1K的电阻下拉到地

15.接口必须包含在HP BANK,除Reset_n引脚以外其他引脚不允许使用其他类型的BANK

16.如果这个Byte被用于内存接口,那么sys_rst_n不能被分配到N0和N6

引脚交换规则

1.每个Byte中除了DQS和DQM以外都可以随意交换

2.Byte组(数据、地址/控制)可以随意交换

3.地址/控制脚可以在同一Byte组内或Byte组之间随意交换