目录

[LPC(Low Pin Count)](#LPC(Low Pin Count))

[IIC(Inter-Integrated Circuit)](#IIC(Inter-Integrated Circuit))

[SRIO(Serial RapidIO)](#SRIO(Serial RapidIO))

[USB 3.0](#USB 3.0)

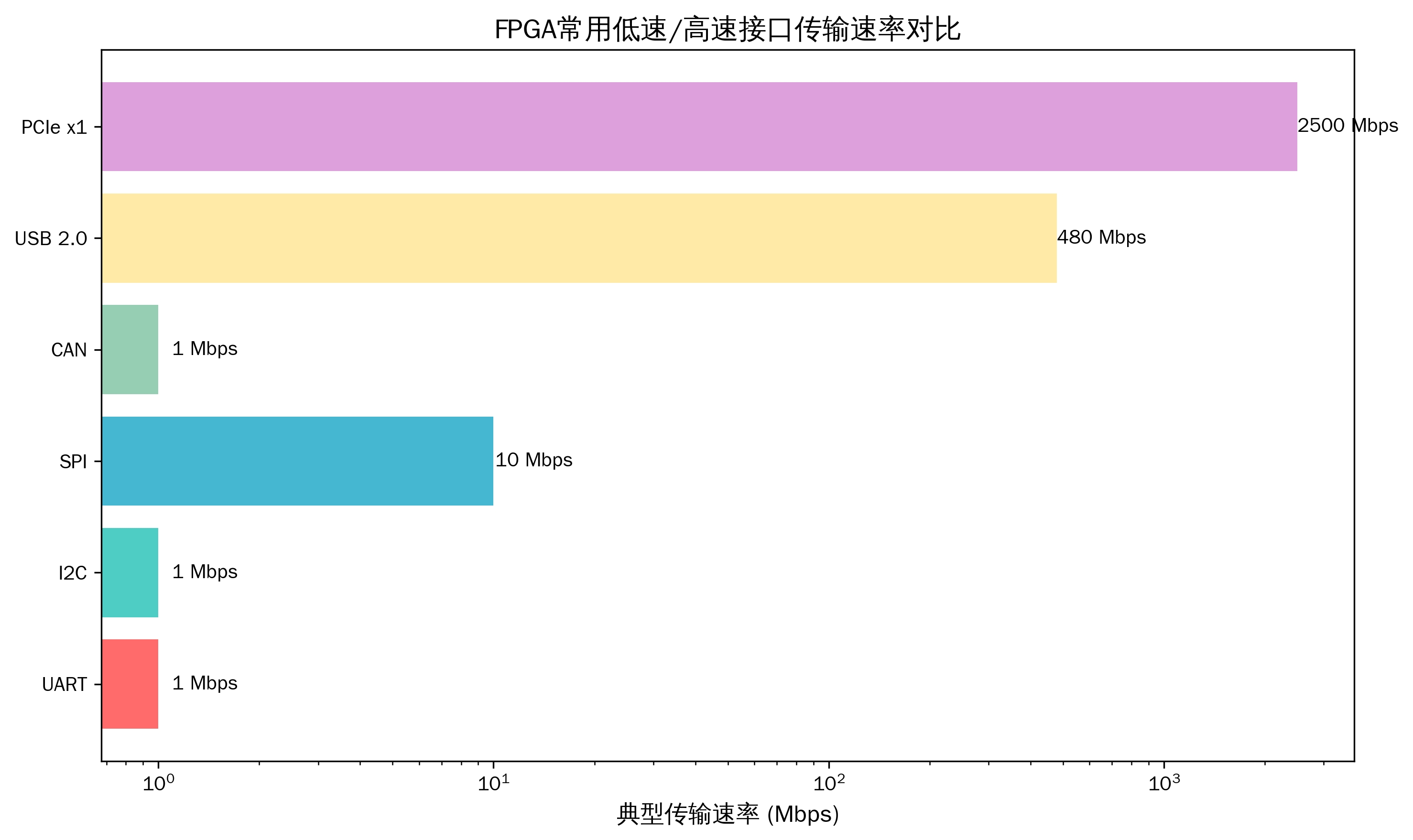

低速接口(适合控制信号、小批量数据传输)

- SPI

- LPC

- uart

- IIC

- 自定义并行或串行总线

高速接口(适合大数据量、高带宽传输)

- 自定义并行或串行总线

- MIPI

- BT.1120/BT.656

- SRIO

- PCIe

- QPI

- LVDS

- SGMII(高速网络接口、以太网物理层接口)

- USB 3.0

- AXI(片内互联总线)

- PLB(片内互联总线)

高速接口(板级 CPU-FPGA)

- PCIe

- SRIO

- LVDS

- 自定义高速并行 / 串行总线

视频专用高速

- MIPI

- BT.656 / BT.1120

网络扩展

- SGMII

片内总线(不对外)

- AXI

- PLB

低速接口

SPI(串行外设接口)

核心特点:串行同步通信,4线(CS、CLK、MOSI、MISO),主从模式,速率通常<50Mbps

典型应用场景:CPU配置FPGA寄存器、读取传感器数据、Flash加载

可作为主/从设备,需严格同步时钟沿,注意始时钟约束,避免跨时钟域问题

同步串行主从接口,由 Motorola 定义,FPGA 与 CPU/Flash/ 传感器的最常用控制接口。

- SCK:串行时钟(主机输出)

- MOSI:主发从收

- MISO:主收从发

- CS/SS:片选(低有效)

- 单主多从(独立片选):最常用,FPGA 做主,每个从机独立 CS

- 菊花链:极少用,FPGA 一般不推荐

- 同步时钟驱动,全双工

- 支持 4 种时钟极性 / 相位模式(CPOL/CPHA)

- 速率:典型 10~50MHz,FPGA 可跑到 100MHz+

- 优点:速率高、全双工、协议简单、FPGA 极易实现

- 缺点:无应答、无纠错、引脚比 I2C 多

- 必须做时序约束

- 推荐做主设备,不推荐做从设备(复杂)

- 适合:CPU 配置 FPGA 寄存器、高速小数据读写

LPC(Low Pin Count)

核心特点:低引脚数总线,Intel定义的低速并行接口,速率<33MHz

典型应用场景:飞腾、x86等CPU连接FPGA实现低速IO、键盘鼠标等外设扩展

需模拟LPC时序,处理帧同步和地址译码,适合替代传统ISA总线

Intel 定义,用于替代 ISA 的低速并行总线 ,是飞腾 / 龙芯 / X86与 FPGA 通信的标准低速接口。

LCLK、LFRAME、LAD [3:0],共7 根线

- 时钟:33MHz

- 半双工

- 面向 x86 / 飞腾平台的传统控制总线

- FPGA 必须严格模拟 LPC 时序

飞腾 CPU ↔ FPGA 低速控制、IO 扩展、传统外设替代

UART(通用异步收发器)

核心特点:异步串行通信,全双工,速率通常为9600bps~1Mbps

典型应用场景:调试串口、控制台交互、低速数据透传

需实现波特率发生器、奇偶校验和帧检测,常用作调试接口

UART 是点对点异步串行通信,无时钟线,依靠双方约定波特率同步,是 FPGA 最基础的调试 / 控制接口。

- TX:发送

- RX:接收

- GND

| 字段 | 位数 | 说明 |

|---|---|---|

| 起始位 | 1bit | 固定低电平,标志传输开始 |

| 数据位 | 5/6/7/8bit | 常用 8bit |

| 校验位 | 0/1bit | 奇校验 / 偶校验 / 无校验 |

| 停止位 | 1~2bit | 固定高电平,标志传输结束 |

- 标准波特率:9600、115200、921600bps

- 最高速率:典型≤1Mbps(FPGA 可做到 10Mbps,但稳定性下降)

- 通信方式:全双工、点对点

- 错误检测:仅奇偶校验

- 须做波特率发生器

- 跨时钟域处理(CDC)

- 适合:调试打印、CPU 简单指令下发、低速状态回读

【串口通信】UART_一路串口和串口屏进行通信电路-CSDN博客

IIC(Inter-Integrated Circuit)

核心特点:串行同步通信,2线(SCL、SDA),多主多从,速率<1Mbps(Fast-mode-Plus)

典型应用场景:配置外设(如EEPROM、传感器)、小容量数据读写

需实现IIC控制器,处理仲裁和时钟拉伸,适合连接多个低速外设

由 NXP 定义的两线制多主多从同步串行总线,用于低速设备控制。

- SCL:串行时钟

- SDA:串行数据

- 需上拉电阻共 2 根线

- 起始条件:SCL 高时,SDA 下降沿

- 地址帧:7/10 位地址 + 1 位读写位

- ACK 应答:每字节后必须有应答

- 数据帧:每次 8bit

- 停止条件:SCL 高时,SDA 上升沿

- 标准:100kbps

- 快速:400kbps

- 快速 +:1Mbps

- 高速:3.4Mbps

- 多主仲裁:线与机制 + 低电平优先

- 内置 ACK 应答,可靠性高于 SPI

- 必须实现起始 / 停止 / ACK 检测

- 适合:配置外设、读取传感器、多设备共享总线

自定义并行/串行总线

核心特点:由FPGA逻辑自定义,可灵活配置位宽、时钟和协议

典型应用场景:专用控制通道、小批量数据传输

并行总线:注意时许约束和IO电平匹配

串行总线:需实现帧同步和校验,可复用FPGA高速收发器资源

FPGA 根据需求自主设计的私有协议,无标准规范。

- 引脚自定义、时序自定义

- 成本最低、灵活性最高

- 无标准、不可跨平台

- 速率:通常≤50Mbps

必须做:同步时序设计、帧头校验、稳定握手

高速接口

自定义并行/串行总线

核心特点:

并行:位宽8~64bit,时钟可达100~200MHz;

串行:基于FPGA高速收发器(GT),速度可达10Gbps+

典型应用场景:板级间高速数据传输、自定义协议互联

并行:需严格做时序约束和源同步设计;

串行:需实现8B/10B编码、时钟数据恢复(CDR)和链路训练

MIPI

核心特点:移动行业处理器接口,高速差分串行,速率可达6Gbps/通道

典型应用场景:视频图像数据传输(如摄像头、显示接口)

需实现MIPI D-PHY/C-PHY,处理高速差分信号和图像格式转换

移动行业处理器接口,视频图像专用高速接口。

- D-PHY:1~2.5Gbps/lane

- C-PHY:更高密度

- 用于摄像头、显示屏

视频传输、图像处理系统

BT.1120/BT.656

核心特点:数字视频并行/串行接口,用于标清/高清视频传输

典型应用场景:视频监控、图像处理系统

BT.656:并行 8/10bit,27MHz 时钟;BT.1120:高速串行,适合高清视频

需同步视频时序和行场同步信号

ITU 标准数字视频接口。

- BT.656:标清并行,27MHz

- BT.1120:高清串行

视频监控、视频传输

SRIO(Serial RapidIO)

核心特点:串行 RapidIO,高性能嵌入式互联,速率可达 10Gbps / 通道,支持交换式拓扑

典型应用场景:高性能计算、DSP/FPGA/CPU 集群互联

需实现 SRIO 物理层和传输层,支持消息传递和 DMA 传输,适合低延迟、高可靠场景

嵌入式高性能低延迟总线,DSP/FPGA/ 嵌入式 CPU 集群专用。

- 1.25/2.5/5/10Gbps

- 支持交换架构、消息机制、DMA

- 延迟远低于 PCIe

雷达、通信、高性能嵌入式计算

PCIe(高速串行计算机扩展总线)

核心特点:高速串行总线,端到端互联,速率可达 32Gbps / 通道(PCIe 5.0),支持 DMA

典型应用场景:服务器、PC、嵌入式系统中 FPGA 作为协处理器扩展

需实现 PCIe 硬核 IP,配置 BAR 空间、MSI 中断和 DMA 引擎,是目前最主流的 CPU-FPGA 高速互联方案

FPGA 与 CPU 互联的绝对主流标准,所有飞腾、X86、ARM、PowerPC 均原生支持。

- 差分串行、端到端

- 全双工

- 速率:

- Gen2:5Gbps/lane

- Gen3:8Gbps/lane

- Gen4:16Gbps/lane

- 支持 DMA、MSI 中断、BAR 地址空间

- 必须使用 FPGA硬核 PCIe IP

- 适合:大数据交互、FPGA 加速、高速采集

【FPGA】高速接口PCIe_fpga pcie-CSDN博客

QPI

核心特点:Intel QuickPath Interconnect,高速点对点互联,速率可达 8.0GT/s

典型应用场景:Intel Xeon 等 CPU 之间或 CPU 与 FPGA 的直连

需支持 QPI 物理层和协议层,主要用于 Intel 平台的高性能计算场景,应用范围较窄

LVDS(低压差分信号)

核心特点:低压差分信号,并行 / 串行模式,速率可达 1Gbps+

典型应用场景:高速数据采集、板级互联

需使用差分 IO 资源,实现源同步时钟和数据传输,抗干扰能力强,适合中短距离高速传输

并行高速差分接口,FPGA 经典板间互联方案。

- 源同步时钟

- 单路速率:600Mbps~1Gbps

- 抗干扰强

- 并行总线,需严格等长

- IOB 寄存器、时序约束、差分端接

SGMII

核心特点:串行千兆媒体独立接口,是 GMII 的串行版本,速率 1.25Gbps

典型应用场景:千兆以太网物理层接口

需实现 SGMII 到 GMII 的转换,用于连接以太网 PHY 芯片,属于网络扩展接口,非直接 CPU 互联

串行 GMII,千兆以太网 PHY 接口。

USB 3.0

核心特点:高速串行总线,速率 5Gbps,支持主 / 从模式

典型应用场景:外接存储、高速数据采集设备

可作为 USB 设备端,实现大容量数据传输,需集成 USB 3.0 控制器 IP

5Gbps,主从结构,FPGA 常用作从设备。适用:高速数据存储、外接设备

AXI

核心特点:AMBA 总线协议,片内互联,用于 FPGA 内部逻辑与 ARM CPU(如 Zynq)的通信

典型应用场景:片内系统级互联(FPGA 逻辑 ↔ 硬核 CPU)

属于片内总线,需在 FPGA 内部实现 AXI-Lite(控制)、AXI-Stream(数据流)、AXI-Memory(内存访问),不适合板级 CPU-FPGA 互联

AXI:ARM CPU(Zynq)与 FPGA 逻辑互联

【FPGA】AXI总线协议_axi协议时序图详解-CSDN博客

PLB

核心特点:IBM Processor Local Bus,片内并行总线,用于 PowerPC 处理器与 FPGA 逻辑的通信

典型应用场景:片内系统级互联(FPGA 逻辑 ↔ PowerPC CPU)

属于片内总线,已逐步被 AXI 替代,主要用于老款 Xilinx FPGA(如 Virtex-5)

PLB:PowerPC 与 FPGA 逻辑互联

- 控制信号 / 小数据量 :优先选择 SPI/UART/IIC,实现简单、资源占用少。

- 飞腾 / X86 平台 :低速用 LPC ,高速首选 PCIe,兼容性最好。

- 视频传输 :MIPI/BT.1120/BT.656 是行业标准方案。

- 高性能计算集群 :SRIO/PCIe 是主流选择,SRIO 延迟更低,PCIe 生态更完善。

- 片内 CPU(如 Zynq) :直接使用 AXI 总线 实现 FPGA 逻辑与 CPU 的高效互联。