作为一名嵌入式开发者,理解底层硬件与指令集架构是写出高效代码的基础。今天就结合我整理的学习笔记,和大家聊聊 ARM 开发的核心知识点。

一、CPU 架构:CISC 与 RISC 的本质区别

计算机 CPU 内核主要分为两大阵营:

1、CISC(复杂指令集计算机)

代表架构:x86

特点:指令数量多、功能复杂,芯片面积大、功耗高,存在 "2/8 效应"(20% 的指令承担 80% 的工作)

适用场景:PC、服务器等对性能要求极高的领域

2、RISC(精简指令集计算机)

代表架构:ARM、MIPS、RISC-V

特点:指令数量少、格式统一,芯片面积小、功耗低、体积小巧

适用场景:手机、嵌入式设备、便携电子产品

ARM 就是典型的 RISC 架构,凭借低功耗优势,成为了嵌入式领域的绝对主流

二、Cortex

A: Application 应用, 手机、应用电子领域

R: real time 实时性 ,汽车电子 , 航空航天

M: Micro 微控制器 MCU 单片机领域

接下来要学习的imx6ull用的处理器内核则是 Cortex-A7,指令集版本为ARMv7-A(也常简称为 armv7)

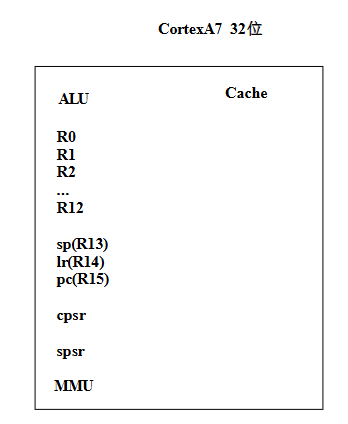

三、Cortex-A7 内核寄存器详解

ALU:算术逻辑单元

R0 - R12 通用寄存器( 内核 ):存放数据

pc寄存器:program counter,程序计数器,本质上是一个指针,指向当前代码正在执行指令的下 一条指令

lr寄存器:linked register,链接寄存器,保存函数返回地址

sp寄存器 :stack pointer,栈指针寄存器 ,用来管理栈区

cpsr寄存器:current program status register, 当前程序状态寄存器 ,保存程序运行到某一步时的状态

spsr寄存器:save program status register,保存/备份程序状态寄存器异,异常发生时,保存cpsr寄存器中的程序状态

MMU:Mermory Manager Unit,内存管理单元用于管理虚拟内存到物理内存映射,从而提高物理 内存的利用率

Cache:高速数据缓存, 直接从Cache访问数据 ,提高CPU访问数据的效率

icache:instruction cache,指令缓存,用于指令

dcache: data cache,数据缓存, 用于数据

(所以ARM普遍使用哈佛架构)

在学习裸机时,必须要关闭MMU,打开 icache,关闭 dcache

四、存储类型与总线

- 存储器类型

RAM:易失性存储器,掉电数据丢失,读写速度快,用于程序运行时数据

ROM/Flash:非易失性存储器,掉电数据不丢失,用于存储程序和固件

Nor Flash:字节可寻址,适合存储代码

Nand Flash:块操作(通常 512 字节),容量大、成本低,适合存储数据

- 总线通信

单总线通信 :通过一根线 /一组线和外设通信,和某个外设通信时,其他外设接不进来

双总线通信 :

AHB总线: 先进高速总线 (USB、网卡 、RAM),连接通信速率快的外设

APB总线:先进外设总线 (GPIO、 UART),连接通信速率慢的外设

为了平衡不同外设的速度,ARM 采用双总线架构

五、程序编译

1、程序编译所经历的阶段

(1)预处理(Pre-Processing):处理和#号相关的代码,将C语言展开、替换、按照条件加入去除

(2)编译(Compiling):将C语言代码编译成汇编代码

(3)汇编(Assembling):将汇编代码编译为机器语言

(4)链接(Linking):将用户的代码与系统中的库链接成一个可执行程序

2、交叉编译:在一个平台编写编译程序,能够在另外 一个平台运行程序

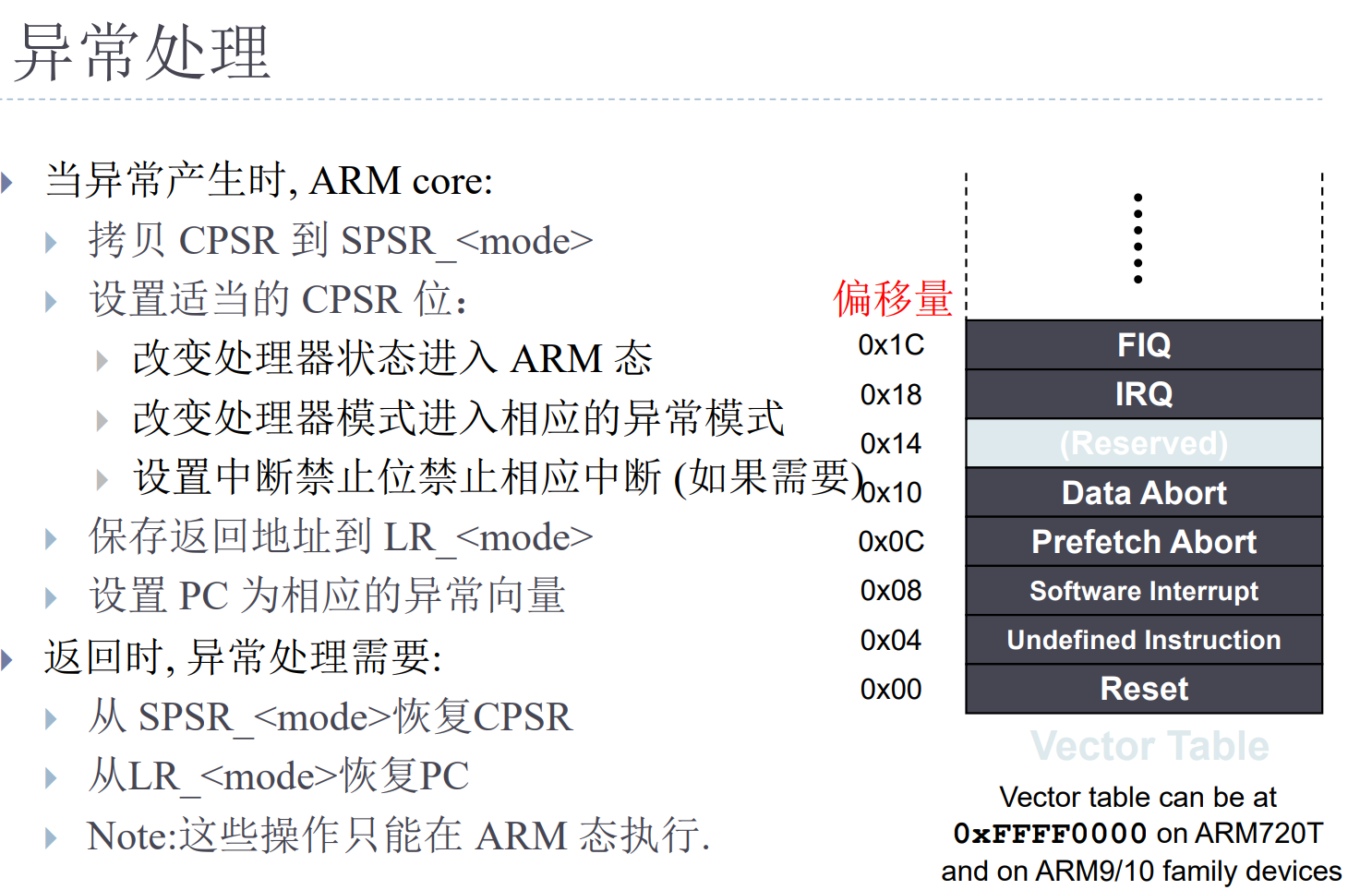

六、异常向量表

本质是一个数组, 数组中存放的是跳转到对应异常服务函数的指令

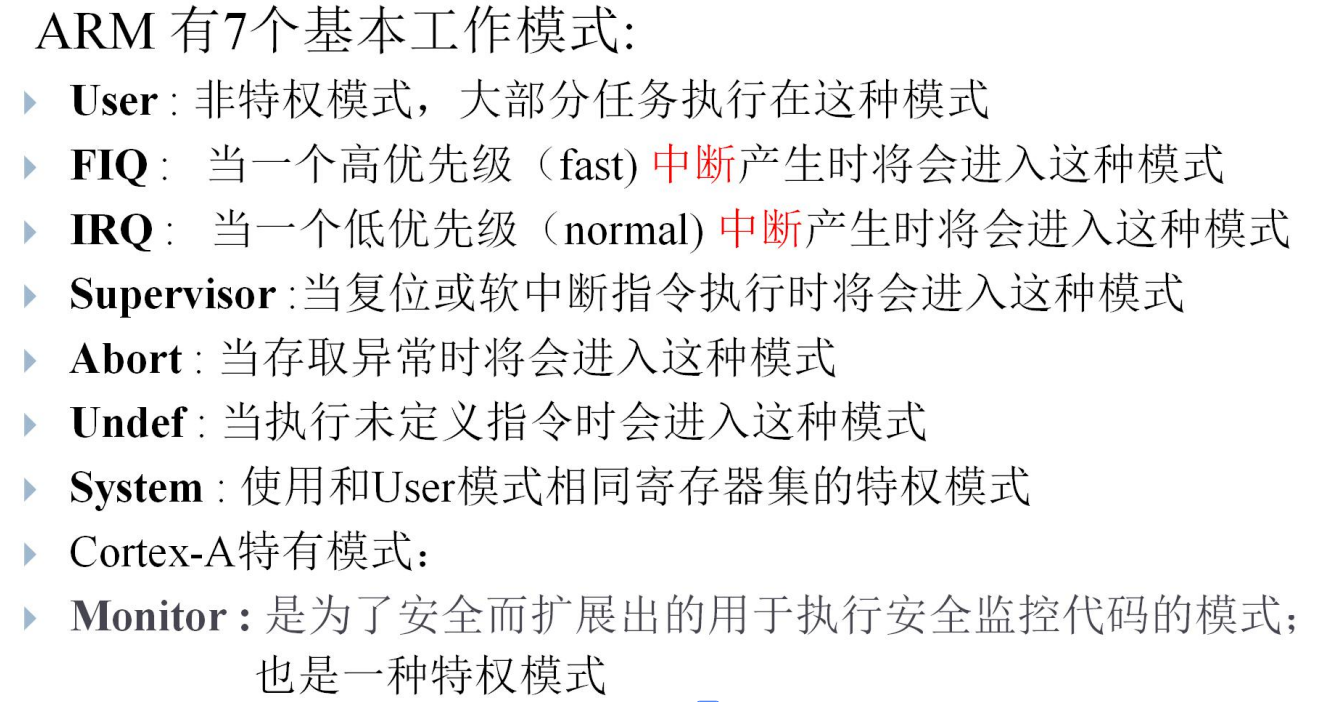

七、处理器工作模式

八、ARM寄存器

ARM 有37个32-Bits长的寄存器

Cortex体系结构下有40个32-Bits长的寄存器