速度设置

打开软件配置页

在JTAG配置区域

- 勾选要修改JTAG通道,设置分频系数

- 设置参数->更新参数(完成设置,无需重启)

- 设置速度2.5M-53M

注意:JTAG速度高速时,ila的时钟不要太慢哦。

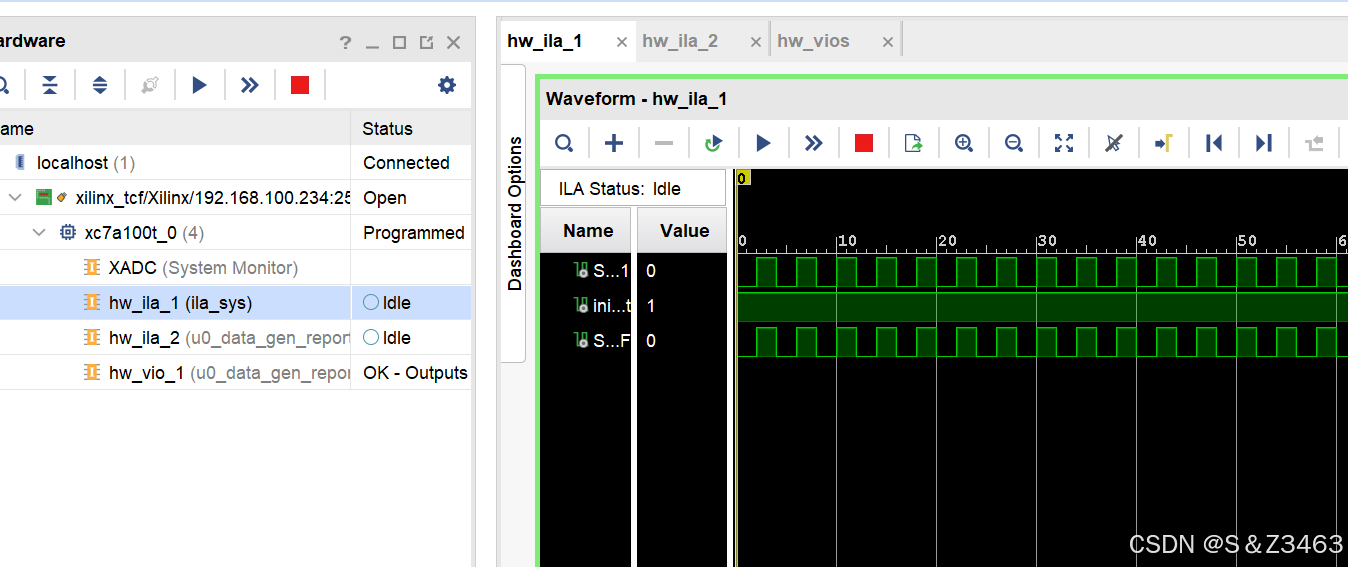

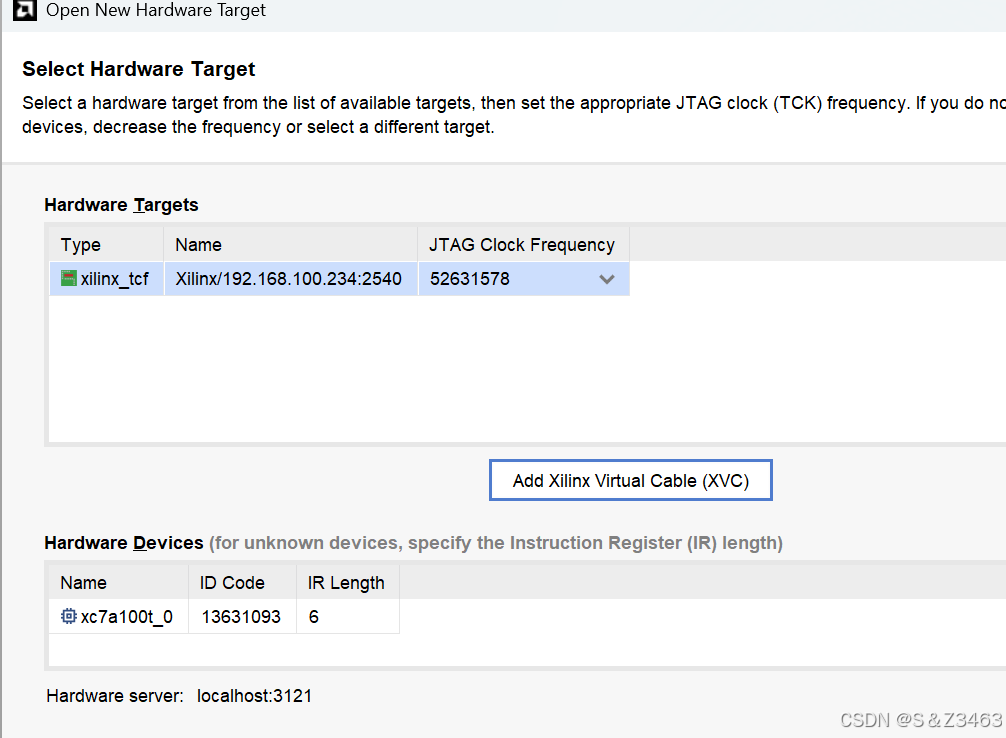

连接FPGA设备

打开Vivado硬件管理界面(Open HwadwareManager)

方法1

-

open target -> Auto Connect或状态栏图标

-

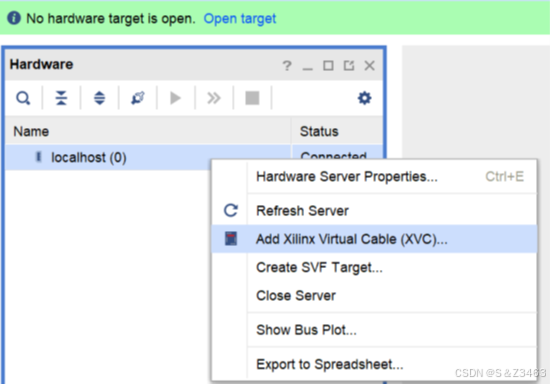

右键localhost,选择Add Xilinx Virtual Cabe(XVC)

-

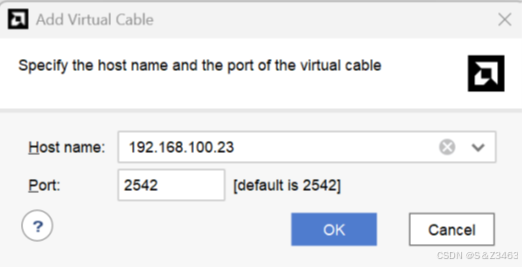

设置设备IP地址及JTAG通道对应端口号并确认

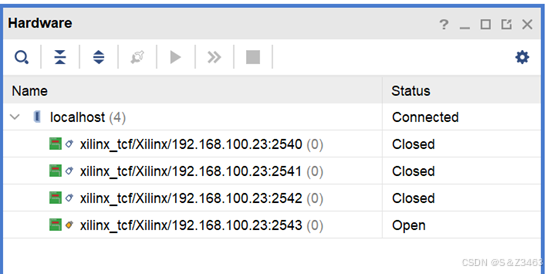

端口号设置可以为2540,2541,2542,2543

分别对应硬件JTAG 0,1,2,3

-

重复2,3步骤,修改不同端口号,可以打开其它JTAG端口

常规模式,同一vivado 仅支持一个FPGA连接,可进行连接切换

常规模式,同一vivado 仅支持一个FPGA连接,可进行连接切换

方法2

VIVADO 正常识别FPGA,速度高达52.6M。

VIVADO 正常识别FPGA,速度高达52.6M。

注意:此过程需要连接FPGA,才可以进行下一步