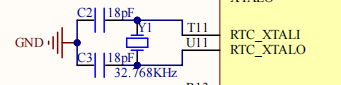

RTC是用来记时间的

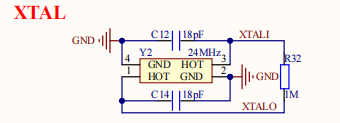

XTAL是内部用于运算的

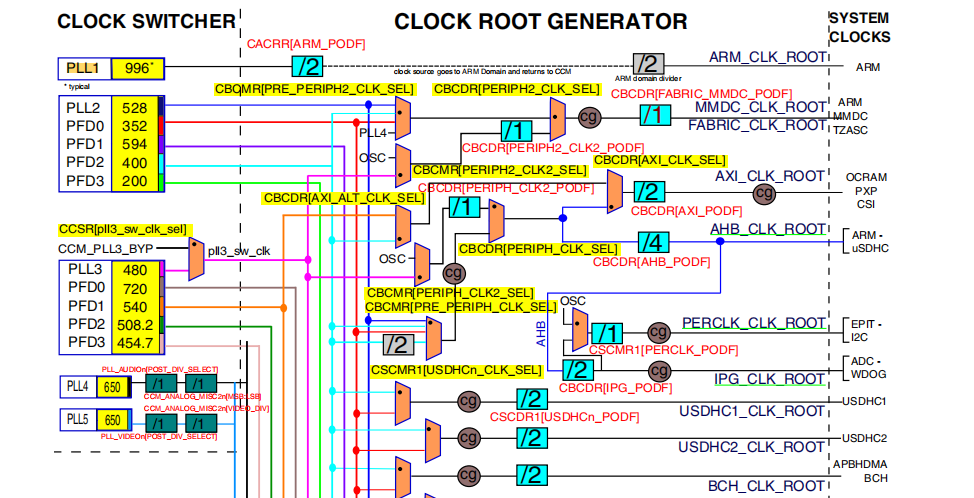

PLL:锁相环----用于倍频

预分频器:用于分频

分频器:类似上面二者组合,可以倍频和分频

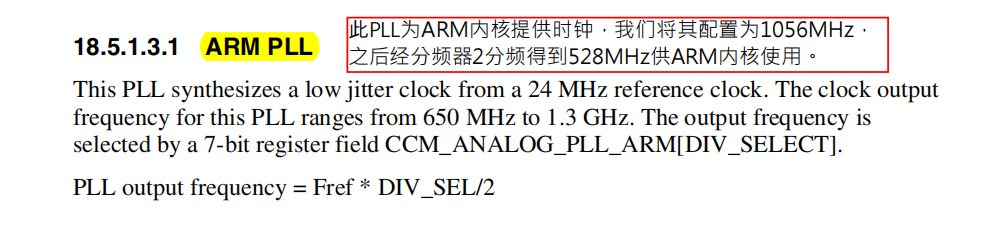

一、PLL1的配置

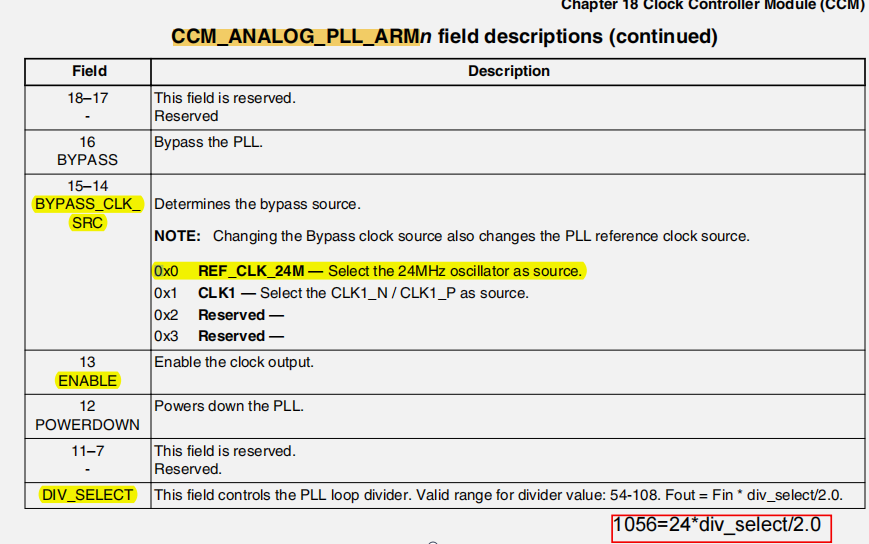

PLL1为ARM内核提供时钟,将其配置为1056MHz,之后经分频器2分频得到528MHz供ARM内核使用。

由于担心分频/倍频过于频繁,最后的频率老是确定不了,导致收到错乱的时钟,使得工作极其不稳定,因此先给最后接上晶振,等待分频/倍频配置完成之后,再给其接上

|-------------------------------------------------|

| 1、先选择osc_clk,让step_clk为 24MHz。 |

| 2、再将PLL1的输出改 成step_clk,让ARM暂时工作在24HZ |

| 3、配置PLL为1056,注意设置倍频因子之前先把PPL之后的二分频设置好,避免ARM内核故障 |

| 4、最后再改回去 |

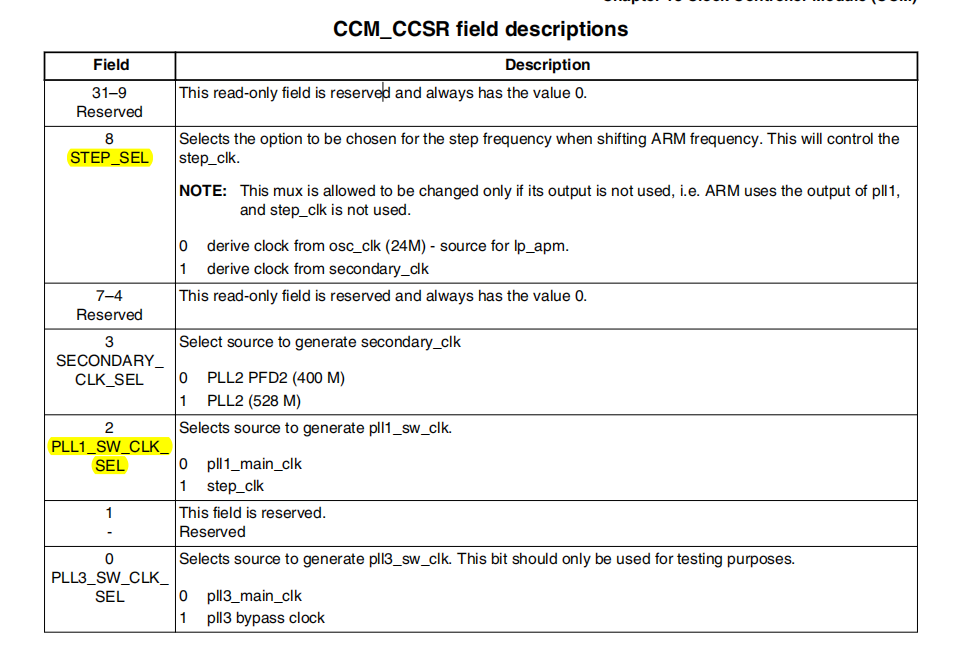

1、先根据下面寄存器,先将step_sel选为24M,再改为step_clk(最后记得配置完改回pll1_main_clk)

2、再根据下面寄存器,先给13位置1使能,再根据公式算出div_select填入最后

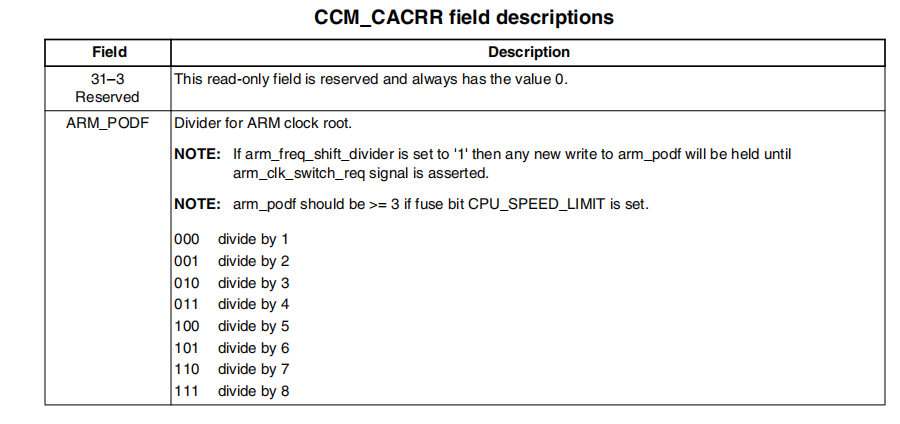

3、根据下面寄存器,将其配置001设置为二分频

cpp

CCM->CCSR &= ~(1<<8);

CCM->CCSR |= (1<<2);

unsigned int tmp = CCM->CACRR;

tmp &= ~(0x7 << 0);

tmp |= (0x1<<0);

CCM->CACRR = tmp;

tmp = CCM_ANALOG->PLL_ARM;

tmp &= ~(0x03<<14);

tmp |=(0x1<<13);

tmp &= ~(0x7f<<0);

tmp |=(88<<0);

CCM->CACRR = tmp;

CCM->CCSR &= ~(1<<2);二、配置PLL2

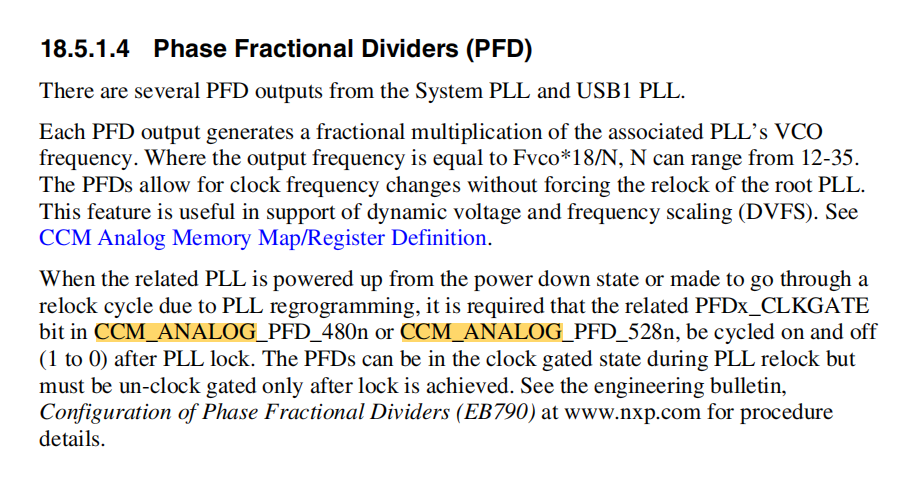

此PLL下有四 个PFD

现在我们需要配置这四个PFD,建议值为:352、594 、400(其实是396)和297

根据下面描述来配置,此次选择CCM_ANALOG_PFD_528n PFD值为528*18/N其中N是要填入寄存器的值

cpp

tmp = CCM_ANALOG->PFD_528;

tmp %= (0x3f << 0) | (0x3f << 8) | (0x3f << 16) | (0x3f << 24);

tmp |= (27 << 0) | (16 << 8) | (24 << 16) | (48 << 24);

CCM_ANALOG->PFD_528 = tmp;三、配置PPL3

方法与上面类似,此次选择CCM_ANALOG_PFD_480n,PFD值为480*18/N其中N是要填入寄存器的值

cpp

tmp = CCM_ANALOG->PFD_480;

tmp %= (0x3f << 0) | (0x3f << 8) | (0x3f << 16) | (0x3f << 24);

tmp |= (12 << 0) | (16 << 8) | (17 << 16) | (19 << 24);

CCM_ANALOG->PFD_480 = tmp;四、配置最后的分频器等

根据最上图,此次需配置PERCLK_CLK_ROOT、AHB_CLK_ROOT、IPG_CLK_ROOT这些常用,根据图片配置其分频器与选择器件

cpp

tmp = CCM->CBCDR;

tmp &= ~(0x07 << 10);

tmp |= (0x2 << 10);

tmp &= ~(0x1<<25);

CCM -> CBCDR = tmp;

tmp = CCM->CBCMR;

tmp &= ~(0x3 << 18);

tmp |= (1 << 18);

CCM ->CBCMR = tmp;

tmp = CCM -> CBCDR;

tmp &= ~(0x3 << 8);

tmp |= (0x1 << 8);

CCM -> CBCDR = tmp;

tmp = CCM ->CSCMR1;

tmp &= ~(0x7f<<0);

CCM -> CSCMR1 = tmp;