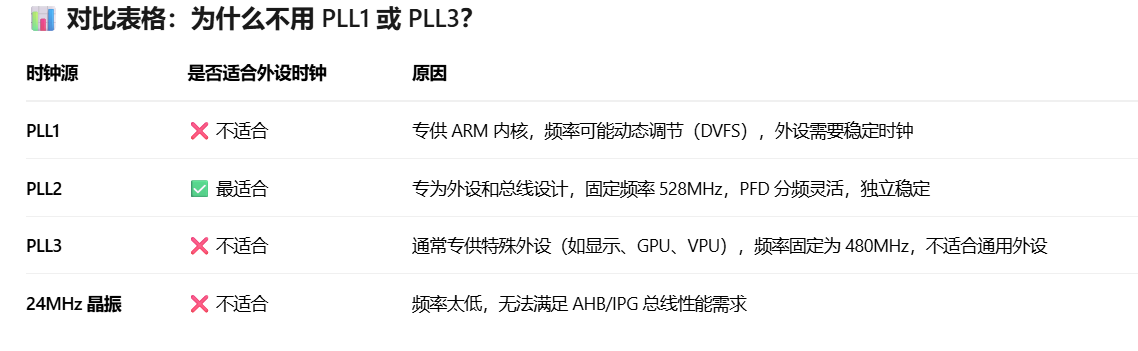

一、时钟系统概述

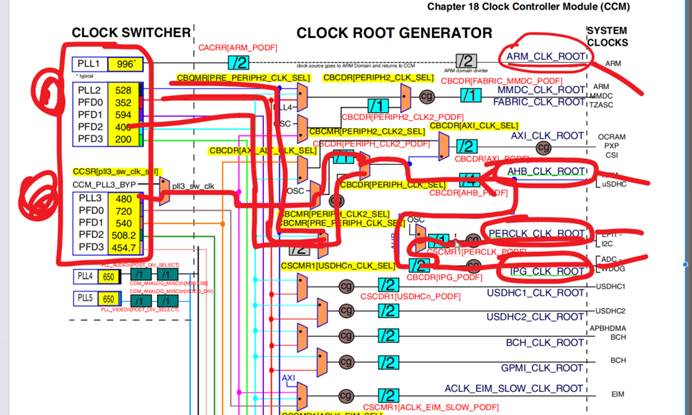

i.MX6ULL 的时钟系统由多个 PLL(锁相环)和分频器组成,通过寄存器配置来选择时钟源和分频比,最终为 ARM 内核、总线和各外设提供所需的工作频率。

1.1 频率说明

- 996 MHz:建议值,非固定值,通常不选用此频率

- 996 MHz → ÷2 → 给 ARM → ÷2 → 给 CPU

- 528 MHz:官方建议值,最高支持到 1.3 GHz,为固定值无法修改

- 480 MHz:固定值,无法修改

📌 528 MHz 和 480 MHz 是固定频率,软件无法更改,需优先完成配置。

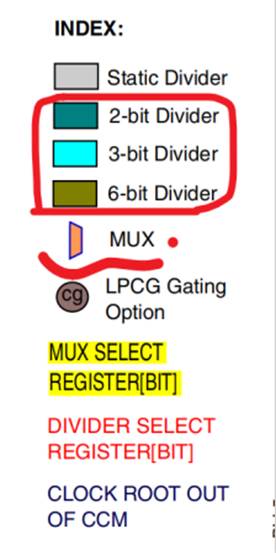

1.2 时钟分频器模块结构

下图展示时钟分频器模块的寄存器配置与结构索引,用于说明如何通过寄存器位选择不同分频器类型,控制时钟输出:

1.3 时钟路径总览

整个时钟系统的信号流向如下:

时钟源\] ──→ \[PLL\] ──→ \[预分频器\] ──→ \[分频器\] ──→ \[外设时钟

↑ ↑

PRE_PERIPH_CLK_SEL PERIPH_CLK2_SEL

1.4 需要配置的寄存器

以下寄存器需要依次完成配置:

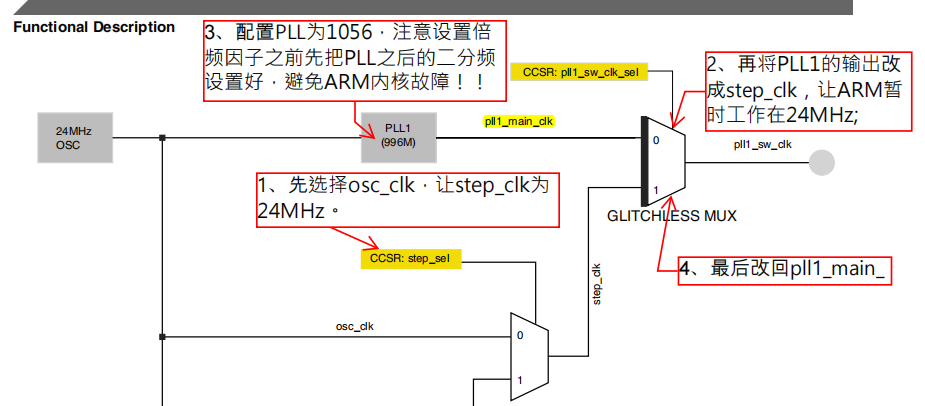

二、ARM 内核时钟配置(PLL1)

ARM 内核时钟由 PLL1 提供。配置步骤如下:

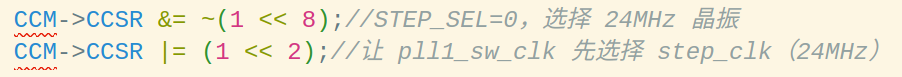

第一步:设置 CCSR 寄存器

配置 CCSR 中的 STEP_SEL 和 PLL_SW_CLK_SEL 字段:

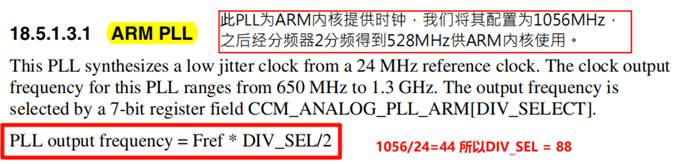

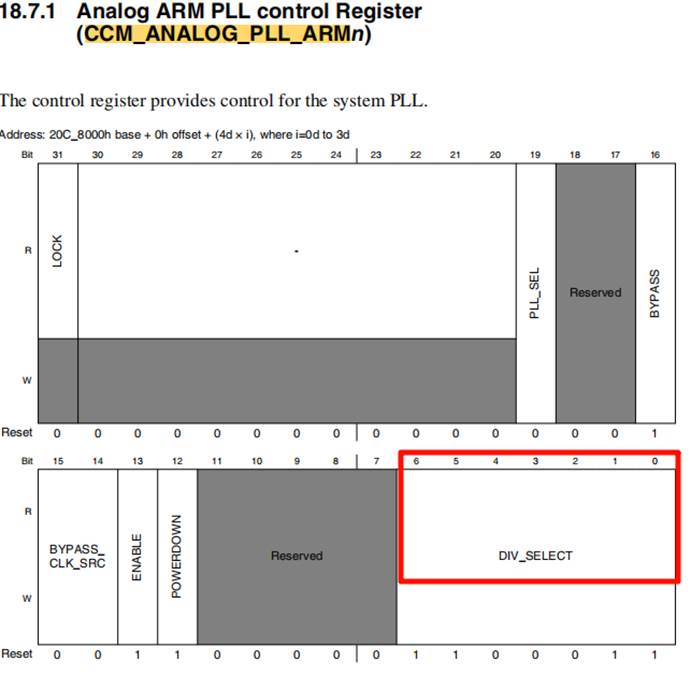

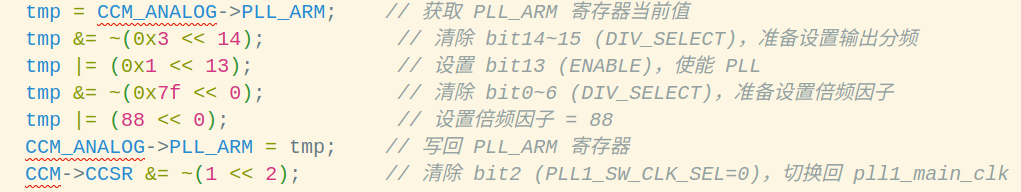

第二步:设置 CCM_ANALOG_PLL_ARMn

配置 PLL1(ARM PLL)的倍频系数:

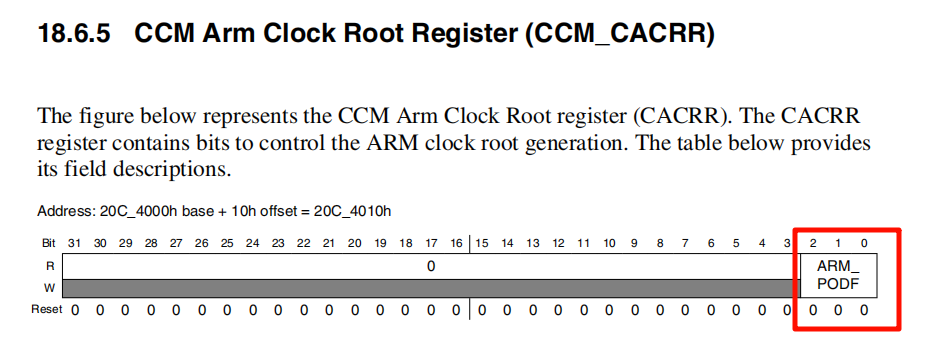

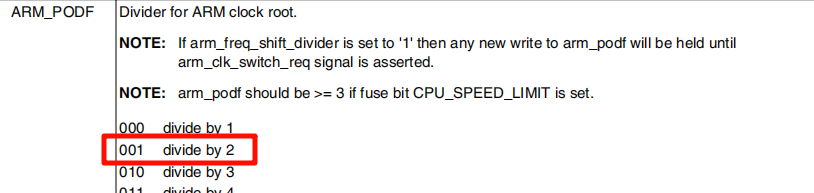

第三步:设置 CCM_CACRR --- ARM_PODF 2分频

将 CCM_CACRR 寄存器中的 ARM_PODF 字段设置为 2 分频:

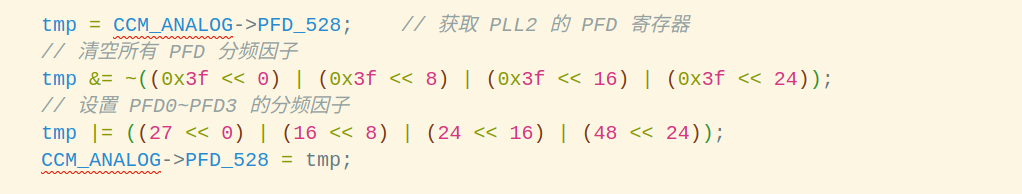

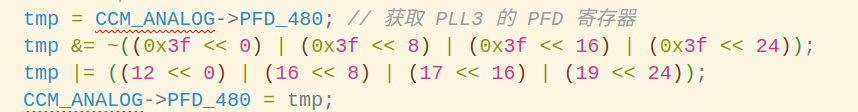

三、配置 PLL2 和 PLL3

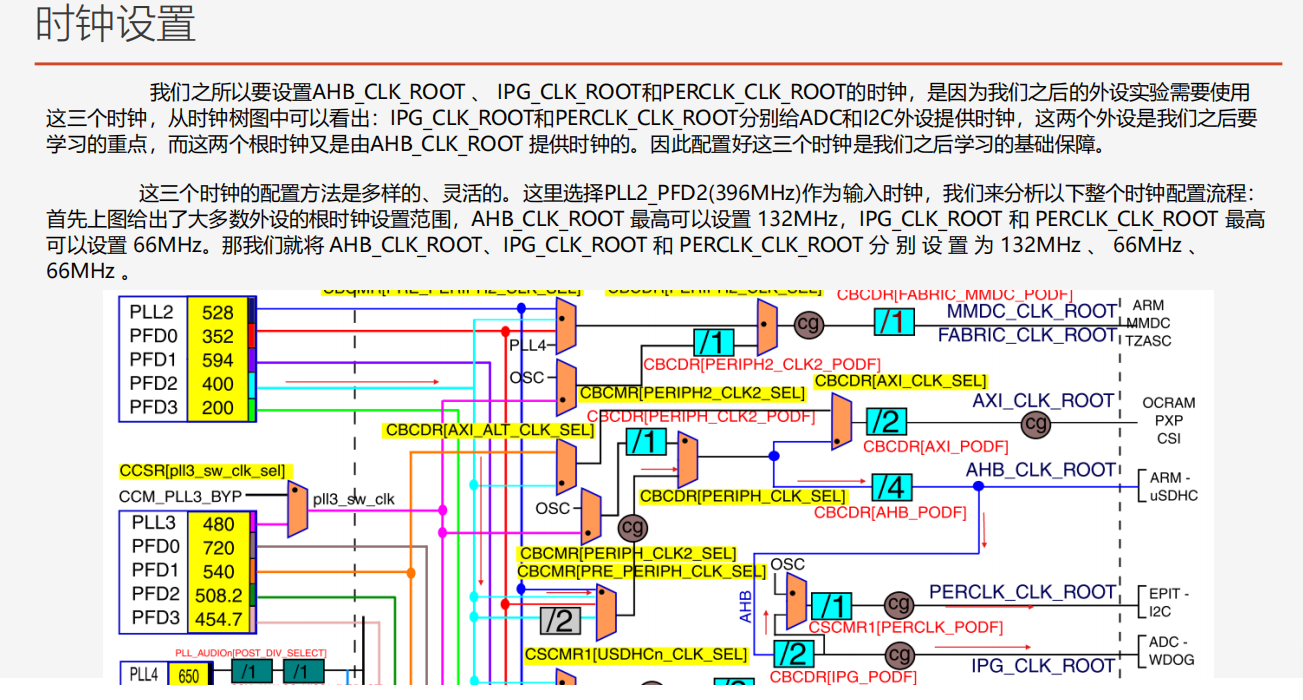

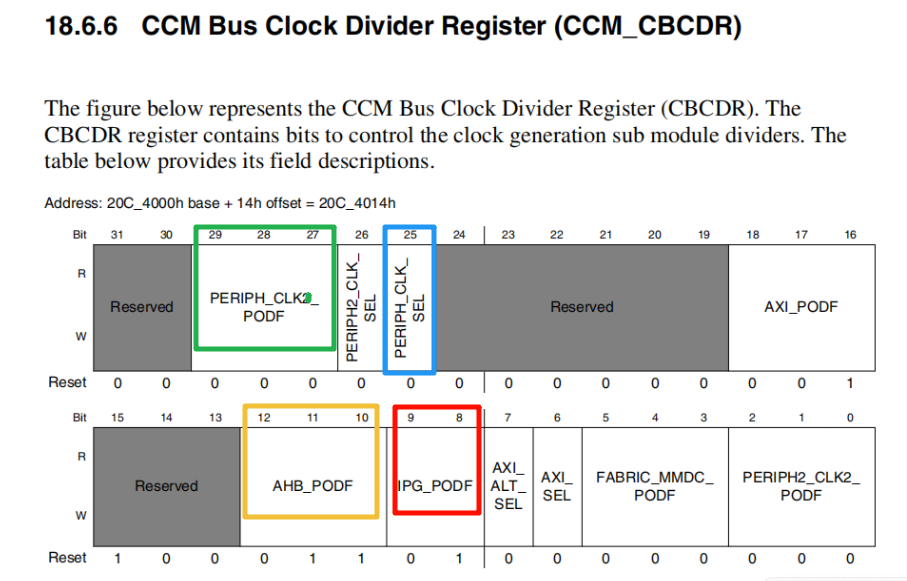

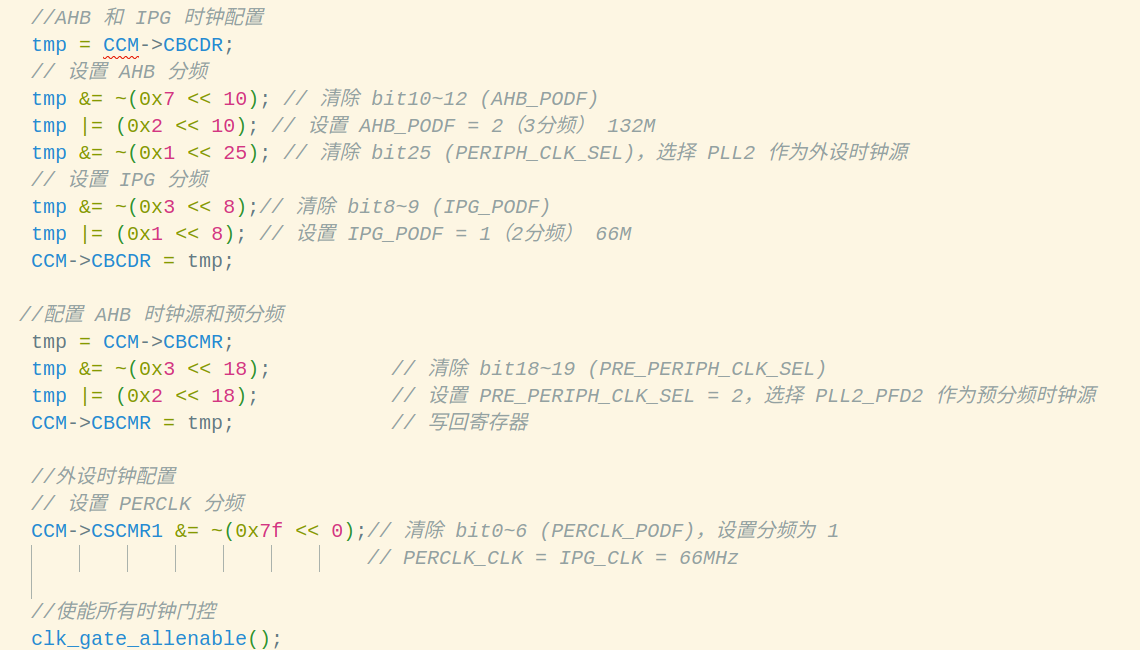

四、配置总线时钟

4.1 配置对象

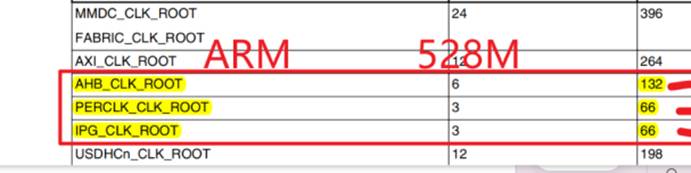

需要依次配置以下三个总线时钟根节点:

- AHB_CLK_ROOT

- IPG_CLK_ROOT

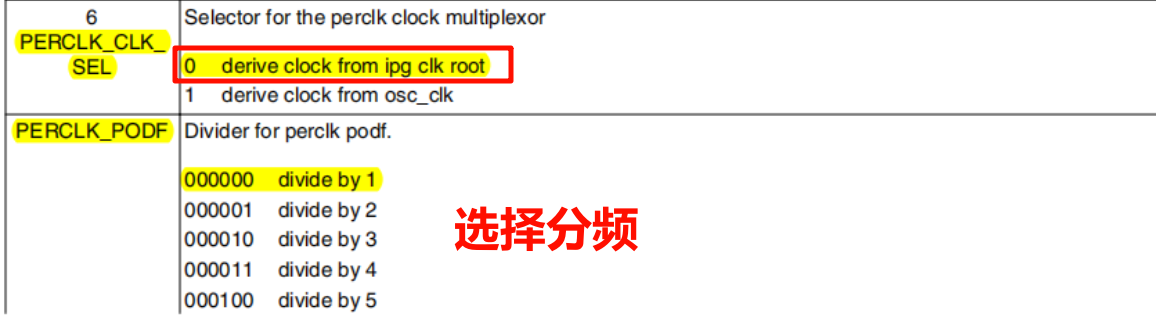

- PERCLK_CLK_ROOT

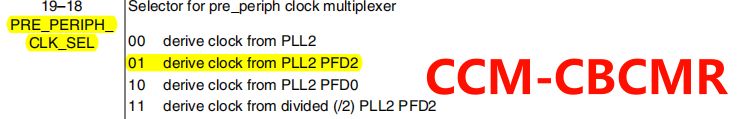

4.2 分频策略

时钟源选择 PLL2_PFD2,分频步骤如下:

- PLL2_PFD2 → ÷3 → AHB_CLK_ROOT

- AHB_CLK_ROOT → ÷2 → IPG_CLK_ROOT

- IPG_CLK_ROOT → ÷1 → PERCLK_CLK_ROOT

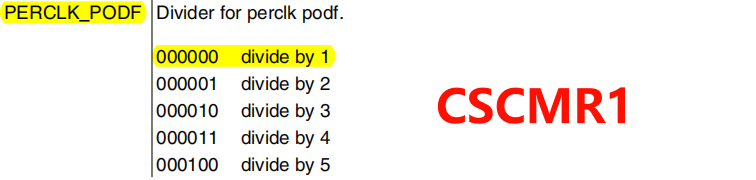

4.3 寄存器配置

-

至此时钟设置完毕,某些外设 我们在需要的时候再来设置。 下载程序后看不出有太大的变 化,对于PLL1来说,如果Led采用软件 延时周期性闪烁的话,经过设置会闪烁 得更快些。其他的频率是否正确只能在 使用相关外设的时候才能验证。