基于FPGA的QAM调制解调,有详细实验文档

概述

本系统实现了一个完整的 16QAM(16-Quadrature Amplitude Modulation) 调制与解调链路,部署于 Altera Cyclone IV GX 系列 FPGA 平台上。系统以 PN 序列 作为原始数据源,通过调制、载波调制、DAC 输出、载波解调、滤波、符号判决等环节,最终还原原始比特流,可用于通信原理教学、信号处理实验或 FPGA 基带系统验证。

基于FPGA的QAM调制解调,有详细实验文档

系统整体架构分为 调制通路 与 解调通路 两大模块,并辅以 时钟管理、信号选择、I²C 配置接口 等外围控制逻辑,支持灵活的信号观测与参数配置。

一、系统顶层结构

系统顶层模块为 fpga16qambsf_top,其主要功能包括:

- 接收外部系统时钟(

sysclkin) - 驱动 DAC 输出接口(

dacdata[9:0]**、dacclk、dac_wr等) - 提供 I²C 接口用于上位机配置(

iicscl*/iic*sda) - 集成 SignalTap 逻辑分析仪用于内部信号调试

系统时钟频率由外部提供,内部通过 clk_div2 模块生成多相位使能信号,用于控制各子模块的同步操作。

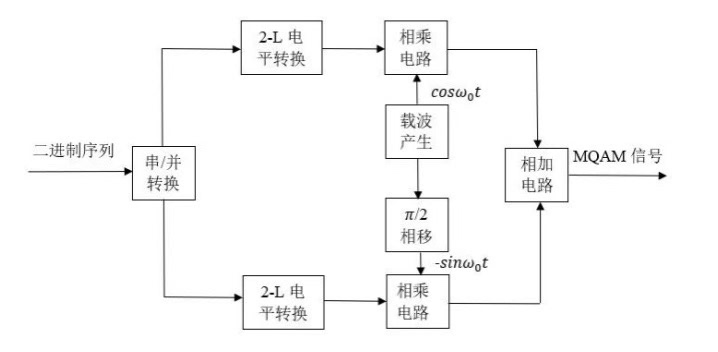

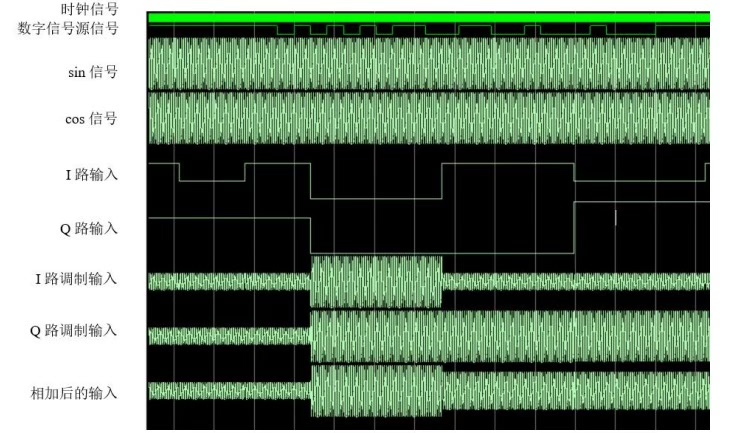

二、调制通路(Modulation Path)

1. 信号源模块

原始数据由 nrzsource2_8 模块生成,该模块输出 PN8 伪随机序列,每 800 个比特为一个周期,默认有效数据长度为 240 比特。输出信号包括:

nrz_out:原始比特流nrz_vid:数据有效标志nrz_fs:帧同步标志(周期起始)

该模块支持通过参数动态调整初始种子与有效长度,便于实验验证。

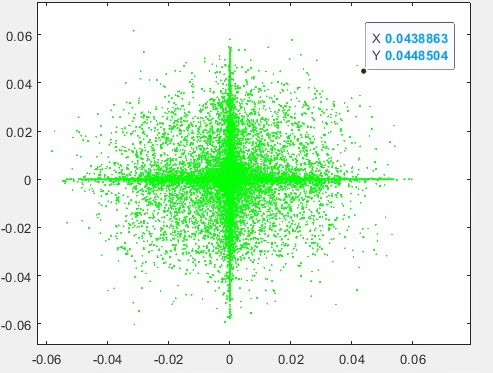

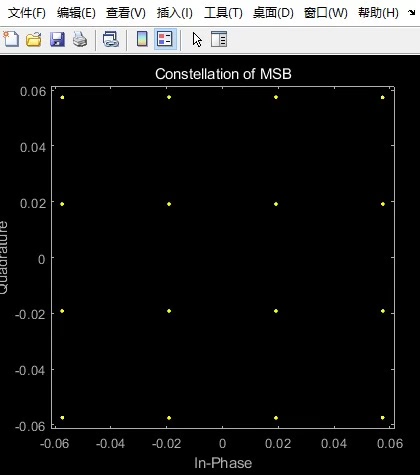

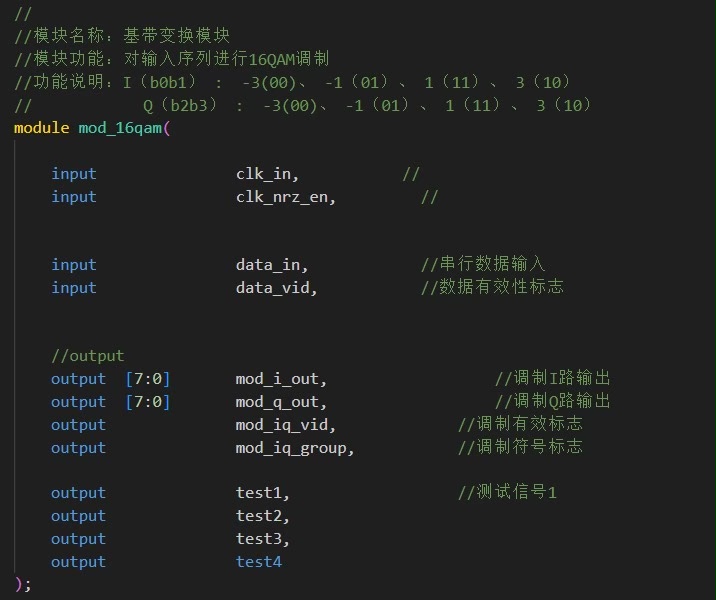

2. 16QAM 映射模块(`mod_16qam`)

该模块接收串行比特流,每 4 比特组成一个符号,映射为 I/Q 两路基带信号:

- I 路对应比特 b0b1,Q 路对应 b2b3

- 映射规则采用 Gray 编码风格,如

00 → -3、01 → -1、11 → +1、10 → +3 - 映射结果通过 ROM 查表 实现(

MODROM16QAM_I/Q),预存了 32 个 10 位宽的 I/Q 幅值 - 输出为 8 位有符号整数(

modiout[7:0]/modqout[7:0]) - 同时输出符号有效标志

modiqvid与分组标志modiqgroup

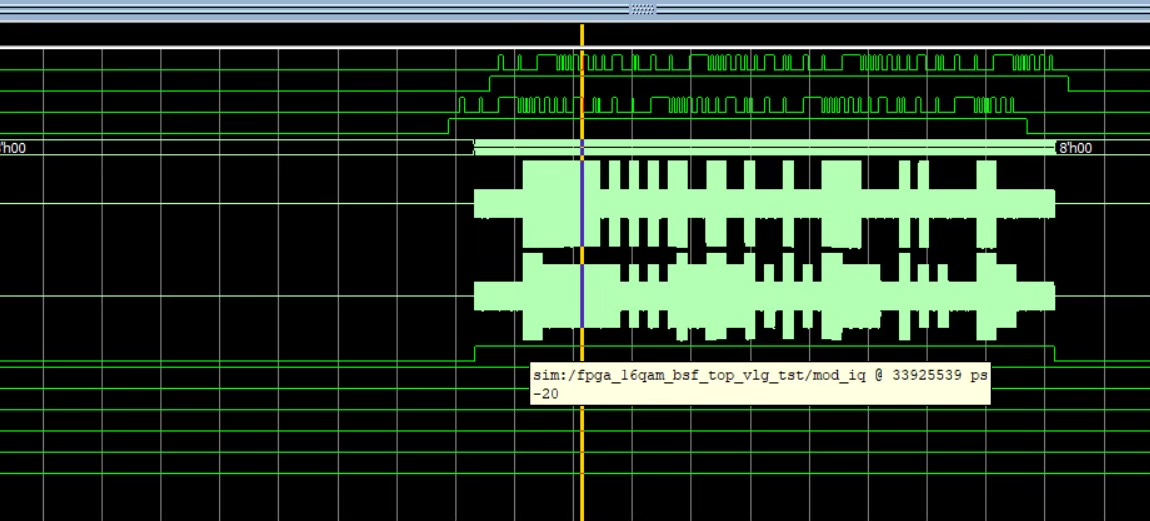

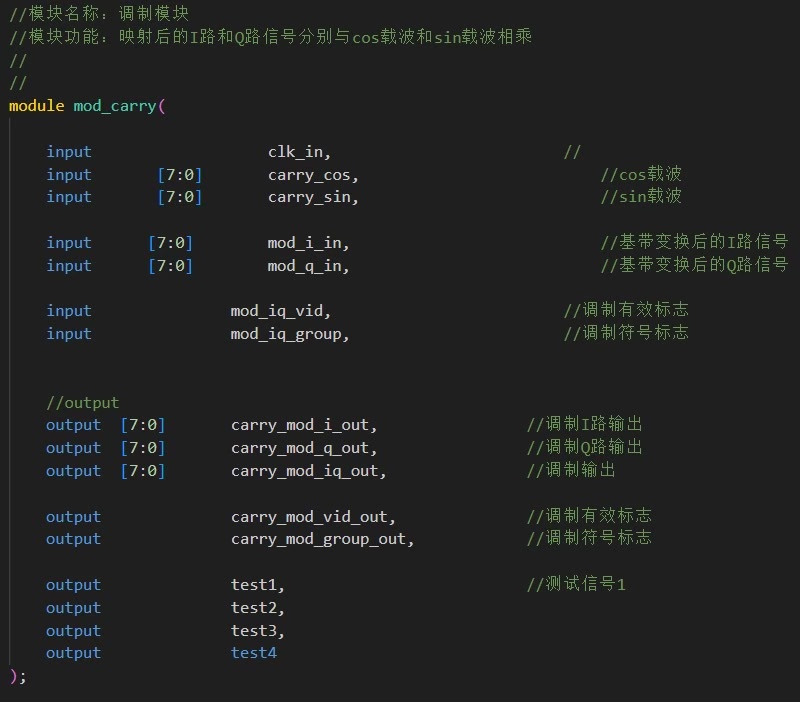

3. 载波调制模块(`mod_carry`)

该模块将基带 I/Q 信号分别与 正交载波(cos/sin) 相乘,完成频谱搬移:

- 载波由

carrier_create模块生成,频率由 ROM 地址递增控制(32 点正弦/余弦表) - 使用 8×8 有符号乘法器 (

lmpmult8x8)实现混频 - I/Q 路混频结果相加,输出已调信号

carrymodiq_out - 所有信号通过寄存器对齐,确保时序一致性

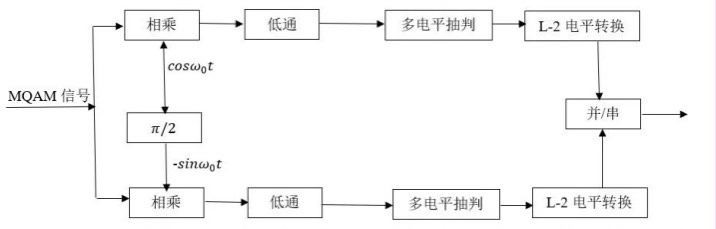

三、解调通路(Demodulation Path)

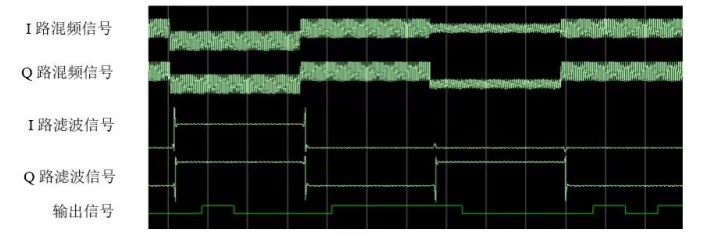

1. 载波解调模块(`demod_carry`)

接收已调信号后,执行相干解调:

- 将输入信号分别与本地 同频同相的 cos/sin 载波 相乘

- 乘法结果经 截位处理 后送入 FIR 低通滤波器

- FIR 滤波器(

fir_demod)为 61 阶对称结构,用于滤除高频分量,恢复基带 I/Q 信号 - 滤波器系数以参数形式硬编码,针对系统带宽优化设计

- 输出为滤波前/后 I/Q 信号,以及对齐后的有效/分组标志

2. 符号判决与解映射模块(`demod_16qam`)

该模块完成从模拟域到数字域的转换:

- 对 I/Q 信号取绝对值并判断幅值区间(阈值 310)

- 根据 I/Q 符号位与幅值大小,还原出原始 4 比特符号

- 通过 并串转换 输出串行比特流

demoddataout - 输出同步标志

demoddatavid与分组标志demoddatagroup

四、信号输出与观测机制

1. DAC 接口模块(`dac_bus_out1`)

- 支持选择 4 组 I/Q 信号对(如原始信号、调制信号、解调信号等)

- 将 8 位数据扩展为 10 位,适配外部 DAC 芯片

- 通过时钟分频生成 DAC 控制时序(

dacclk*、dac*wr、dac_sel) - 输出信号可直接连接示波器观测波形

2. 信号选择机制

- 通过

eightbittodac和onebittodac1模块,支持 8 位数据 与 1 位标志信号 的灵活路由 - 选择逻辑由 I²C 配置寄存器控制,实现动态观测切换

3. I²C 配置接口(`arm_iic_reg_top`)

- 提供 10 个 8 位寄存器,用于上位机配置

- 可设置信号源类型、观测通道、数据长度等参数

- 支持实时交互,便于实验调试

五、调试与验证支持

- 系统集成 SignalTap II 逻辑分析仪,采样深度 65536,可实时捕获:

- 调制 I/Q 输出

- 解调 I/Q 输入

- 符号判决中间变量

- 原始与解调比特流

- 所有关键信号均通过

setinstanceassignment绑定至调试节点 - 支持触发条件配置,便于定位特定事件

六、总结

本 16QAM 调制解调系统完整实现了从比特流到射频等效信号、再还原回比特流的全过程,具备以下特点:

- 模块化设计:各功能单元解耦清晰,便于扩展与替换

- 硬件友好:大量使用 ROM 查表与定点运算,适合 FPGA 实现

- 教学友好:支持多种观测点与配置选项,适合通信原理实验

- 可调试性强:集成逻辑分析仪与 DAC 输出,便于信号验证

该系统可作为数字通信系统 FPGA 实现的典型范例,适用于高校实验、科研验证或嵌入式通信模块开发。