1、vivado 2019.2版本以后删除了xilinx sdk,采用vitis替代,但这个vitis开发linux程序真的太费劲儿了,我今天来记录一下。

2、平台创建

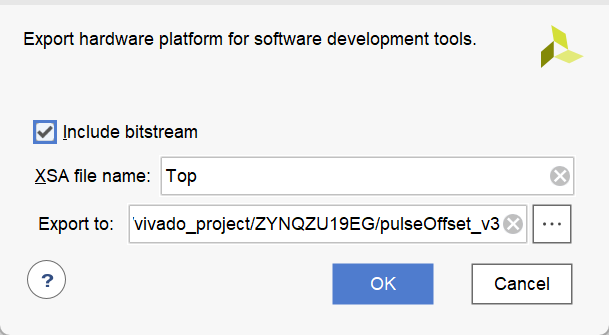

(1)在vivado 2019.2中导出包含bit的.xsa文件

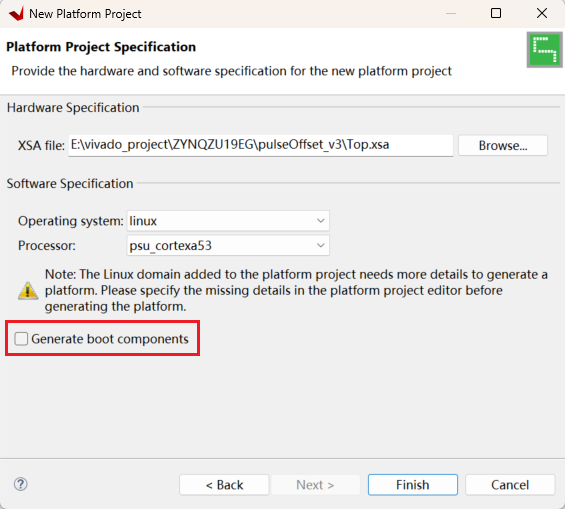

(2)在vitis中基于xsa创建平台,取消勾选这个启动组件

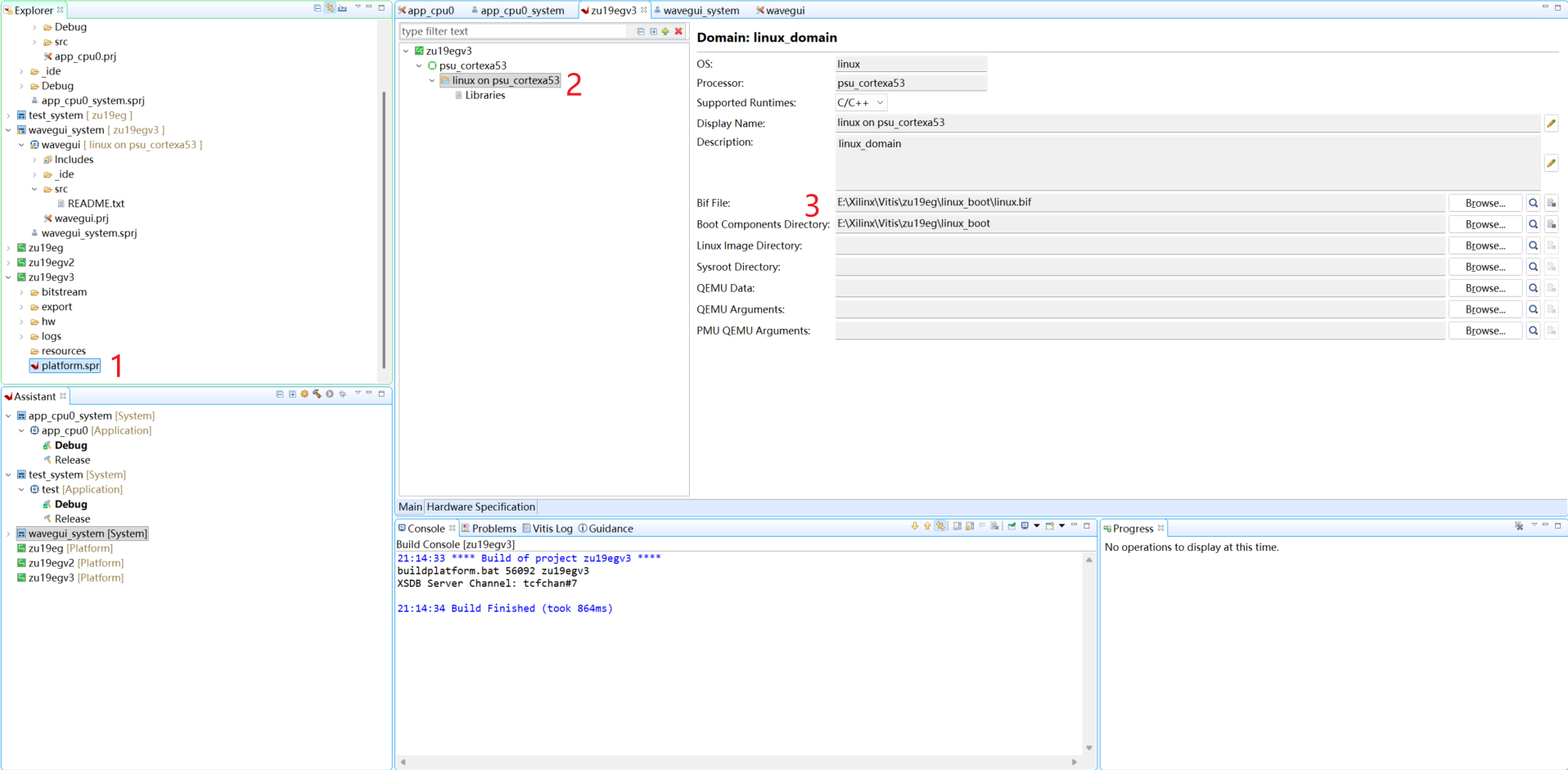

(3)生成平台后,依据一下步骤点开

(4)生成bif file以及boot components directory

首先,将petalinux下生成的<project>/images/linux 这一整个文件夹,移动到你的windows系统(不能有中文名),并将linux文件夹重命名为linux_boot,在linux_boot文件夹下新建文件"linux.bif"写入以下内容

bash

//arch = zynqmp; split = false; format = BIN

the_ROM_image:

{

[bootloader, destination_cpu = a53-0]<fsbl.elf>

<pmufw.elf>

<bl31.elf>

<system.dtb>

<u-boot.elf>

}如果是7000系列的zynq,则写入以下内容

bash

//arch = zynq; split = false; format = BIN

the_ROM_image:

{

[bootloader] zynq_fsbl.elf

system.dtb

u-boot.elf

}(5)boot components directory就是你的linux_boot文件夹路径

(6)bif file就是你刚刚写的linux.bif文件路径

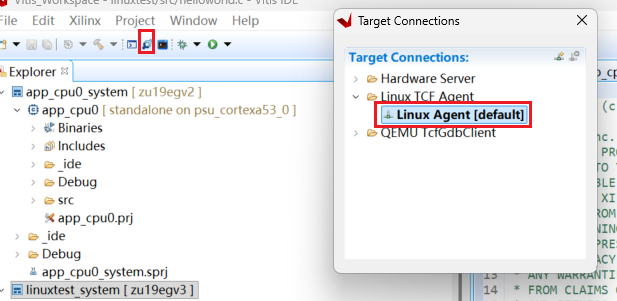

3、linux的TCF在哪里设置?

藏得太深了,真服了