从其他AI转载

"创建一个 PCIe Gen5 链路训练和状态机 (LTSSM) 过程的技术工程流程图。重点关注物理层。包括以下方框:检测、轮询、配置、L0 (2.5 GT/s)、恢复(速度更改为 32 GT/s)和均衡(阶段 0-3)。使用箭头显示转换流程。添加"排序集合 (TS1/TS2)"、"32 GT/s 速度协商"和"128b/130b 编码"的标签。样式:干净、专业、工业原理图,带有白色背景和清晰的蓝色/黑色线条。"

针对提到的每个阶段:检测、轮询、配置、L0 (2.5 GT/s)、恢复(速度更改为 32 GT/s)和均衡(阶段 0-3),都请继续按照上面要求,再进一步深入细致的绘制,可以绘制尽可能多的图片,以方便我这个新手学习。图片中文字修改成中文.

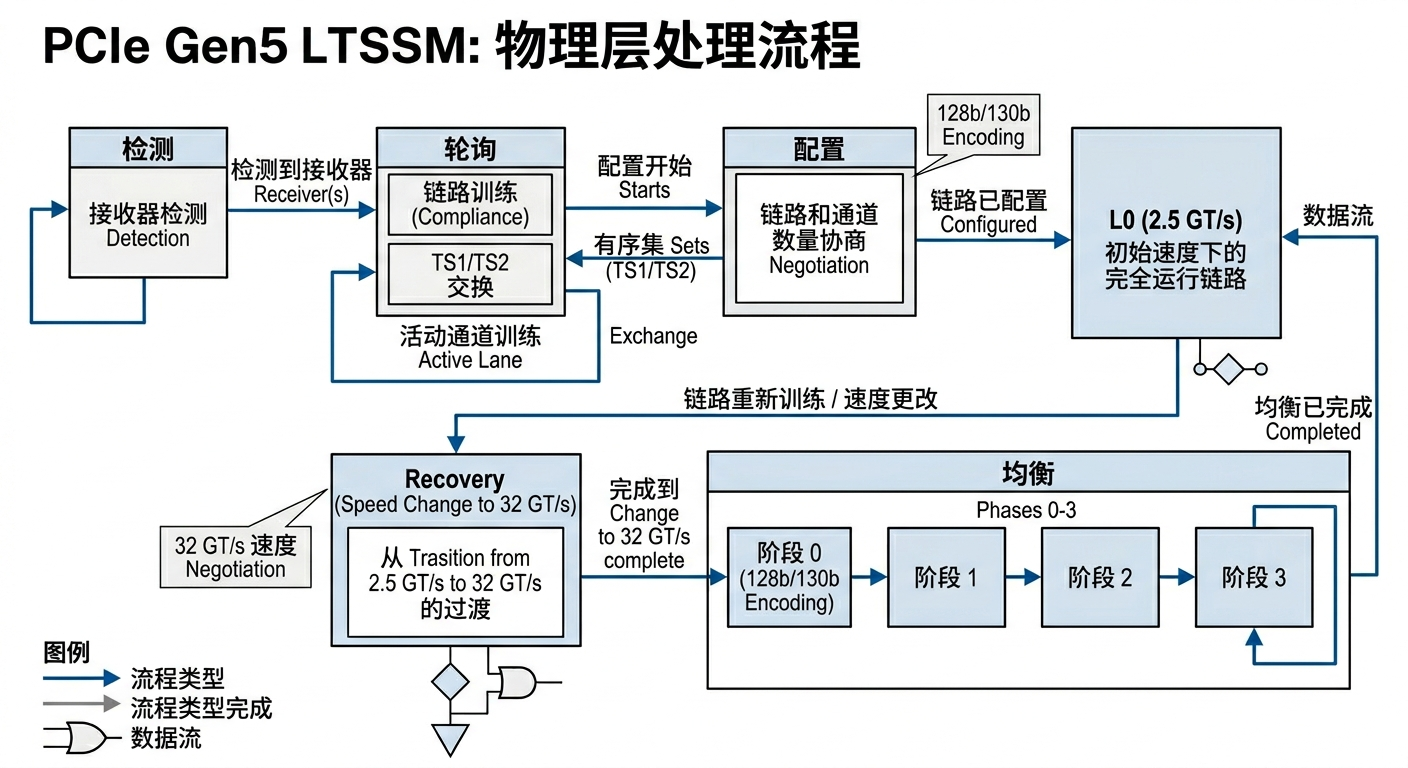

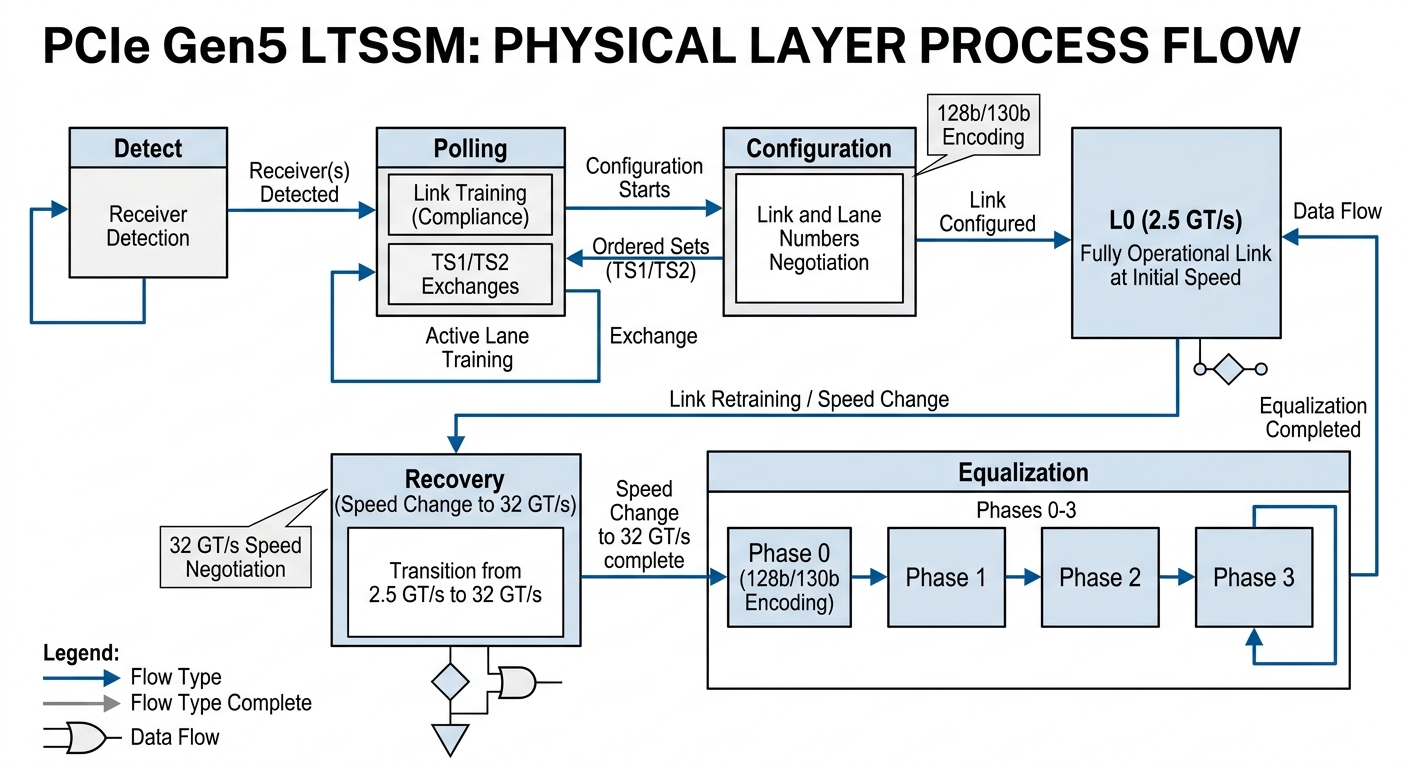

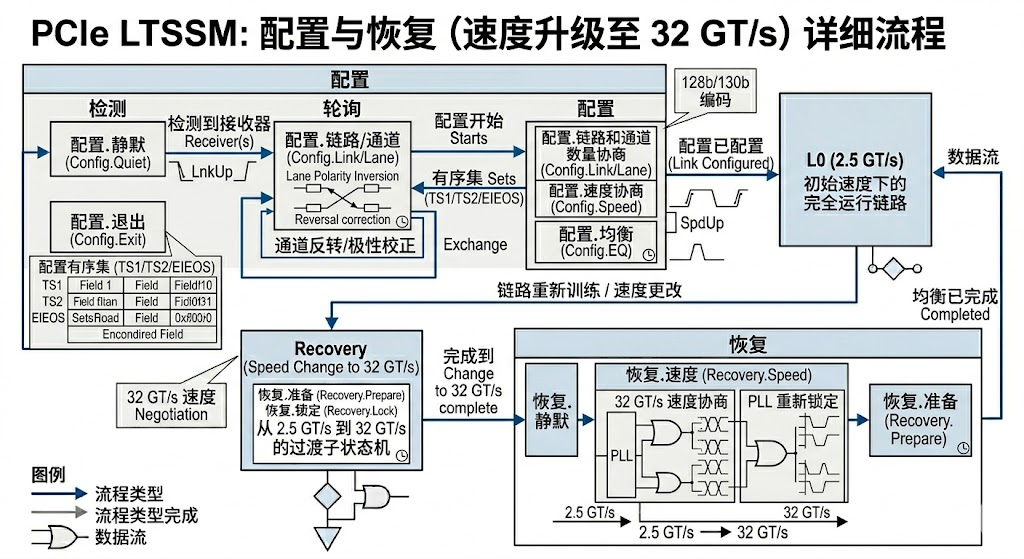

图表 1 说明:总体深度 LTSSM 流程图

-

新的深度: 此图不仅展示了主要状态,还深入到了子状态级。例如,"配置"阶段现在明确显示了链路、通道和速度协商的内部子状态。

-

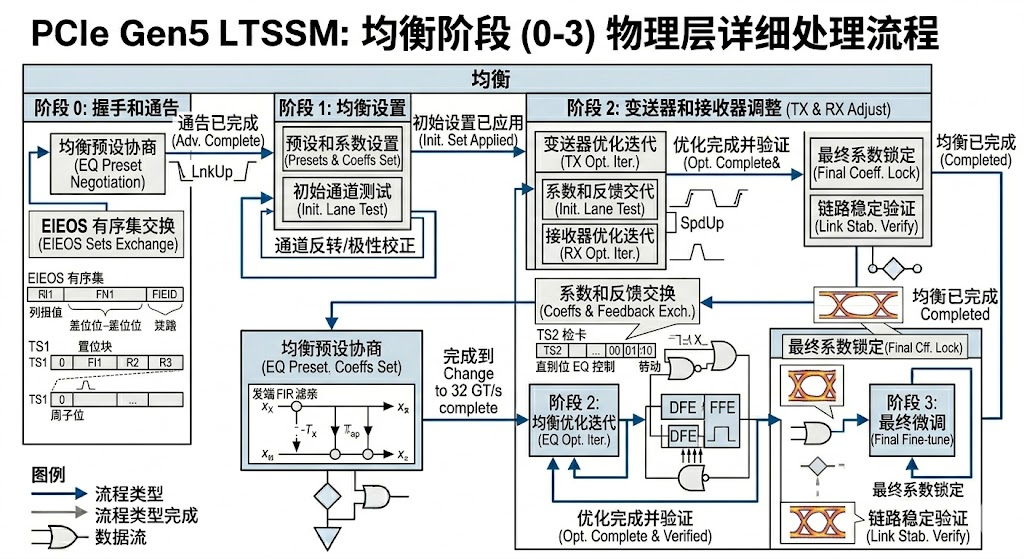

详细的均衡: 均衡过程(Phase 0-3)不再是简单的方框,而是被拆分为具有特定功能的子步骤,如"预设和系数设置"、"变送器调整"和"最终微调"。

-

全中文: 所有的标签、状态名称和过渡描述都已翻译成清晰的技术中文。

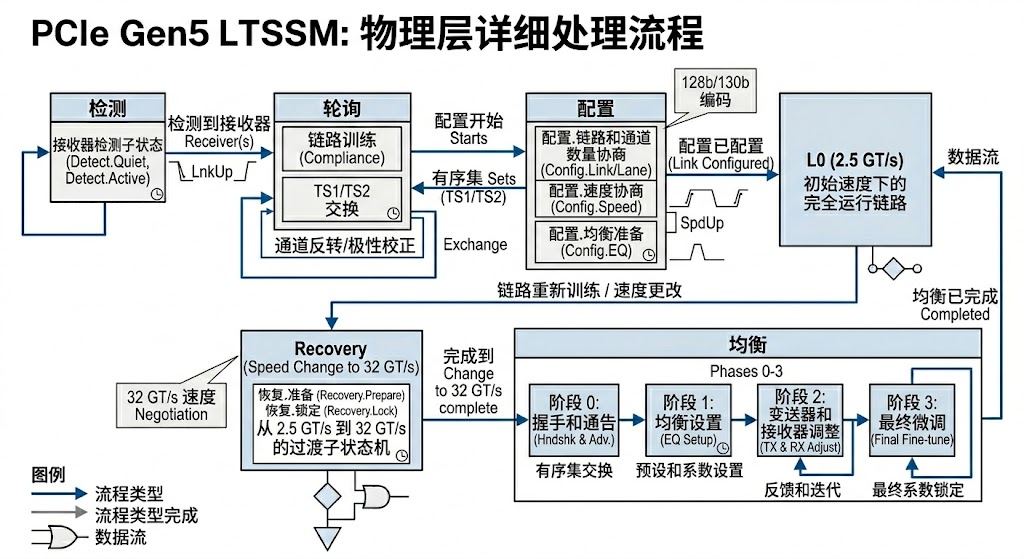

第一部分:总体深度 LTSSM 流程图

这个图表扩展了您最初的要求,将关键阶段(如配置、恢复、均衡)细分为其内部子状态。

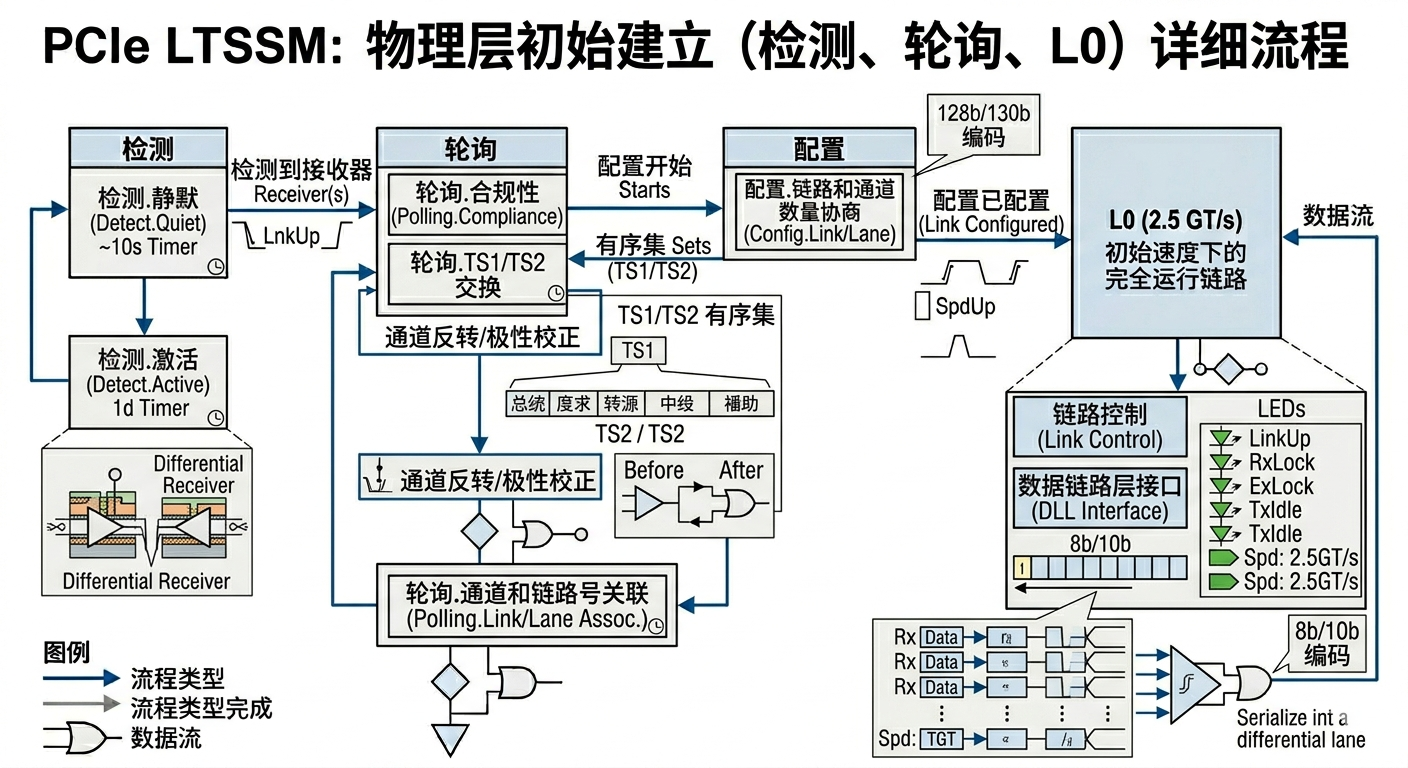

2.1 检测、轮询和 L0 (2.5 GT/s) 阶段的详细信息

此图表侧重于链路建立的初始阶段,直到达到初始的 2.5 GT/s 运行速度。

图表 2 说明:初始链路建立详细信息

-

子状态拆解: "检测"和"轮询"被拆分为其内部子状态(如:静默、激活、合规性、TS1/TS2 交换)。

-

有序集结构: 图中包含了 TS1/TS2 报文结构的放大视图,展示了高速链路如何通过这些有序集进行握手。

-

8b/10b 编码: 由于 L0 阶段初始速度为 2.5 GT/s,图中明确标注了此时使用的是 8b/10b 编码。

-

状态标志: 增加了"LinkUp"和"RxLock"等状态标志,让您直观地看到每个子步骤何时完成。

2.2 配置和恢复(速度更改为 32 GT/s)阶段的详细信息

此图表重点关注从 2.5 GT/s 升级到 32 GT/s (Gen5) 的过程。

图表 3 说明:配置与恢复(速度升级)阶段详细信息

-

配置的全面子状态: "配置"阶段现在明确显示了链路、通道、速度和均衡准备的子状态级流程。

-

速度升级逻辑: "恢复"阶段被细分为准备、锁定、速度更改和重新均衡的子状态机。图表特别强调了 32 GT/s 的速度协商。

-

编码转换: 图中明确标注,随着速度升级,将从 8b/10b 编码转换为更高效的 128b/130b 编码。

-

触发条件: 增加了"速度更改请求"和"PLL 重新锁定"等触发和锁定状态。

2.3 均衡(Phase 0-3)阶段的详细信息

此图表提供了 Phase 0 至 Phase 3 的分步细化,这是确保 PCIe Gen5 高速信号质量的关键过程。

图表 4 说明:均衡阶段(0-3)详细流程

-

分步细化: Phase 0 至 Phase 3 的 generic 方框被拆分为具有特定功能的子步骤,清晰展示了均衡过程的进展。

-

均衡功能: 图中包含了各阶段功能的详细描述,如 Phase 1 的"预设和系数设置"和 Phase 3 的"最终微调"。

-

均衡迭代: Phase 2 和 Phase 3 的循环路径被标记为"均衡优化迭代",表明它们是需要进行变送器和接收器调整的重复过程。

-

有序集交换: Phase 0 中特别强调了 EIEOS(电气空闲退出有序集)的交换。

通过这套全中文、由易到难的图表,您应该能对 PCIe Gen5 的 LTSSM 物理层流程有一个深入、系统的理解。祝您学习顺利!