本博文主要交流设计思路,在本博客已给出相关博文约190篇,希望对初学者有用。 注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。

为了便于产生激励及控制信号,同时便于测试过程的分析,使用 Vitis2022.2 开发套件进行软件测试平台的搭建。

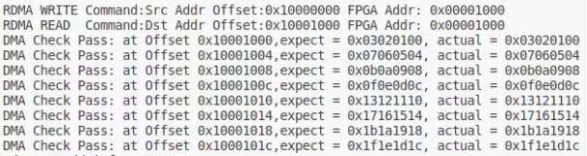

在进行原语功能测试后,进行 DMA 功能数据正确性校验。在数据正确性校验过程中,将对数据流向为 FPGA 至远程主机与远程主机至 FPGA 分别进行测试。由于波形图不便展示具体的数据与地址对应关系,这里使用打印信息进行展示,分别如图3 和图 4所示。

图3 DMA 功能测试 FPGA 至远程主机打印信息图

图4 DMA 功能测试远程主机至 FPGA 打印信息图

根据波形图和打印信息,可以看出 RoCE v2 高速数据传输系统能够正确识别并执行用户指令,同时对 RoCE v2 数据包进行正确地接收与发送。此外,DMA 功能测试对比结果打印信息表明数据在 DMA 搬运前后一致,符合设计预期,同时也进一步证明了之前谈到的队列管理及连接建立过程的正确性。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望