本文档聚焦 Calibre nmLVS 的器件归约功能 ,详细阐述其核心逻辑、归约顺序、各类器件的归约规则(条件、控制语句、属性计算)及高级配置(容差、自定义程序)。器件归约的核心目的是将版图与源网表中一组电气上等价的器件 (如并行 / 串联的 MOS 管、电阻)归约为单个虚拟器件,解决 "单示意图器件对应多版图实现器件" 的对比场景,提升 LVS 对比的效率与准确性。

一、器件归约概述

Calibre nmLVS 会在内部对版图和源文件中的器件组进行归约。每个器件组由一个单独的虚拟器件表示。归约完成后,电路将基于这些虚拟器件进行对比。器件归约可处理多种场景,例如,原理图中的单个器件在版图中由多个并联或串联的器件组实现。

本节描述特定于各器件分组的器件归约行为、如何指定器件归约的容差级别,以及如何创建程序来定义器件归约过程中的计算方式。

以下是一些需要注意的问题:

-

初始对应点:初始对应点会阻止顶层单元中的串联和并联归约。对于 LVS-H 模式,初始对应点不会影响底层单元的器件归约。

-

端口 :对于串联器件归约,与单元端口的连接会中断串联链。这会影响顶层单元和分层单元(hcell)中的实例,但前提是该端口未被移除(例如平凡端口------ 未连接到任何器件或设计中更高层级网络的端口 ------ 会被移除)。

-

过滤:器件过滤在归约之后执行。

-

执行顺序:器件归约在电路变换之后、电路对比阶段之前执行。

1. 核心定义与作用

-

定义 :LVS 在电路变换后、对比阶段前 ,对版图和源网表中的器件组进行归约,用单个虚拟器件代表一组电气等价的器件,基于虚拟器件进行对比。

-

典型场景:示意图中一个宽长比为 W/L 的 MOS 管,在版图中由多个小 MOS 管并行实现;示意图中一个大电阻,在版图中由多个电阻串联实现。

-

关键价值 :避免因 "物理实现的器件拆分" 导致不必要的 LVS 差异,确保对比的是电气功能等价性而非物理器件数量。

- 整体规则与限制

(1)归约顺序

-

默认归约顺序:先串联 → 后并行 → 再串联 → 再并行,交替执行直到无法进一步归约。

-

优先级控制:通过

LVS Reduction Priority语句,可指定在串并行二选一的歧义拓扑中(如两个电阻一端浮空),优先执行并行 或串联归约。

(2)关键限制

-

初始对应点 :顶层单元的初始对应点(同名网、实例、端口)会阻止其所在的串并行结构归约;分层 LVS(LVS-H)中,底层单元的初始对应点不影响归约。

-

端口影响 :单元端口会打断串联结构(若端口未被移除,如无意义端口),顶层单元和 hcell 中的实例均受此影响。

-

执行顺序 :器件归约 先于 器件过滤(Filtering)执行,即先归约再过滤未使用器件。

(3)通用器件归约

-

对于用户定义器件 或非默认归约的内置器件,可通过

LVS Reduce语句实现通用归约。 -

支持单元特定归约 :通过

LVS Reduce CELL LIST选项,仅在指定单元中执行归约。

二、核心器件归约规则

2.1 并联与串联器件归约

在对器件进行归约时,Calibre nmLVS 会先归约串联结构,再归约并联结构,随后重复串联、并联的归约流程,直至所有器件完成归约。

对于既可进行串联归约也可进行并联归约的器件配置,可通过 LVS Reduction Priority 规范语句控制执行的归约类型。该语句允许用户指定:当某一器件配置同时支持两种归约方式时,优先执行并联归约还是串联归约。

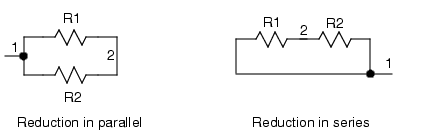

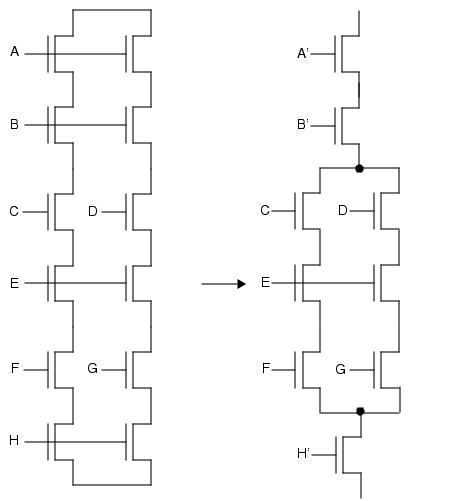

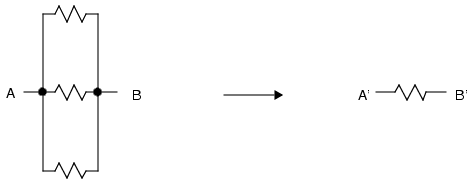

例如,某一器件配置包含两个并联的电阻,且其中一个引脚悬空,该结构既可以按照图 1 所示的方式,在网络 1 和网络 2 之间进行并联归约,也可以通过引入内部网络 2 进行串联归约。

图 1. 并联和串联器件归约

通常,当满足以下条件时,两个并联器件也可进行串联归约:

- 构成并联连接的两个引脚可互相交换。

- 构成并联连接的两个引脚不能与其他任何引脚交换。

- 连接到并联器件的网络中,至少有一个网络无其他连接。

注意 根据未使用器件的过滤选项设置,若某组器件通过一种归约方式归约后被判定为未使用,而通过另一种方式归约后仍被使用,则该器件对可能会被过滤。在上述示例中,若指定 LVS Filter Unused Option RB ,则电阻并联归约后会被视为未使用;若指定 LVS Filter Unused Option RC,则电阻串联归约后会被视为未使用。

若 LVS Reduction Priority 算法无法通过指定的方式对某组器件进行归约,则这些器件会被视为独立器件,不执行归约。

2.2 通用器件归约

Calibre nmLVS 可通过 LVS Reduce 语句,对用户定义的通用器件或内置通用器件进行归约。

通过 LVS Reduce CELL LIST 选项,可将通用器件归约设置为单元专属模式。启用该选项后,仅会在指定的单元中对指定器件执行归约。

2.3 并联 MOS 晶体管归约

在对内置 MOS 器件进行比较时,并联 MOS 晶体管的归约默认启用。LVS Reduce Parallel MOS 规范语句用于控制并联 MOS 晶体管的归约功能。

内置 MOS 晶体管包括以下器件类型:MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD,以及通过 LVS Device Type 规范语句指定的等效类型(详见表 13-3)。归约要求:组内所有晶体管必须具有相同的器件类型、可选子类型、引脚数量和引脚名称;所有栅极(Gate)、源极(Source)、漏极(Drain)引脚以及可选引脚,必须分别连接到相同的网络(即呈并联状态)。

对于 MN、MP、ME、MD、M 及等效器件,其源极和漏极连接可互换。若可选引脚被指定为逻辑等效,也可进行互换。引脚互换的具体指定方法请参见 "引脚互换" 章节。

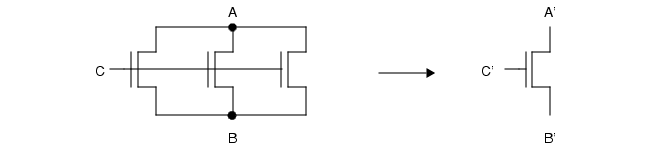

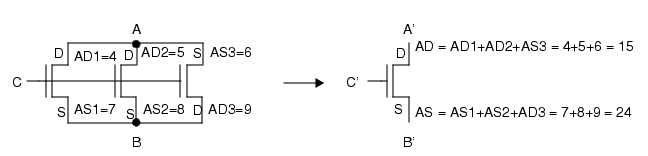

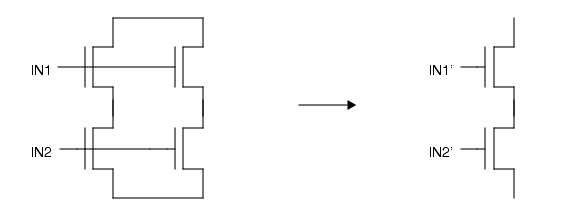

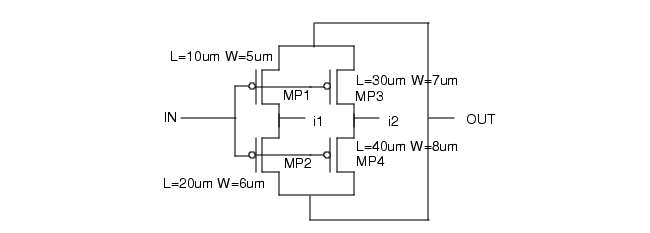

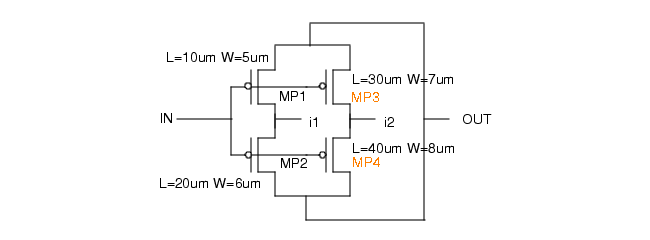

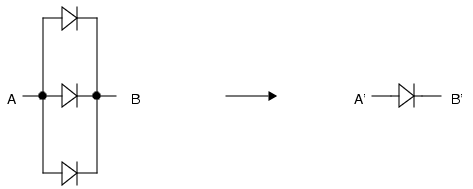

图 2展示了并联 MOS 晶体管归约的示例。 图2. 并联 MOS 晶体管归约

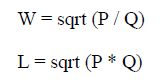

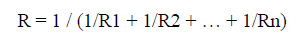

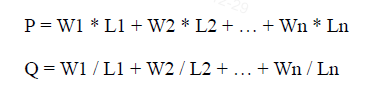

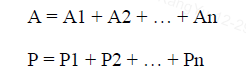

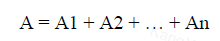

默认情况下,归约后晶体管的等效宽度(W)和长度(L)按以下公式计算:

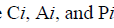

分别为第 i 个晶体管的宽度和长度。

分别为第 i 个晶体管的宽度和长度。

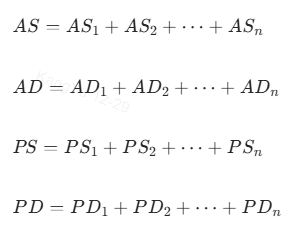

并联 MOS 器件归约还会通过默认的等效属性计算方式,处理源极面积(AS)、漏极面积(AD)、源极周长(PS)和漏极周长(PD)的等效值。计算过程会考虑源极和漏极引脚可能的互换情况。在标准场景下(所有源极引脚互连、所有漏极引脚互连),计算公式如下:

若部分晶体管的源极和漏极引脚发生互换,则 AS 与 AD、PS 与 PD 的值可互换。Calibre nmLVS 会随机确定归约后器件的哪个引脚为源极、哪个为漏极,但属性计算会与该判定保持一致。示例见图 3。

图 3. 带引脚互换的等效 AS/AD 计算

等效属性值会在版图和源文件中同时计算。若使用默认的等效属性计算方式(即未在 LVS Reduce Parallel MOS 语句中自定义等效属性计算逻辑),则在网表中必须使用内置属性名 "w" 、"l" 、"as" 、"ad" 、"ps" 、"pd" 分别计算等效宽度、长度、源极面积、漏极面积、源极周长和漏极周长,除非在 "内置属性分类" 章节(第 481 页)讨论的 Trace Property 语句中另有指定。

对于几何版图,MOS 器件默认仅计算 W 和 L;但用户可通过在 MOS Device 语句中指定自定义属性计算逻辑,来计算任意器件属性。之后,LVS Reduce Parallel MOS 语句应根据需要,通过默认方式或自定义等效属性计算逻辑,为归约后的器件计算对应的等效属性。

若在等效属性计算程序中计算 NRS 和 NRD 属性,可通过 LVS Builtin MOS NRD_NRS 规范语句控制这些属性是否可互换。

归约不匹配的器件

当请求执行并联 MOS 晶体管归约时,Calibre nmLVS 会验证源文件中的每个并联 MOS 晶体管组,是否与版图中具有相同器件数量的并联 MOS 晶体管组对应。若不对应,工具会在 LVS 报告中发出警告。

此检查仅适用于格式规范的 MOS 晶体管,具体为:器件类型为 MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD,或通过 LVS Device Type 语句指定的等效器件,且至少具有三个引脚,引脚名称符合表 13-5 中的标准命名。

在源文件中设置并联 MOS 晶体管组,可确保版图由指定数量的晶体管构成。若无需此要求,应在源文件中使用单个晶体管。

可通过 LVS Report Option F 禁用此检查。

2.4 串联 MOS 晶体管归约

在对内置 MOS 器件进行比较时,串联 MOS 晶体管的归约默认禁用。LVS Reduce Series MOS 规范语句用于控制串联 MOS 晶体管的归约功能。

内置 MOS 晶体管包括以下器件类型:MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD,以及通过 LVS Device Type 规范语句指定的等效类型(详见表 13-3)。归约要求:组内所有晶体管必须具有相同的器件类型、可选子类型、引脚数量和引脚名称;所有源极和漏极引脚必须串联连接;栅极、体极(Bulk)和可选引脚必须分别连接到相同的网络(即呈并联状态)。

对于 MN、MP、ME、MD、M 及等效器件,源极和漏极等效,极性不影响归约。

对于 LDDN、LDDP、LDDE、LDDD、LDD 及等效器件,源极和漏极必须在串联结构中交替连接;若出现源极 - 源极或漏极 - 漏极连接,该位置的串联链会中断。

对于所有晶体管类型,若体极和可选引脚被指定为逻辑等效,则可互换。

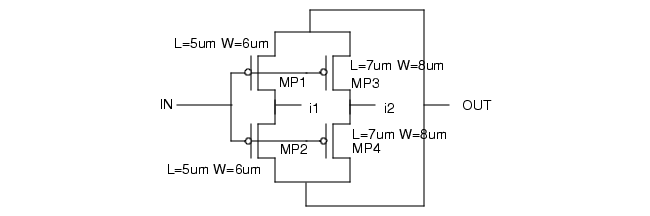

图 3 展示了串联 MOS 晶体管归约的示例。 图3 串联 MOS 晶体管归约

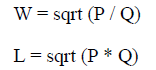

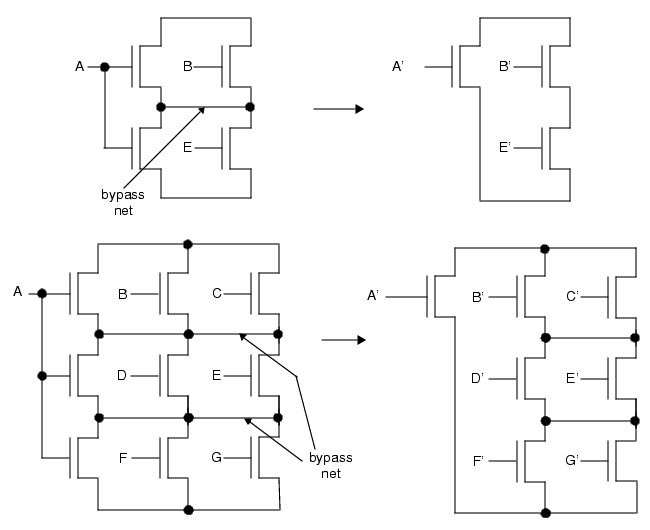

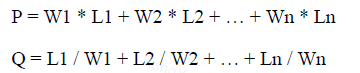

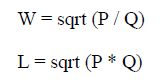

默认情况下,归约后晶体管的等效宽度(W)和长度(L)按以下公式计算:

分别为第 i 个晶体管的宽度和长度。

分别为第 i 个晶体管的宽度和长度。

默认情况下,串联 MOS 器件归约不计算串联 MOS 晶体管的源极面积(AS)、漏极面积(AD)、源极周长(PS)和漏极周长(PD)的等效值。

等效属性值会在版图和源文件中同时计算。若使用默认的等效属性计算方式(即未在 LVS Reduce Series MOS 语句中自定义等效属性计算逻辑),则在网表中必须使用内置属性名 "w" 和 "l" 分别计算等效宽度和长度,除非在 "内置属性分类" 章节(讨论的 Trace Property 语句中另有指定。

对于几何版图,MOS 器件默认仅计算 W 和 L;但用户可通过在 MOS Device 语句中指定自定义属性计算逻辑,来计算任意器件属性。之后,LVS Reduce Series MOS 语句应根据需要,通过默认方式或自定义等效属性计算逻辑,为归约后的器件计算对应的等效属性。

2.5 半串联 MOS 晶体管归约

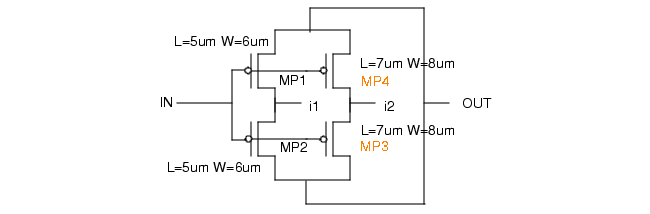

半串联 MOS 晶体管的归约默认禁用。LVS Reduce Semi Series MOS 规范语句用于控制半串联 MOS 晶体管的归约功能。

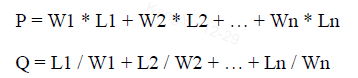

内置 MOS 晶体管包括以下器件类型:MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD,以及通过 LVS Device Type 规范语句指定的等效类型(详见表 13-3)。归约要求:组内所有晶体管必须具有相同的器件类型、可选子类型、引脚数量和引脚名称;所有源极和漏极引脚必须串联连接,并带有旁路网络(如图4所示);栅极、体极和可选引脚必须分别连接到相同的网络(即呈并联状态)。

对于 MN、MP、ME、MD、M 及等效器件,源极和漏极等效,极性不影响归约。

对于 LDDN、LDDP、LDDE、LDDD、LDD 及等效器件,源极和漏极必须在串联结构中交替连接;若出现源极 - 源极或漏极 - 漏极连接,该位置的串联链会中断。

对于所有晶体管类型,若体极和可选引脚被指定为逻辑等效,则可互换。

图 4表明,旁路网络不得连接到串并联结构对应 "行" 之外的任何器件。

图 4. 半串联 MOS 归约

半串联 MOS 归约独立于常规串联 MOS 归约,可单独执行其中一种,也可两种同时执行。

默认情况下,归约后晶体管的宽度(W)和长度(L)按以下公式计算:

分别为第 i 个晶体管的宽度和长度。

分别为第 i 个晶体管的宽度和长度。

默认情况下,半串联 MOS 器件归约不计算半串联 MOS 晶体管的源极面积(AS)、漏极面积(AD)、源极周长(PS)和漏极周长(PD)的等效值。

等效属性值会在版图和源文件中同时计算。若使用默认的等效属性计算方式(即未在 LVS Reduce Semi Series MOS 语句中自定义等效属性计算逻辑),则在网表中必须使用内置属性名 "w" 和 "l" 分别计算等效宽度和长度,除非在 "内置属性分类" 章节讨论的 Trace Property 语句中另有指定。

对于几何版图,MOS 器件默认仅计算 W 和 L;但用户可通过在 MOS Device 语句中指定自定义属性计算逻辑,来计算任意器件属性。之后,LVS Reduce Semi Series MOS 语句应根据需要,通过默认方式或自定义等效属性计算逻辑,为归约后的器件计算对应的等效属性。

2.6 分裂栅归约

在对内置 MOS 器件进行比较时,分裂栅 MOS 结构的归约默认启用。分裂栅归约由 LVS Reduce Split Gates 和 LVS Short Equivalent Nodes 规范语句控制。

在许多情况下,规则文件中首选的配置是 LVS Short Equivalent Nodes SPLIT (该配置要求 LVS Reduce Split Gates NO)。这是因为该配置支持器件模型相关的归约,而分裂栅归约不具备此能力。

注意分裂栅归约意味着执行并联 MOS 晶体管归约,即使未明确请求并联 MOS 晶体管归约。

若指定执行分裂栅归约,则分裂栅结构会被归约为单栅结构。分裂栅结构由两组或多组 MOS 晶体管串组成(器件类型包括 MN、MP、ME、MD、M、LDDN、LDDP、LDDE、LDDD、LDD,以及通过 LVS Device Type 规范语句指定的等效类型,详见表1)。

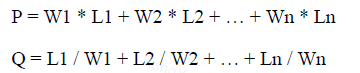

每组晶体管串内部呈串联连接,且各晶体管串的两端均连接到公共网络。每组晶体管串中对应位置晶体管的栅极引脚共享同一网络,如图 5 所示。原始结构中每组对应位置的晶体管,在归约后的结构中由一个晶体管表示。

当启用逻辑门识别(Logic Gate Recognition)时,不同晶体管串中对应位置晶体管的顺序可以不同(需遵循 LVS Reduce Split Gates SAME ORDER 选项)。当禁用逻辑门识别时,对应位置晶体管的顺序必须相同(需遵循 LVS Recognize Gates WITHIN TOLERANCE 选项)。若分裂栅结构违反了任何相关 LVS Recognize Gates Tolerance 语句中的容差要求,则整个分裂栅结构会强制启用 LVS Reduce Split Gates SAME ORDER 选项,即使未明确指定该选项。

通常,分裂栅结构中的所有晶体管必须具有相同的器件类型、引脚数量、引脚名称和引脚互换条件。可通过 LVS Reduce Split Gates MIX TYPES 选项修改此要求。但在每一组被归约的晶体管中(即分裂栅的每一行),子类型必须相同。

例如,在图5 中,每一行的子类型必须相同,不同行的子类型可以不同。若晶体管具有三个以上引脚,则所有可选引脚必须呈并联连接(即分别连接到相同的网络)。

对于 MN、MP、ME、MD、M 及等效器件,源极和漏极引脚可互换。

对于 LDD 类型及等效器件,串联连接必须在一个器件的源极引脚和另一个器件的漏极引脚之间建立。

图 5. 分裂栅归约

若可选引脚被指定为逻辑等效,则可互换。

初始对应点会阻止分裂栅归约;具体而言,若分裂栅结构中的内部网络构成初始对应点,则这些网络不会与其他网络合并。

分裂栅结构中的单个晶体管基于其栅极引脚连接(晶体管引脚名 G)进行匹配。一个设计中分裂栅结构的内部网络,仅基于其相对于结构 "顶部" 和 "底部" 的相对距离,与另一个设计中的对应网络匹配。

所有原始内部网络都会被匹配;因此,一个设计中的多个网络可能会匹配到另一个设计中的单个网络。若两个设计中均存在分裂栅结构,则会从一个设计中每组合并的网络中选择一个代表性网络,并将另一个设计中的对应网络与该代表性网络匹配。

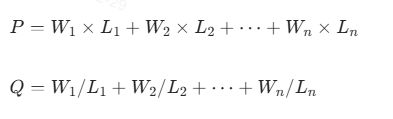

默认情况下,对于每一组被归约为单个晶体管的晶体管组,归约后晶体管的宽度(W)和长度(L)按以下公式计算:

分别为第 i 个晶体管的宽度和长度。

分别为第 i 个晶体管的宽度和长度。

等效宽度和长度值会在版图和源文件中同时计算。若使用默认的等效属性计算方式(即未在 LVS Reduce Split Gates 语句中自定义等效属性计算逻辑),则在网表中必须使用内置属性名 "w" 和 "l" 分别计算等效宽度和长度,除非在 "内置属性分类" 章节讨论的 Trace Property 语句中另有指定。

对于几何版图,MOS 器件默认仅计算 W 和 L;但用户可通过在 MOS Device 语句中指定自定义属性计算逻辑,来计算任意器件属性。之后,LVS Reduce Semi Series MOS 语句应根据需要,通过默认方式或自定义等效属性计算逻辑,为归约后的器件计算对应的等效属性。

2.6.1 串并联分裂栅归约

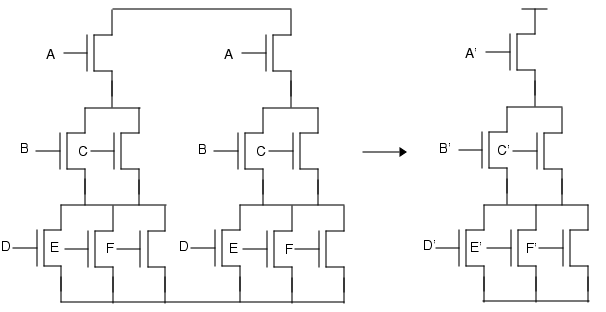

串并联分裂栅归约是常规分裂栅归约的扩展。与常规分裂栅归约的区别在于,该归约还会合并晶体管串中包含的并联结构。

图 16 展示了串并联分裂栅归约。该归约适用于 MOS 器件的串并联结构,要求所有串联结构包含相同数量的并联器件结构。要合并并联结构,需满足以下特征:

- 栅极引脚共享同一网络。

- 具有相同数量的晶体管,且以下属性完全相同:

- 器件类型和子类型

- 引脚数量

- 引脚名称

- 引脚可互换性

若晶体管具有三个以上引脚,则所有可选引脚必须在该行内呈并联连接。在图6中,字母 A-F 表示连接到栅极引脚的网络;标记为相同字母的所有栅极引脚均被视为连接到同一网络。

图 6 串并联分裂栅归约

作为对比,常规分裂栅归约也适用于类似结构,但要求每个并联组内的所有栅极必须短接在一起(即在前述图示中,B 和 C 必须为同一网络,D、E、F 同理)。

若正如图示中所绘制的那样,仅归约两组并联器件,则需满足一些特殊条件。要执行归约,图示中最上方的网络必须至少满足以下条件之一:

- 该网络必须连接到至少一个额外的器件。

- 该网络必须具有用户指定的名称,且为初始对应点。

- 该网络必须连接到单元的引脚。

否则,最上方网络的选择本身存在模糊性,归约将不执行。

串并联分裂栅归约通过 LVS Reduce Split Gates 规范语句的 SP ALSO 选项启用。该语句的其他选项同样适用于串并联分裂栅归约,且效果与常规分裂栅归约相同。对于属性计算(无论是内置还是用户自定义的),以及 LVS Split Gate Ratio 语句,上述规则同样适用。

2.6.2 半分裂栅归约

半分裂栅归约通过 LVS Reduce Split Gates 语句的 SEMI ALSO 选项启用。

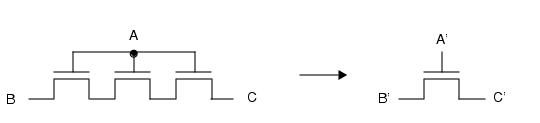

除完全分裂栅外,Calibre nmLVS 还可归约半分裂栅结构。半分裂栅归约与完全分裂栅归约类似,但仅要求结构中的部分栅极引脚共享同一网络。栅极引脚共享的晶体管会被合并,栅极引脚不同的晶体管会保持独立。归约从结构的顶部和底部开始,按水平行进行,只要每行的晶体管栅极引脚共享,归约就会继续。当遇到栅极引脚不共享的行时,归约停止。

图 7 显示,E 行的晶体管未被归约。与完全分裂栅不同,无论是否启用逻辑门识别,半分裂栅中所有 MOS 晶体管串的晶体管顺序必须相同。所有晶体管串必须包含相同数量的晶体管。

图 7. 分裂栅归约示例

2.6.3 输入顺序考量

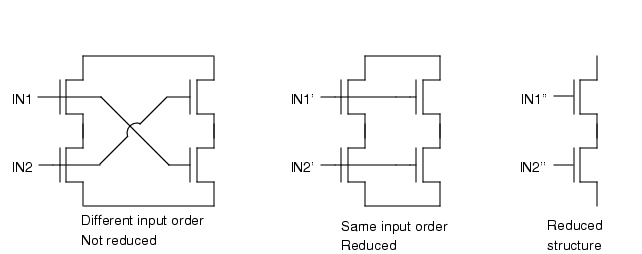

LVS Reduce Split Gates 规范语句的 SAME ORDER 选项指定:仅当构成分裂栅的所有晶体管串的输入顺序相同时,才对分裂栅进行合并。图8 展示了 SAME ORDER 选项的效果。

图 8. SAME ORDER 选项

2.6.4 误差容差

LVS Reduce Split Gates 规范语句的 WITHIN TOLERANCE 选项表明:若分裂结构违反了任何相关 LVS Split Gate Ratio 规范语句中的容差要求,则不对其进行归约。当指定 WITHIN TOLERANCE 时,若分裂栅归约会导致 LVS Split Gate Ratio 差异,则不执行该归约。

2.6.5 混合器件类型

LVS Reduce Split Gates 规范语句的 MIX TYPES 选项指定:分裂栅结构中可包含具有不同器件类型、引脚数量、引脚名称或引脚可互换性的晶体管。但在每一组被归约的晶体管中(即分裂栅的每一行),器件类型、引脚数量、引脚名称、引脚可互换性以及器件子类型仍必须相同。

若分裂栅结构中的任意位置存在具有不同器件类型、引脚数量、引脚名称或引脚可互换性的器件,则整个结构会强制启用 SAME ORDER 选项。

逻辑门识别相关限制

分裂栅归约需遵守以下限制:

-

禁用逻辑门识别(LVS Recognize Gates NONE )会强制分裂栅归约启用 SAME ORDER 选项,即使未明确指定该选项。

-

若分裂栅结构中的任意位置存在具有不同子类型的器件,则整个结构会强制启用 SAME ORDER 选项,除非指定了 LVS Recognize Gates MIX SUBTYPES。

-

若分裂栅结构中的任意位置存在 X+ 器件,则整个结构会强制启用 SAME ORDER 选项,除非指定了 LVS Recognize Gates XALSO。

这些限制的目的均是为了防止出现不确定的结果。若未启用 SAME ORDER 选项,最终归约结构的输入顺序可能继承自构成分裂栅的任意一个原始晶体管串。若归约后的晶体管随后构成逻辑门,这是可接受的(因为逻辑门的输入在逻辑上是等效的)。但当未构成逻辑门时,这可能导致结果不确定,因此设置了上述限制。

2.6.6 模糊拓扑与分裂栅归约

某些器件排列对于分裂栅归约存在模糊性。

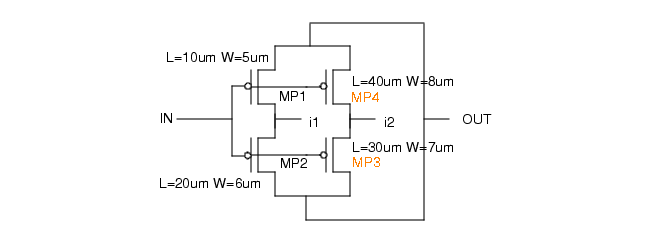

当版图输入数据的顺序与源文件输入数据的顺序不同时(如图 13-12 和图 13-13 中的顺序差异所示),两者的拓扑结构相互模糊。因此,由于不同归约顺序下,具有不同归约前属性值的实例可能会以不同方式关联,导致归约后的属性值可能不同。

请注意,在图示的分裂栅结构中,所有晶体管的栅极引脚均短接到公共网络 IN。此外,结构的顶部和底部网络(分裂栅结构的输出)均短接到公共网络 OUT。

假设规则文件中存在以下规范语句:

LVS REDUCE SPLIT GATES YES

TRACE PROPERTY MP L L

TRACE PROPERTY MP W W在这些条件下,无法无歧义地归约以下结构。

图 9. 版图原理图

图 10 源文件原理图

若将图 13-14 中的源文件输入数据与图 13-12 中的版图输入数据进行归约后比较,则版图和源文件中的归约属性值相同。

图 11替代源文件原理图

前述拓扑结构的模糊性可能导致:当比较图9和图 10 时,LVS 报告错误结果;而当比较图 9 和图 11 时,LVS 报告正确结果。

LVS Reduce Split Gates 会归约所有分裂栅,但会将归约后的属性值设置为 UNKNOWN(未知)。这样,即使在存在模糊性的情况下,无论输入顺序如何,Calibre nmLVS 每次都会报告一致的结果。

图 12 和图 13 是一个例外情况,该情况可通过分裂栅归约处理,且仍能产生一致的归约属性值,尽管两种结构在拓扑上均存在模糊性。此时会应用常规的属性值归约公式,而非将归约实例的属性值指定为 UNKNOWN。

图 13 中最右侧的列相对于图 12 中的同一列进行了垂直反转。但这对将最右侧列器件与最左侧列中的 MP1 和 MP2 相关联时使用的属性值没有影响。

图 12 具有属性值对称性的版图

图13. 具有属性值对称性的源文件

若垂直反转顺序,读出的属性值顺序相同。无论输入数据的顺序如何,图 12 和图 13 的归约方式相同,且产生相同的归约后属性值。

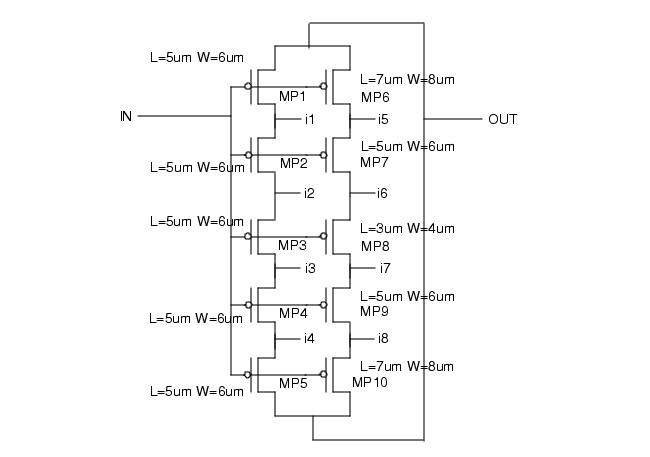

图 14展示了一个更大的示例,包含五个具有相同属性值对称性的器件。该结构会被归约,并将实际属性值写入归约后的器件。

图 14. 具有属性值对称性的输入数据

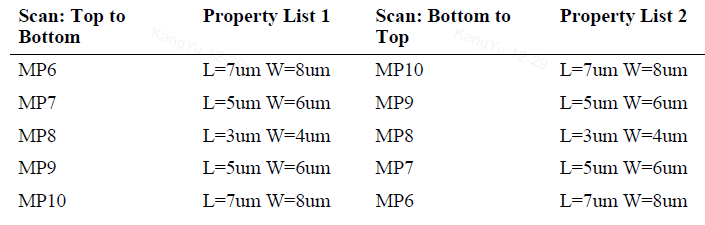

最左侧的列可忽略,因为其所有属性均相同,且器件归约后的实际值也相同。考虑最右侧的列。请注意,无论是从上到下扫描(MP6、MP7、MP8、MP9、MP10)还是从下到上扫描(MP10、MP9、MP8、MP7、MP6),属性值列表均相同。

请注意,属性列表 1 和属性列表 2 完全相同。只要每个器件具有相同的相邻器件,属性值就会产生一致的归约结果。例如,MP7 的相邻器件必须是 MP6 和 MP8。无论列中的器件数量是偶数还是奇数,此类情况都会被检测到。

分裂栅结构中的每一列都会被检查是否满足此条件。若分裂栅结构中的所有列均符合条件,则会正常执行归约,并将有效属性值(而非 UNKNOWN 值)写入归约后的器件。

归约器件的属性值通过常规分裂栅归约公式计算。

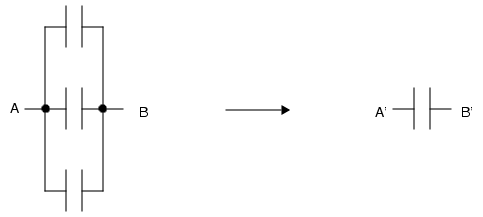

2.6.7 并联电容归约

在对内置电容器进行比较时,并联电容器的归约默认启用。LVS Reduce Parallel Capacitors 规范语句用于控制并联电容器的归约功能。Calibre nmLVS 可将一组并联电容器(器件类型 C,以及通过 LVS Device Type 规范语句指定的等效类型)归约为单个电容器。

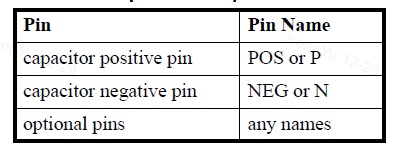

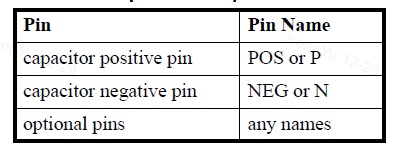

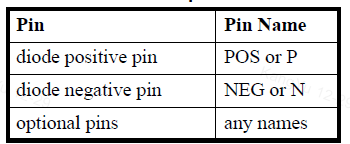

归约要求:电容器必须至少具有两个引脚,引脚名称符合表下表中的标准命名。组内所有电容器必须具有相同的可选器件子类型、引脚数量和引脚名称。所有正极、负极和可选引脚(若有)必须连接到相同的网络。

若正极、负极和可选引脚被指定为逻辑等效,则可互换。

所有可选引脚必须分别连接到相同的网络(即呈并联状态)。

图15. 并联电容器归约

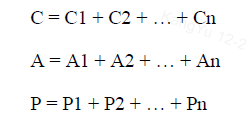

默认情况下,归约后器件的等效电容(C)、面积(A)和周长(P)按以下公式计算:

分别为第 i 个电容器的电容、面积和周长。

分别为第 i 个电容器的电容、面积和周长。

等效电容、面积和周长值会在版图和源文件中同时计算。若使用默认的等效属性计算方式(即未在 LVS Reduce Parallel Capacitors 语句中自定义等效属性计算逻辑),则在网表中必须使用内置属性名 "c" 、"a" 和 "p" 分别计算等效电容、面积和周长,除非在 "内置属性分类" 章节(讨论的 Trace Property 语句中另有指定。

对于几何版图,C 类型器件默认仅计算属性 C;但用户可通过在 电容器 Device 语句中指定自定义属性计算逻辑,来计算任意器件属性。之后,LVS Reduce Parallel Capacitors 语句应根据需要,通过默认方式或自定义等效属性计算逻辑,为归约后的器件计算对应的等效属性。

2.8 串联电容归约

在对内置电容器进行比较时,串联电容器的归约默认启用。LVS Reduce Series Capacitors 规范语句用于控制串联电容器的归约功能。Calibre nmLVS 可将一组串联连接的电容器(器件类型 C,以及通过 LVS Device Type 规范语句指定的等效类型)归约为单个电容器。

归约要求:电容器必须至少具有两个引脚,引脚名称符合下标中的标准命名。组内所有电容器必须具有相同的可选器件子类型、引脚数量和引脚名称。所有正极和负极引脚必须串联连接。

正极和负极引脚必须在串联结构中交替连接;若出现正极 - 正极或负极 - 负极连接,该位置的串联链会中断,除非这些引脚被指定为逻辑等效。所有可选引脚必须分别连接到相同的网络(即呈并联状态)。若可选引脚被指定为逻辑等效,则可互换。

图 16 展示了串联电容器归约的示例。 图 16. 串联电容器归约

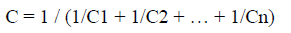

默认情况下,归约后器件的等效电容(C)按以下公式计算:

Ci分别为第 i 个电容器的电容。

等效电容值会在版图和源文件中同时计算。若使用默认的等效属性计算方式(即未在 LVS Reduce Series Capacitors 语句中自定义等效属性计算逻辑),则在网表中必须使用内置属性名 "c" 计算等效电容,除非在 "内置属性分类" 章节讨论的 Trace Property 语句中另有指定。

用户可覆盖默认的等效属性计算方式,并指定其他公式。

对于几何版图,C 类型器件默认仅计算属性 C;但用户可通过在 电容器 Device 语句中指定自定义属性计算逻辑,来计算任意器件属性。之后,LVS Reduce Series Capacitors 语句应根据需要,通过默认方式或自定义等效属性计算逻辑,为归约后的器件计算对应的等效属性。

2.9 并联电阻归约

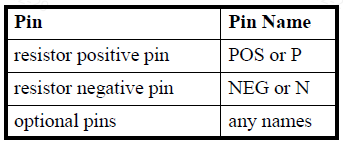

在对内置电阻器进行比较时,并联电阻器的归约默认启用。LVS Reduce Parallel Resistors 规范语句用于控制并联电阻器的归约功能。Calibre nmLVS 可将一组并联电阻器(器件类型 R,以及通过 LVS Device Type 规范语句指定的等效类型)归约为单个电阻器。

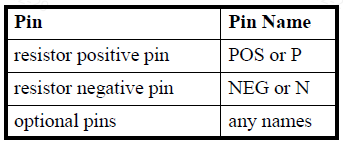

归约要求:电阻器必须至少具有两个引脚,引脚名称符合下表中的标准命名。组内所有电阻器必须具有相同的可选器件子类型、引脚数量和引脚名称。所有正极、负极和可选引脚(若有)必须分别连接到相同的网络。

若正极、负极和可选引脚被指定为逻辑等效,则可互换。所有可选引脚必须分别连接到相同的网络(即呈并联状态)。若可选引脚被指定为逻辑等效,则可互换。逻辑等效的指定方法请参见 "引脚互换" 章节。

图 17展示了并联电阻器归约的示例。 图 17. 并联电阻器归约

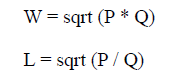

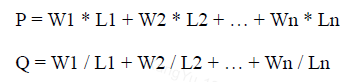

默认情况下,归约后电阻器的电阻值(R)按以下公式计算:

Ri为第 i 个电阻器的电阻值。

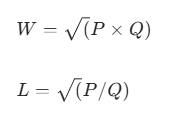

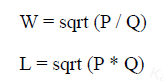

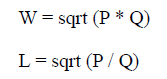

默认情况下,归约后器件的宽度(W)和长度(L)按以下公式计算:

Wi,Li分别为第 i 个电阻器的宽度和长度。

等效电阻、宽度和长度值会在版图和源文件中同时计算。若使用默认的等效属性计算方式(即未在 LVS Reduce Parallel Resistors 语句中自定义等效属性计算逻辑),则在网表中必须使用内置属性名 "r" 、"w" 和 "l" 分别计算等效电阻、宽度和长度,除非在 "内置属性分类" 章节(第 481 页)讨论的 Trace Property 语句中另有指定。

对于几何版图,R 类型器件默认仅计算属性 R;但用户可通过在 电阻器 Device 语句中指定自定义属性计算逻辑,来计算任意器件属性。之后,LVS Reduce Parallel Resistors 语句应根据需要,通过默认方式或自定义等效属性计算逻辑,为归约后的器件计算对应的等效属性。

2.10 串联电阻归约

在对内置电阻进行对比时,串联电阻归约 默认执行。LVS Reduce Series Resistors 规格语句用于控制串联电阻归约功能。Calibre nmLVS 可将一组串联电阻(器件类型为 R 以及通过 LVS Device Type 规格语句指定的任何等效类型)归约为单个电阻。

若要进行归约,电阻必须至少具备两个引脚,且引脚名称需符合下表中规定的标准引脚名。同一组内的所有电阻必须具有相同的可选器件子类型、引脚数量和引脚名称。

所有正引脚和负引脚必须串联连接。在串联结构中,正、负引脚必须交替排列;除非引脚被指定为逻辑等效,否则正 - 正或负 - 负连接会在此处中断串联链。所有可选引脚必须分别连接至相同的网络(并联)。若可选引脚被指定为逻辑等效,则可进行引脚交换。第 475 页的 "引脚交换" 章节详细说明了如何指定逻辑等效。

图 18 展示了串联电阻归约的示例。图 18 串联电阻归约

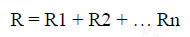

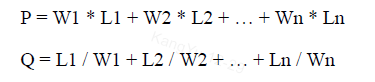

默认情况下,归约后电阻的阻值计算公式如下:

Ri分别为第 i 个电阻的阻值。

默认情况下,归约后器件的宽度和长度值计算公式如下:

且:

Wi,Li分别为第 i 个电阻的宽度和长度。

有效电阻、宽度和长度值会在版图和原理图中同时计算。若使用默认的有效属性计算方式(即未在 LVS Reduce Series Resistors 语句中指定用户自定义的有效属性计算),则在网表中必须分别使用内置属性名 "r" (电阻)、"w" (宽度)和 "l" (长度)来计算相应值,除非在第 481 页 "内置属性分类" 章节讨论的 Trace Property 语句中另有规定。

对于几何版图,R 型器件默认仅计算属性 R;但可通过在电阻 Device 语句中指定用户自定义的属性计算,来计算任意器件属性。之后,LVS Reduce Series Resistors 语句应根据需要,通过默认方式或用户自定义的有效属性计算,为归约后的器件计算相应的有效属性。

2.11 并联二极管归约

在对内置二极管进行对比时,并联二极管归约 默认执行。LVS Reduce Parallel Diodes 规格语句用于控制并联二极管归约功能。Calibre nmLVS 可将一组并联二极管(器件类型为 D 以及通过 LVS Device Type 规格语句指定的任何等效类型)归约为单个二极管。

若要进行归约,二极管必须至少具备两个引脚,且引脚名称需符合下表中规定的标准引脚名。同一组内的所有二极管必须具有相同的可选器件子类型、引脚数量和引脚名称。所有正引脚、负引脚和可选引脚必须连接至相同的网络。若引脚被指定为逻辑等效,器件归约过程中可对所有引脚进行交换。

图 19展示了并联二极管归约的示例。

图19并联二极管归约

默认情况下,归约后二极管的面积和周长值计算公式如下:

Ai 和Pi 分别为第 i 个二极管的面积和周长。

有效面积和周长值会在版图和原理图中同时计算。若使用默认的有效属性计算方式,则在网表中必须分别使用内置属性名 "a" (面积)和 "p" (周长)来计算相应值,除非在第 481 页 "内置属性分类" 章节讨论的 Trace Property 语句中另有规定。

可以覆盖默认的有效属性计算方式,并指定其他公式。

对于几何版图,D 型器件默认计算属性 A 和 P;但你可通过在二极管 Device 语句中指定用户自定义的属性计算,来计算任意器件属性。之后,LVS Reduce Parallel Diodes 语句应根据需要,为归约后的器件计算相应的有效属性。

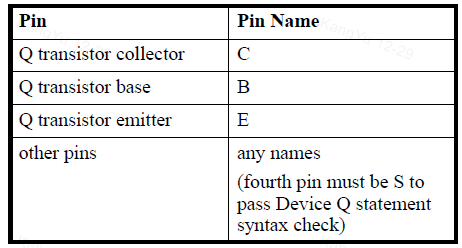

2.12 并联双极晶体管归约

在对内置晶体管进行对比时,并联双极晶体管归约 默认执行。Calibre nmLVS 可将一组并联双极晶体管(器件类型为 Q 以及通过 LVS Device Type 规格语句指定的任何等效类型)归约为单个晶体管。LVS Reduce Parallel Bipolar 规格语句用于控制并联双极晶体管归约功能。

若要进行归约,双极晶体管必须至少具备三个引脚,且引脚名称需符合下表中规定的标准引脚名。同一组内的所有晶体管必须具有相同的可选器件子类型、引脚数量和引脚名称。所有集电极、基极、发射极以及可选引脚(若有)必须连接至相同的网络。若可选引脚被指定为逻辑等效,器件归约过程中可对其进行交换。

图 20 展示了并联双极晶体管归约的示例。图 20 并联双极晶体管归约

默认情况下,归约后晶体管的有效面积计算公式如下:

其中,Ai为第 i 个晶体管的面积。

默认情况下,归约后晶体管的有效宽度和长度值计算公式如下:

且:

Ai分别为第 i 个晶体管的宽度和长度。

有效属性值会在版图和原理图中同时计算。若使用默认的有效属性计算方式(即未在 LVS Reduce Parallel Bipolar 语句中指定用户自定义的有效属性计算),则在网表中必须分别使用内置属性名 "a" (面积)、"w" (宽度)和 "l" (长度)来计算相应值,除非在 "内置属性分类" 章节讨论的 Trace Property 语句中另有规定。

对于几何版图,Q 型器件默认不计算任何属性;但你可通过在双极晶体管 Device 语句中指定用户自定义的属性计算,来计算任意器件属性。之后,LVS Reduce Parallel Bipolar 语句应根据需要,通过默认方式或用户自定义的有效属性计算,为归约后的器件计算相应的有效属性。

2.13 缺失和未知属性值

在某些情况下,Calibre nmLVS 可能会在器件归约过程中为属性分配 **"缺失(missing)"或"未知(unknown)"** 值。这种情况可能发生在有效属性计算阶段,无论使用内置还是用户自定义的有效属性计算公式,也无论使用内置还是通用的器件归约规格语句。

假设正在为属性 X 计算有效值,且有一组器件正被归约为单个器件(输入组),则适用以下规则:

-

若原始输入器件缺少属性 X,则归约后输入组的有效属性为 **"缺失"**。

-

若所有输入值均存在且有效,则 X 的有效值将按照适用的内置公式或用户指定公式进行计算。输入值定义为输入组中所有参与 X 有效值计算的属性值集合,可能包括 X 的原始值,以及参与 X 计算的其他属性值(即所谓的关联属性)。

-

若因缺少 X 的计算公式、计算时出现运行时问题(如除零、溢出等)或其他原因导致无法计算 X 的有效值,则 X 的有效值为 **"未知"**。例如,当输入组中部分器件存在属性 X 的值而其他器件缺失时,会得到 "未知" 值;当输入组中部分器件的属性 X 已为 "未知" 值时,或当输入组中所有器件均存在属性 X 的值,但参与 X 计算的另一属性缺失时,也会得到 "未知" 值。

-

若使用默认属性计算方式,输入组中具有相同字符串属性的器件会被归约,且有效字符串值等于该字符串属性;若任一输入器件缺少该字符串属性,则有效值为 **"未知"**。

若被追踪的属性出现未知值,该未知值会在 LVS 报告的 PROPERTY ERRORS (属性错误)部分作为差异进行报告,在报告中用问号(?)表示。原始输入器件中的缺失属性值会在报告的 SOURCE ERRORS (原理图错误)或 LAYOUT ERRORS (版图错误)部分作为差异进行报告(除非通过 LVS Report Option E 禁用)。归约后器件的缺失属性值不会被报告,因为其必然是由原始输入器件的缺失值导致的。

2.14 字符串属性的大小写对比

默认情况下,字符串属性的对比不区分大小写 。你可通过指定 Layout Case YES、Source Case YES 以及 LVS Compare Case YES 或 VALUES,将其设置为区分大小写

三、关键程序

1. 归约程序(Device Reduction Programs)

器件归约程序可出现在 LVS Reduce 系列规格语句中。例如,并联 MOS 管归约的语法如下:

svrf

LVS Reduce Parallel MOS { YES [ reduction_program ] | NO }器件归约程序是一组指令,用于控制器件归约的执行方式以及过程中需要计算的内容。该程序始终是某条 LVS Reduce 规格语句的一部分,并适用于该语句所操作的器件。器件归约程序的基本结构包括归约容差 和(可选的)有效属性计算,整个程序需用方括号括起。

归约容差和有效属性计算的顺序可任意排列。每个器件归约程序中必须至少包含其中一项,且最多只能指定一个归约容差部分和一个有效属性计算部分。以下是一个简单示例:

svrf

LVS REDUCE PARALLEL RESISTORS YES [

tolerance W 0

effective W

W = min( W )

]2. 归约容差(Tolerance in Device Reduction)

此处列出的器件归约语句允许你限制或阻止属性值存在差异的器件进行归约。

表 13-12 器件归约语句

| 语句 | 语句 |

|---|---|

LVS Reduce Parallel Bipolar |

LVS Reduce Series Capacitors |

LVS Reduce Parallel Capacitors |

LVS Reduce Series MOS |

LVS Reduce Parallel Diodes |

LVS Reduce Series Resistors |

LVS Reduce Parallel MOS |

LVS Reduce Split Gates |

LVS Reduce Parallel Resistors |

LVS Reduce |

归约容差包含两个可选语句:TOLerance(用于数值属性)和 TOLerance STRing(用于字符串属性),语法如下:

svrf

[TOLerance numeric_property_name tolerance_number

[... numeric_property_name tolerance_number]]

[TOLerance STRing string_property_name

[... string_property_name]]示例:

svrf

LVS REDUCE PARALLEL MOS YES [

TOLERANCE L 0 W 0

TOLERANCE STRING str1 str2 str3

]TOLERANCE 和 TOLERANCE STRING 参数的顺序可任意排列。TOLERANCE 关键字后需跟一个或多个属性名 - 容差值 对,用于指定属性名及其对应的容差值,每个 tolerance_number 参数均对应其前面的 property_name 参数。TOLERANCE STRING 关键字后需跟一个或多个字符串属性名,用于指定字符串属性名,字符串属性不指定容差值。

属性名必须为简单名称;不允许使用 "instpar (w)" 等属性名与 SPICE 参数的组合形式。若要处理此类组合,请使用 LVS Property Map 规格语句。

每个器件归约程序中最多只能指定一个归约容差部分。

对于 TOLERANCE 规格,若器件具有某一数值属性,且该属性的数值存在差异,且差异超过 tolerance_number,则这些器件不会被归约在一起。tolerance_number 为浮点数,表示容差百分比,差异计算公式如下:\(\text{abs}((v1-v2)/v1) \times 100\)其中,abs 为绝对值函数,v1 和 v2 为待对比的属性值,v1 为原理图属性的值。值为零的属性与任何非零属性的差异视为无穷大;两个值均为零的属性视为完全相同,差异为零。

当你指定多个属性名 - 容差值对时,Calibre nmLVS 会对每个属性分别进行检查。若至少有一个属性的差异超过其指定容差,则器件不会被归约。

对于 TOLERANCE STRING 规格,若器件具有某一字符串属性,且该属性的字符串值存在差异,则这些器件不会被归约。对比的大小写敏感性由 LVS Compare Case 规格语句中的 VALUES 设置决定。

当指定多个字符串属性名时,Calibre nmLVS 会对每个字符串属性分别进行检查;若至少有一个字符串值与其他值不相等,则器件不会被归约。

同一属性名不能在同一个器件归约程序的 TOLERANCE 和 TOLERANCE STRING 语句中同时声明。例如,以下语句会产生编译错误:

svrf

LVS REDUCE ... [

TOLERANCE x 0

TOLERANCE STRING x // 错误:重复声明 'x'

]在器件归约过程中,Calibre nmLVS 会迭代执行串联和并联归约步骤。例如,电容的串联和并联归约步骤会重复进行。在每次迭代中,Calibre nmLVS 会为当前已归约的器件计算有效属性值(如有效宽度、长度、电容、电阻等)。在第一次迭代中,TOLERANCE 和 TOLERANCE STRING 语句的处理基于输入数据库中指定的原始属性值;在后续迭代中,其处理则基于当前已计算的有效属性值。在每个步骤中,器件的属性值可能有效,也可能被分配为 "缺失" 或 "未知" 类型.

若某器件缺少归约 TOLERANCE 或 TOLERANCE STRING 语句中使用的属性,则该器件会参与归约,如同上述语句不存在一样。换句话说,对于归约 TOLERANCE 或 TOLERANCE STRING 语句而言,属性值缺失的器件其行为等同于该属性值与所有其他器件的属性值完全相同。若该器件为原始输入器件,则会报告缺失属性差异(你可通过 LVS Report Option E 禁用缺失属性差异报告)。

若在(数值型)TOLERANCE 语句中指定了某一属性名,但在特定器件上找到的却是同名的字符串属性,则对于该 TOLERANCE 语句而言,该属性会被视为缺失。同理,若在 TOLERANCE STRING 语句中指定了某一属性名,但在特定器件上找到的却是同名的数值属性,则对于该 TOLERANCE STRING 语句而言,该属性会被视为缺失。

若某器件的归约 TOLERANCE 或 TOLERANCE STRING 语句中使用的属性值为未知,则该器件不会参与后续任何归约迭代。因属性值未知而导致归约停止的器件,会在 LVS 报告的 Information And Warnings (信息与警告)部分的 Source Instances With Undetermined Reduction TOLERANCE Properties (原理图中归约容差属性未确定的实例)和 Layout Instances With Undetermined Reduction TOLERANCE Properties(版图中归约容差属性未确定的实例)标题下进行报告。

示例:

3. 归约容差示例

-

以下语句仅在长度值相等时,对并联 MOS 管进行归约: svrf

LVS REDUCE PARALLEL MOS YES [TOLERANCE L 0] -

以下语句仅在宽度和长度值均相等时,对并联 MOS 管进行归约: svrf

LVS REDUCE PARALLEL MOS YES [TOLERANCE L 0 W 0] -

以下语句仅在电阻值容差在 5% 以内且长度值相等时,对串联电阻进行归约: svrf

LVS REDUCE SERIES RESISTORS YES [TOLERANCE R 5 L 0] -

以下示例仅在电容值相等且字符串属性

COLOR的值也相等时,对并联电容进行归约:svrf

LVS REDUCE PARALLEL CAPACITORS YES [

TOLERANCE C 0

TOLERANCE STRING COLOR

]四、关键注意事项

-

内置器件的引脚规则 :所有归约仅适用于满足内置器件引脚命名规则 的器件(如 MOS 管的

G/S/D,电阻的POS/NEG),否则视为用户定义器件,无默认归约。 -

LDD 器件的特殊性 :LDD 型 MOS 管的 S/D 引脚不可交换,串联时需严格 S-D 交替,否则会打断串联结构。

-

分裂栅与逻辑门识别 :逻辑门识别开启时,分裂栅各串的晶体管顺序可不同(除非指定

SAME ORDER);逻辑门识别关闭时,强制要求顺序一致。 -

归约与过滤的顺序:器件过滤在归约之后执行,即先将并行 MOS 管归约为一个,再判断是否为未使用器件。