参考代码仓库地址:https://github.com/Alioth2000/PYNQ-Z2-traffic-signs-recognition

01 创建卷积层 IP (Conv Core)

cpp

#include "conv_core.h"

//Feature: [H][W][C]

//kernel: [Ky][Kx][CHin][CHout]

void Conv(ap_uint<16> CHin,ap_uint<16> Hin,ap_uint<16> Win,ap_uint<16> CHout,

ap_uint<8> Kx,ap_uint<8> Ky,ap_uint<8> Sx,ap_uint<8> Sy,ap_uint<1> mode,ap_uint<1> relu_en,

Dtype_f feature_in[],Dtype_w W[],Dtype_w bias[],Dtype_f feature_out[]

)//mode: 0:VALID, 1:SAME

{

//#pragma HLS PIPELINE enable_flush

#pragma HLS INTERFACE m_axi depth=4294967295 port=feature_out offset=slave

#pragma HLS INTERFACE m_axi depth=4294967295 port=bias offset=slave

#pragma HLS INTERFACE m_axi depth=4294967295 port=W offset=slave

#pragma HLS INTERFACE m_axi depth=4294967295 port=feature_in offset=slave

#pragma HLS INTERFACE s_axilite port=relu_en

#pragma HLS INTERFACE s_axilite port=CHout

#pragma HLS INTERFACE s_axilite port=Sx

#pragma HLS INTERFACE s_axilite port=Hin

#pragma HLS INTERFACE s_axilite port=CHin

#pragma HLS INTERFACE s_axilite port=Kx

#pragma HLS INTERFACE s_axilite port=mode

#pragma HLS INTERFACE s_axilite port=Sy

#pragma HLS INTERFACE s_axilite port=Ky

#pragma HLS INTERFACE s_axilite port=Win

#pragma HLS INTERFACE s_axilite port=return

ap_uint<8> pad_x,pad_y;

if(mode==0)

{

pad_x=0;pad_y=0;

}

else

{

pad_x=(Kx-1)/2;pad_y=(Ky-1)/2;

}

ap_uint<16> Hout,Wout;

Wout=(Win+2*pad_x-Kx)/Sx+1;

Hout=(Hin+2*pad_y-Ky)/Sy+1;

for(int cout=0;cout<CHout;cout++)

for(int i=0;i<Hout;i++)

for(int j=0;j<Wout;j++)

{

Dtype_acc sum=0;

for(int ii=0;ii<Ky;ii++)

for(int jj=0;jj<Kx;jj++)

{

ap_int<16> h=i*Sy-pad_y+ii;

ap_int<16> w=j*Sx-pad_x+jj;

if(h>=0 && w>=0 && h<Hin && w<Win)

{

for(int cin=0;cin<CHin;cin++)

{

//Feature [H][W][C]

//kernel: [Ky][Kx][CHin][CHout]

//Dtype_mul tp=feature_in[h][w][cin]*w[ii][jj][cin][cout];

//std::cout<<"h:"<<h<<",w"<<w<<",cin"<<cin<<"\n";

//std::cout<<"feature_in["<<h*CHin*Win+w*CHin+cin<<"]*W["<<ii*Kx*CHin*CHout+jj*CHin*CHout+cin*CHout+cout<<"]\n";

Dtype_mul tp=feature_in[h*CHin*Win+w*CHin+cin]*W[ii*Kx*CHin*CHout+jj*CHin*CHout+cin*CHout+cout];

sum+=tp;

}

}

}

sum+=bias[cout];

// if(relu_en & sum<0)

if(relu_en && (sum < 0))

sum=0;

//feature_out[i][j][cout]=sum;

feature_out[i*Wout*CHout+j*CHout+cout]=sum;

}

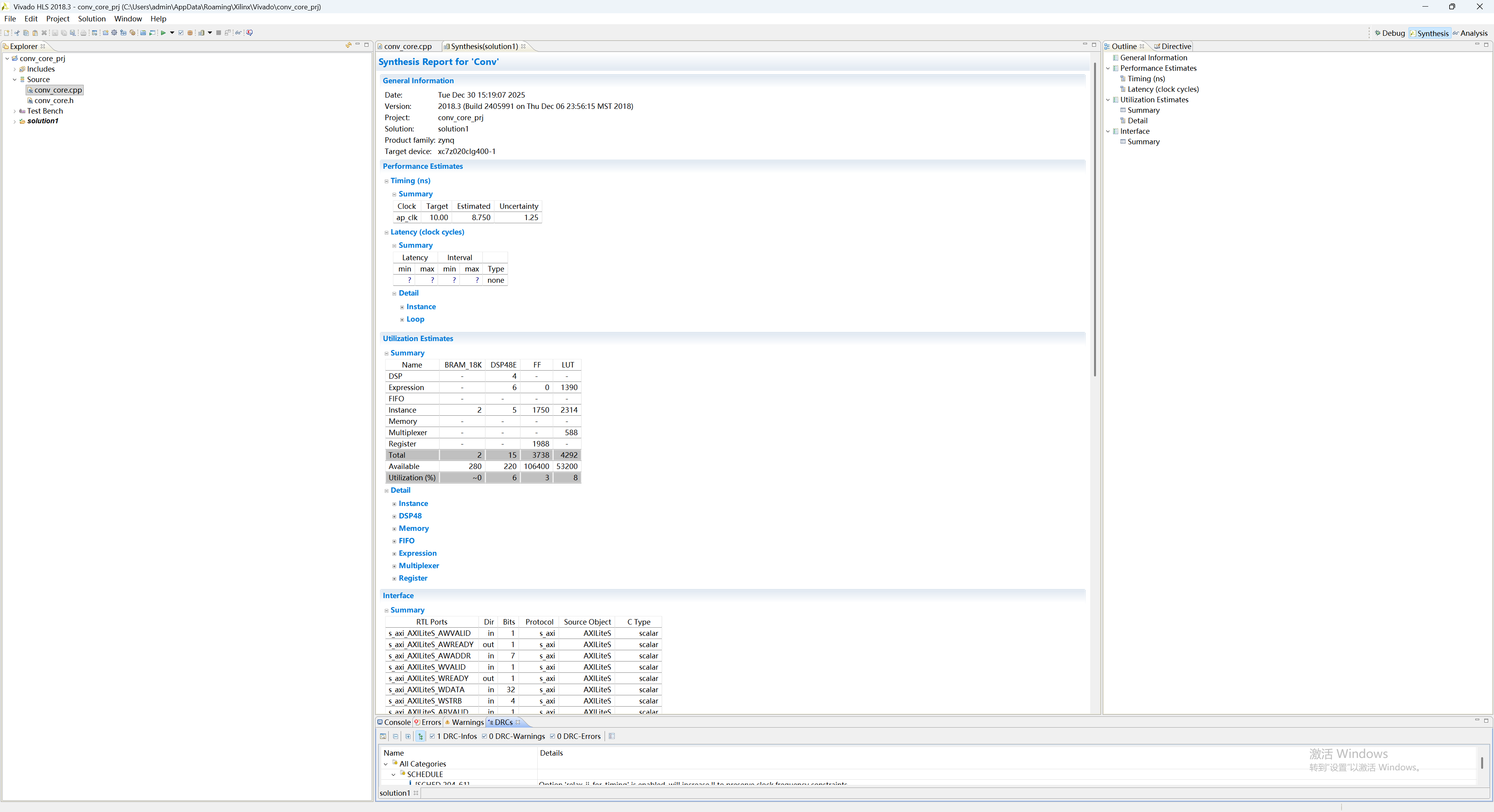

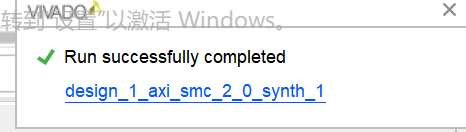

}综合后的console输出:

bash

Starting C synthesis ...

D:/Xilinx/Vivado/2018.3/bin/vivado_hls.bat C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj/solution1/csynth.tcl

INFO: [HLS 200-10] Running 'D:/Xilinx/Vivado/2018.3/bin/unwrapped/win64.o/vivado_hls.exe'

INFO: [HLS 200-10] For user 'admin' on host 'desktop-jd0ieba' (Windows NT_amd64 version 6.2) on Tue Dec 30 14:44:54 +0800 2025

INFO: [HLS 200-10] In directory 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado'

INFO: [HLS 200-10] Opening project 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj'.

INFO: [HLS 200-10] Adding design file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.cpp' to the project

INFO: [HLS 200-10] Adding design file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.h' to the project

INFO: [HLS 200-10] Adding test bench file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/main.cpp' to the project

INFO: [HLS 200-10] Opening solution 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj/solution1'.

INFO: [SYN 201-201] Setting up clock 'default' with a period of 10ns.

INFO: [HLS 200-10] Setting target device to 'xc7z020clg400-1'

INFO: [SYN 201-201] Setting up clock 'default' with a period of 10ns.

INFO: [SCHED 204-61] Option 'relax_ii_for_timing' is enabled, will increase II to preserve clock frequency constraints.

INFO: [HLS 200-10] Analyzing design file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.cpp' ...

WARNING: [HLS 200-40] In file included from D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.cpp:1:

D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.cpp:67:16: warning: & has lower precedence than <; < will be evaluated first [-Wparentheses]

if(relu_en & sum<0)

^~~~~~~

D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.cpp:67:16: note: place parentheses around the < expression to silence this warning

if(relu_en & sum<0)

^

( )

D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.cpp:67:16: note: place parentheses around the & expression to evaluate it first

if(relu_en & sum<0)

^

( )

1 warning generated.

INFO: [HLS 200-111] Finished Linking Time (s): cpu = 00:00:00 ; elapsed = 00:00:07 . Memory (MB): peak = 102.617 ; gain = 17.184

INFO: [HLS 200-111] Finished Checking Pragmas Time (s): cpu = 00:00:00 ; elapsed = 00:00:07 . Memory (MB): peak = 102.617 ; gain = 17.184

INFO: [HLS 200-10] Starting code transformations ...

INFO: [HLS 200-111] Finished Standard Transforms Time (s): cpu = 00:00:01 ; elapsed = 00:00:07 . Memory (MB): peak = 123.754 ; gain = 38.320

INFO: [HLS 200-10] Checking synthesizability ...

INFO: [HLS 200-111] Finished Checking Synthesizability Time (s): cpu = 00:00:01 ; elapsed = 00:00:07 . Memory (MB): peak = 134.797 ; gain = 49.363

INFO: [XFORM 203-401] Performing if-conversion on hyperblock to (D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.cpp:41:16) in function 'Conv'... converting 3 basic blocks.

INFO: [HLS 200-111] Finished Pre-synthesis Time (s): cpu = 00:00:01 ; elapsed = 00:00:08 . Memory (MB): peak = 167.133 ; gain = 81.699

INFO: [HLS 200-111] Finished Architecture Synthesis Time (s): cpu = 00:00:01 ; elapsed = 00:00:08 . Memory (MB): peak = 169.957 ; gain = 84.523

INFO: [HLS 200-10] Starting hardware synthesis ...

INFO: [HLS 200-10] Synthesizing 'Conv' ...

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-42] -- Implementing module 'Conv'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [SCHED 204-11] Starting scheduling ...

INFO: [SCHED 204-11] Finished scheduling.

INFO: [HLS 200-111] Elapsed time: 7.774 seconds; current allocated memory: 119.364 MB.

INFO: [HLS 200-434] Only 0 loops out of a total 6 loops have been pipelined in this design.

INFO: [BIND 205-100] Starting micro-architecture generation ...

INFO: [BIND 205-101] Performing variable lifetime analysis.

INFO: [BIND 205-101] Exploring resource sharing.

INFO: [BIND 205-101] Binding ...

INFO: [BIND 205-100] Finished micro-architecture generation.

INFO: [HLS 200-111] Elapsed time: 0.067 seconds; current allocated memory: 120.473 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Generating RTL for module 'Conv'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/gmem' to 'm_axi'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/CHin_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Hin_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Win_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/CHout_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Kx_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Ky_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Sx_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Sy_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/mode_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/relu_en_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/feature_in' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/W' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/bias' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/feature_out' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on function 'Conv' to 's_axilite & ap_ctrl_hs'.

INFO: [RTGEN 206-100] Bundling port 'return', 'CHin_V', 'Hin_V', 'Win_V', 'CHout_V', 'Kx_V', 'Ky_V', 'Sx_V', 'Sy_V', 'mode_V', 'relu_en_V', 'feature_in', 'W', 'bias' and 'feature_out' to AXI-Lite port AXILiteS.

INFO: [SYN 201-210] Renamed object name 'Conv_fadd_32ns_32ns_32_5_full_dsp_1' to 'Conv_fadd_32ns_32bkb' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_fmul_32ns_32ns_32_4_max_dsp_1' to 'Conv_fmul_32ns_32cud' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_fcmp_32ns_32ns_1_1_1' to 'Conv_fcmp_32ns_32dEe' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_sdiv_19s_9ns_16_23_seq_1' to 'Conv_sdiv_19s_9nseOg' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_mul_mul_16ns_16ns_32_1_1' to 'Conv_mul_mul_16nsfYi' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_mul_mul_16ns_16s_32_1_1' to 'Conv_mul_mul_16nsg8j' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_mac_muladd_16ns_16s_48ns_48_1_1' to 'Conv_mac_muladd_1hbi' due to the length limit 20

INFO: [RTGEN 206-100] Generating core module 'Conv_fadd_32ns_32bkb': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_fcmp_32ns_32dEe': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_fmul_32ns_32cud': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_mac_muladd_1hbi': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_mul_mul_16nsfYi': 2 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_mul_mul_16nsg8j': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_sdiv_19s_9nseOg': 2 instance(s).

INFO: [RTGEN 206-100] Finished creating RTL model for 'Conv'.

INFO: [HLS 200-111] Elapsed time: 0.129 seconds; current allocated memory: 122.627 MB.

INFO: [RTMG 210-282] Generating pipelined core: 'Conv_sdiv_19s_9nseOg_div'

INFO: [HLS 200-111] Finished generating all RTL models Time (s): cpu = 00:00:02 ; elapsed = 00:00:09 . Memory (MB): peak = 181.230 ; gain = 95.797

INFO: [SYSC 207-301] Generating SystemC RTL for Conv.

INFO: [VHDL 208-304] Generating VHDL RTL for Conv.

INFO: [VLOG 209-307] Generating Verilog RTL for Conv.

INFO: [HLS 200-112] Total elapsed time: 9.062 seconds; peak allocated memory: 122.627 MB.

Finished C synthesis.

Starting C synthesis ...

D:/Xilinx/Vivado/2018.3/bin/vivado_hls.bat C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj/solution1/csynth.tcl

INFO: [HLS 200-10] Running 'D:/Xilinx/Vivado/2018.3/bin/unwrapped/win64.o/vivado_hls.exe'

INFO: [HLS 200-10] For user 'admin' on host 'desktop-jd0ieba' (Windows NT_amd64 version 6.2) on Tue Dec 30 14:53:40 +0800 2025

INFO: [HLS 200-10] In directory 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado'

INFO: [HLS 200-10] Opening project 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj'.

INFO: [HLS 200-10] Adding design file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.cpp' to the project

INFO: [HLS 200-10] Adding design file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.h' to the project

INFO: [HLS 200-10] Adding test bench file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/main.cpp' to the project

INFO: [HLS 200-10] Opening solution 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj/solution1'.

INFO: [SYN 201-201] Setting up clock 'default' with a period of 10ns.

INFO: [HLS 200-10] Setting target device to 'xc7z020clg400-1'

INFO: [SCHED 204-61] Option 'relax_ii_for_timing' is enabled, will increase II to preserve clock frequency constraints.

INFO: [HLS 200-10] Analyzing design file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.cpp' ...

INFO: [HLS 200-111] Finished Linking Time (s): cpu = 00:00:01 ; elapsed = 00:00:04 . Memory (MB): peak = 102.664 ; gain = 17.516

INFO: [HLS 200-111] Finished Checking Pragmas Time (s): cpu = 00:00:01 ; elapsed = 00:00:04 . Memory (MB): peak = 102.664 ; gain = 17.516

INFO: [HLS 200-10] Starting code transformations ...

INFO: [HLS 200-111] Finished Standard Transforms Time (s): cpu = 00:00:01 ; elapsed = 00:00:05 . Memory (MB): peak = 123.234 ; gain = 38.086

INFO: [HLS 200-10] Checking synthesizability ...

INFO: [HLS 200-111] Finished Checking Synthesizability Time (s): cpu = 00:00:01 ; elapsed = 00:00:05 . Memory (MB): peak = 134.340 ; gain = 49.191

INFO: [XFORM 203-401] Performing if-conversion on hyperblock to (D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/conv_core/conv_core.cpp:41:16) in function 'Conv'... converting 3 basic blocks.

INFO: [HLS 200-111] Finished Pre-synthesis Time (s): cpu = 00:00:01 ; elapsed = 00:00:05 . Memory (MB): peak = 166.160 ; gain = 81.012

INFO: [HLS 200-111] Finished Architecture Synthesis Time (s): cpu = 00:00:01 ; elapsed = 00:00:05 . Memory (MB): peak = 168.957 ; gain = 83.809

INFO: [HLS 200-10] Starting hardware synthesis ...

INFO: [HLS 200-10] Synthesizing 'Conv' ...

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-42] -- Implementing module 'Conv'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [SCHED 204-11] Starting scheduling ...

INFO: [SCHED 204-11] Finished scheduling.

INFO: [HLS 200-111] Elapsed time: 5.123 seconds; current allocated memory: 119.149 MB.

INFO: [HLS 200-434] Only 0 loops out of a total 6 loops have been pipelined in this design.

INFO: [BIND 205-100] Starting micro-architecture generation ...

INFO: [BIND 205-101] Performing variable lifetime analysis.

INFO: [BIND 205-101] Exploring resource sharing.

INFO: [BIND 205-101] Binding ...

INFO: [BIND 205-100] Finished micro-architecture generation.

INFO: [HLS 200-111] Elapsed time: 0.063 seconds; current allocated memory: 120.274 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Generating RTL for module 'Conv'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/gmem' to 'm_axi'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/CHin_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Hin_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Win_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/CHout_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Kx_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Ky_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Sx_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/Sy_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/mode_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/relu_en_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/feature_in' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/W' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/bias' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Conv/feature_out' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on function 'Conv' to 's_axilite & ap_ctrl_hs'.

INFO: [RTGEN 206-100] Bundling port 'return', 'CHin_V', 'Hin_V', 'Win_V', 'CHout_V', 'Kx_V', 'Ky_V', 'Sx_V', 'Sy_V', 'mode_V', 'relu_en_V', 'feature_in', 'W', 'bias' and 'feature_out' to AXI-Lite port AXILiteS.

INFO: [SYN 201-210] Renamed object name 'Conv_fadd_32ns_32ns_32_5_full_dsp_1' to 'Conv_fadd_32ns_32bkb' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_fmul_32ns_32ns_32_4_max_dsp_1' to 'Conv_fmul_32ns_32cud' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_fcmp_32ns_32ns_1_1_1' to 'Conv_fcmp_32ns_32dEe' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_sdiv_19s_9ns_16_23_seq_1' to 'Conv_sdiv_19s_9nseOg' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_mul_mul_16ns_16ns_32_1_1' to 'Conv_mul_mul_16nsfYi' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_mul_mul_16ns_16s_32_1_1' to 'Conv_mul_mul_16nsg8j' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Conv_mac_muladd_16ns_16s_48ns_48_1_1' to 'Conv_mac_muladd_1hbi' due to the length limit 20

INFO: [RTGEN 206-100] Generating core module 'Conv_fadd_32ns_32bkb': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_fcmp_32ns_32dEe': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_fmul_32ns_32cud': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_mac_muladd_1hbi': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_mul_mul_16nsfYi': 2 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_mul_mul_16nsg8j': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Conv_sdiv_19s_9nseOg': 2 instance(s).

INFO: [RTGEN 206-100] Finished creating RTL model for 'Conv'.

INFO: [HLS 200-111] Elapsed time: 0.128 seconds; current allocated memory: 122.427 MB.

INFO: [RTMG 210-282] Generating pipelined core: 'Conv_sdiv_19s_9nseOg_div'

INFO: [HLS 200-111] Finished generating all RTL models Time (s): cpu = 00:00:02 ; elapsed = 00:00:06 . Memory (MB): peak = 179.340 ; gain = 94.191

INFO: [SYSC 207-301] Generating SystemC RTL for Conv.

INFO: [VHDL 208-304] Generating VHDL RTL for Conv.

INFO: [VLOG 209-307] Generating Verilog RTL for Conv.

INFO: [HLS 200-112] Total elapsed time: 6.403 seconds; peak allocated memory: 122.427 MB.

Finished C synthesis.INFO: [HLS 200-434] Only 0 loops out of a total 6 loops have been pipelined in this design.

这代表你的加速器目前是纯串行跑的,没有利用 FPGA 的并行流水线能力。

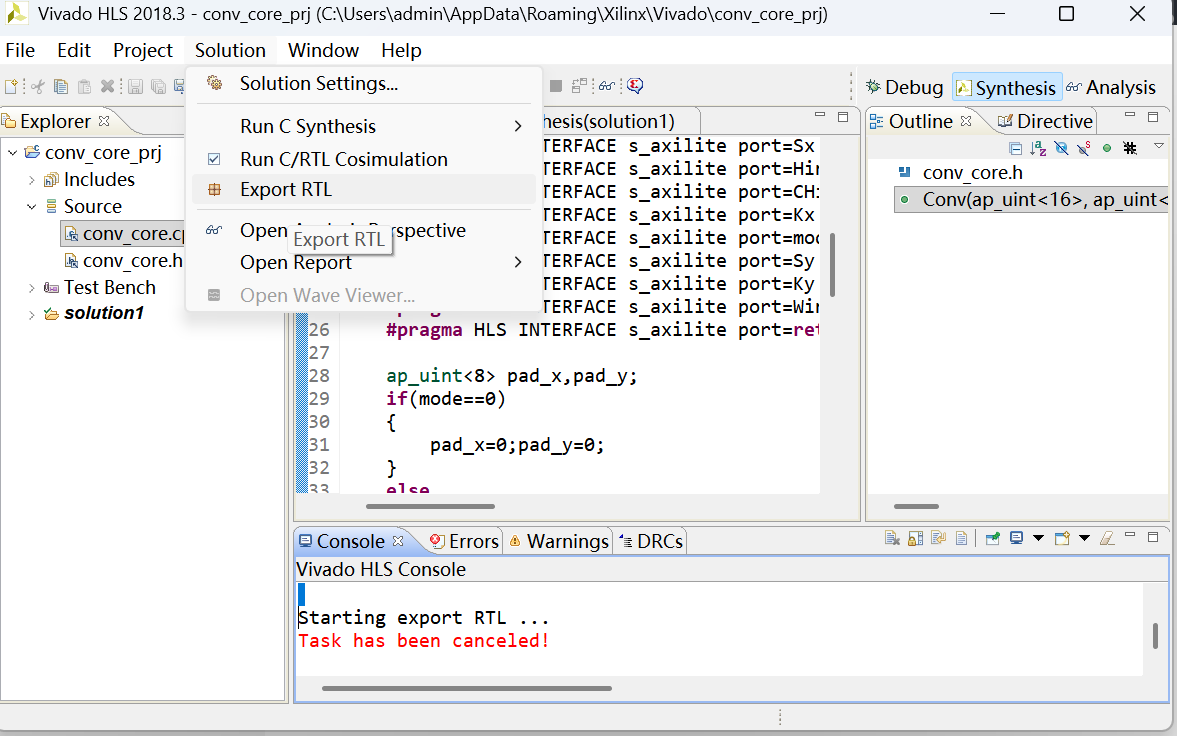

导出IP核

在 Vivado HLS 工具栏点击 Export RTL (或者菜单 Solution -> Export RTL)。

保持默认设置,点击 OK。

等待完成后,确保在工程目录 solution1/impl/ip 下看到了 zip 文件。

具体报错信息:

bash

Starting export RTL ...

D:/Xilinx/Vivado/2018.3/bin/vivado_hls.bat C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj/solution1/export.tcl

INFO: [HLS 200-10] Running 'D:/Xilinx/Vivado/2018.3/bin/unwrapped/win64.o/vivado_hls.exe'

INFO: [HLS 200-10] For user 'admin' on host 'desktop-jd0ieba' (Windows NT_amd64 version 6.2) on Tue Dec 30 15:00:00 +0800 2025

INFO: [HLS 200-10] In directory 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado'

INFO: [HLS 200-10] Opening project 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj'.

INFO: [HLS 200-10] Opening solution 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj/solution1'.

INFO: [SYN 201-201] Setting up clock 'default' with a period of 10ns.

INFO: [HLS 200-10] Setting target device to 'xc7z020clg400-1'

INFO: [IMPL 213-8] Exporting RTL as a Vivado IP.

****** Vivado v2018.3 (64-bit)

**** SW Build 2405991 on Thu Dec 6 23:38:27 MST 2018

**** IP Build 2404404 on Fri Dec 7 01:43:56 MST 2018

** Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.

source run_ippack.tcl -notrace

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository 'D:/Xilinx/Vivado/2018.3/data/ip'.

WARNING: [IP_Flow 19-4832] The IP name 'Conv_ap_fadd_3_full_dsp_32' you have specified is long. The Windows operating system has path length limitations. It is recommended you use shorter names to reduce the likelihood of issues.

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'Conv_ap_fadd_3_full_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'Conv_ap_fadd_3_full_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'Conv_ap_fcmp_0_no_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'Conv_ap_fcmp_0_no_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'Conv_ap_fmul_2_max_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'Conv_ap_fmul_2_max_dsp_32'...

bad lexical cast: source type value could not be interpreted as target

while executing

"rdi::set_property core_revision 2512301500 {component component_1}"

invoked from within

"set_property core_revision $Revision $core"

(file "run_ippack.tcl" line 1089)

INFO: [Common 17-206] Exiting Vivado at Tue Dec 30 15:00:06 2025...

ERROR: [IMPL 213-28] Failed to generate IP.

command 'ap_source' returned error code

while executing

"source C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj/solution1/export.tcl"

invoked from within

"hls::main C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj/solution1/export.tcl"

("uplevel" body line 1)

invoked from within

"uplevel 1 hls::main {*}$args"

(procedure "hls_proc" line 5)

invoked from within

"hls_proc $argv"

Finished export RTL.解决方案:

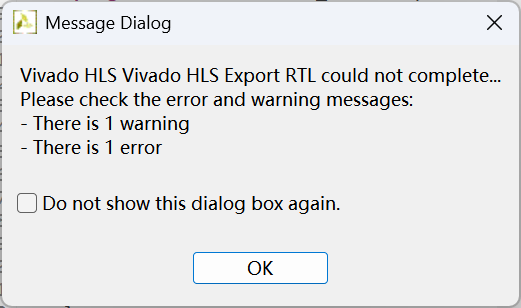

这是一个非常经典且著名的 "Y2K22 溢出 Bug"(虽然现在已经是 2025 年了,但原理一样)。

错误原因分析

请看报错日志中这行最关键的信息:

text

bad lexical cast: source type value could not be interpreted as target

while executing

"rdi::set_property core_revision 2512301500 {component component_1}"- 数字由来:Vivado HLS 2018.3 会自动用当前的"年月日时分"来生成 IP 核的版本号(Revision)。

- 你当前的时间是:2025 年 12 月 30 日 15 点 00分。

- 生成的版本号就是:

2512301500。

- 溢出问题 :Vivado 内部定义

core_revision这个变量是一个 32位有符号整数 (Signed 32-bit Integer)。

- 32位整数的最大值是 2,147,483,647 (约 21 亿)。

- 你的版本号 2,512,301,500 (约 25 亿) 超过了这个最大值。

- 结果 :软件无法把这个巨大的数字转换成整数,于是报错

bad lexical cast,导致 IP 核生成失败。

这个问题从 2022 年 1 月 1 日开始爆发(当时版本号变成 2201010000 > 21亿),所有旧版 Vivado (2020.2 之前) 都会遇到这个问题。

解决方案

你有两种方法解决这个问题,推荐第一种,最快最省事。

方法一:由于是时间造成的,那就"时光倒流" (推荐)

这是最简单的临时解决办法,不需要下载任何补丁。

- 关闭 Vivado HLS。

- 修改 Windows 系统时间:

- 把年份改回 2020 年 (或者 2021 年及以前的任何时间)。

- 例如改为:2020年 12 月 30 日。

- 重新打开 Vivado HLS。

- 打开你的工程,再次点击 Export RTL。

- 此时生成的版本号会是

2012301500(20亿),小于 21亿,就能成功通过了。

- 导出成功拿到 zip 包后,你可以把系统时间改回来。

方法二:打 Xilinx 官方补丁 (永久修复)

如果你不想每次都改时间,需要下载官方提供的 Python 脚本补丁来修复 Vivado 的安装文件。

- 搜索关键词

Xilinx Y2K22 patch或访问 Xilinx 官方支持页面(Answer Record 76960)。https://adaptivesupport.amd.com/s/article/76960?language=en_US - 下载

y2k22_patch-1.2.zip。 - 按照里面的

README说明,把补丁文件解压到 Vivado 安装目录(通常是D:\Xilinx\Vivado\2018.3)并运行脚本。 - 这会替换掉 HLS 导出工具中的一个

.py文件,强制修改版本号生成的逻辑。

总结

你现在的工程本身没有任何问题,纯粹是 Vivado 2018.3 软件太老,没料到你会活到 2022 年以后用它。

👉 请直接把电脑年份改成 2020 年,然后重试 Export RTL,立刻就能好。

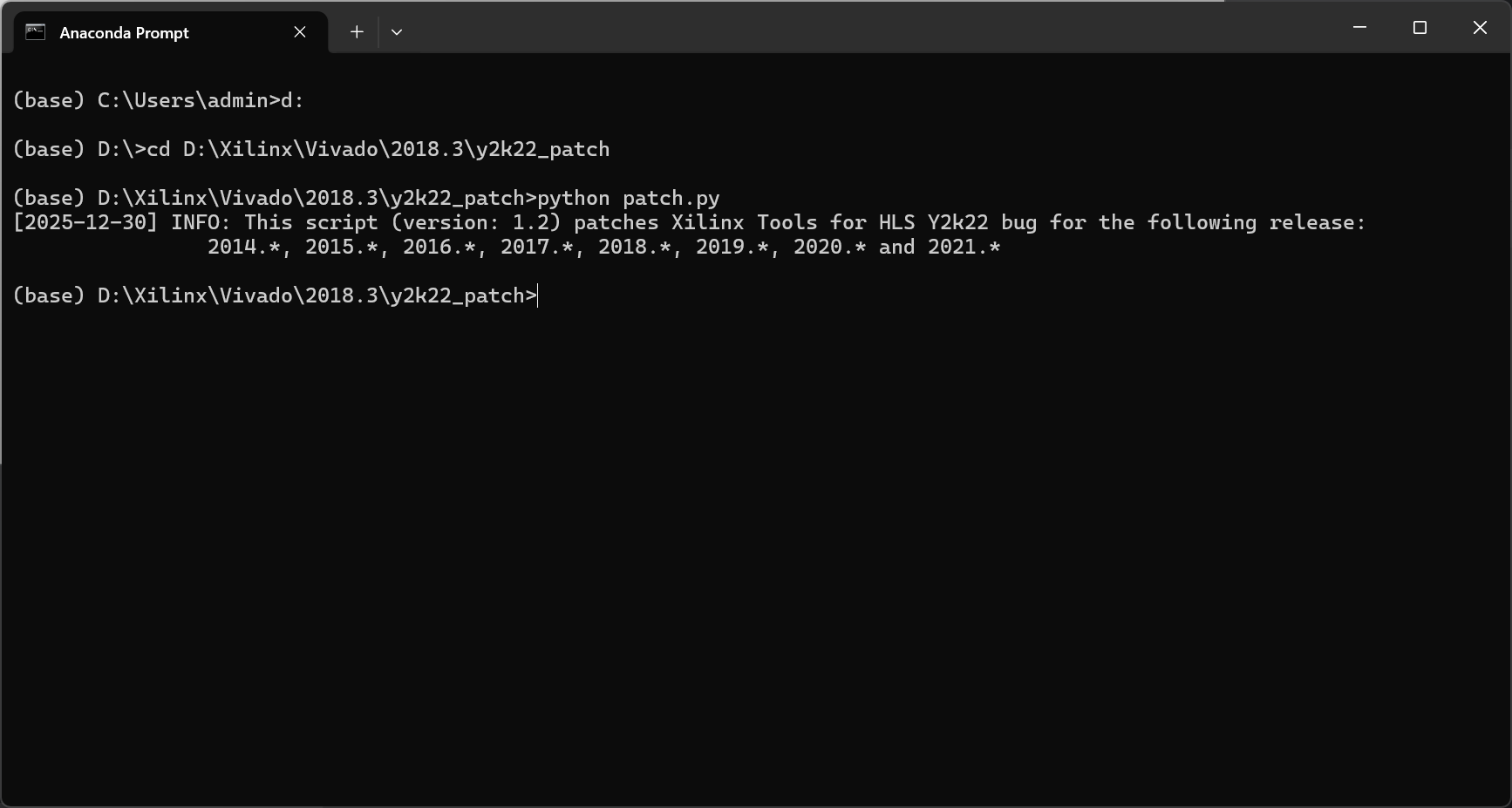

没有修复成功,应该把y2k22_patch 文件夹解压到D:\Xilinx目录下

bash

Starting export RTL ...

D:/Xilinx/Vivado/2018.3/bin/vivado_hls.bat C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj/solution1/export.tcl

INFO: Applying HLS Y2K22 patch v1.2 for IP revision

INFO: [HLS 200-10] Running 'D:/Xilinx/Vivado/2018.3/bin/unwrapped/win64.o/vivado_hls.exe'

INFO: [HLS 200-10] For user 'admin' on host 'desktop-jd0ieba' (Windows NT_amd64 version 6.2) on Tue Dec 30 15:27:56 +0800 2025

INFO: [HLS 200-10] In directory 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado'

INFO: [HLS 200-10] Opening project 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj'.

INFO: [HLS 200-10] Opening solution 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/conv_core_prj/solution1'.

INFO: [SYN 201-201] Setting up clock 'default' with a period of 10ns.

INFO: [HLS 200-10] Setting target device to 'xc7z020clg400-1'

INFO: [IMPL 213-8] Exporting RTL as a Vivado IP.

****** Vivado v2018.3 (64-bit)

**** SW Build 2405991 on Thu Dec 6 23:38:27 MST 2018

**** IP Build 2404404 on Fri Dec 7 01:43:56 MST 2018

** Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.

source run_ippack.tcl -notrace

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository 'D:/Xilinx/Vivado/2018.3/data/ip'.

WARNING: [IP_Flow 19-4832] The IP name 'Conv_ap_fadd_3_full_dsp_32' you have specified is long. The Windows operating system has path length limitations. It is recommended you use shorter names to reduce the likelihood of issues.

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'Conv_ap_fadd_3_full_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'Conv_ap_fadd_3_full_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'Conv_ap_fcmp_0_no_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'Conv_ap_fcmp_0_no_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'Conv_ap_fmul_2_max_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'Conv_ap_fmul_2_max_dsp_32'...

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository 'D:/Xilinx/Vivado/2018.3/data/ip'.

INFO: [Common 17-206] Exiting Vivado at Tue Dec 30 15:28:03 2025...

Finished export RTL.成功导出!

02 创建池化层 IP (Pool Core)

你需要重新建立一个新工程来处理池化运算。

新建工程:点击文件菜单 -> New Project。

设置项目名称:比如 pool_core_prj。

添加源文件:

选择 HLS/pool_core/ 文件夹下的 pool_core.cpp 和 pool_core.h。

关键设置 (Top Function):点击 Browse...,这次选择 Pool 函数作为顶层函数。

添加测试文件:选择同目录下的 main.cpp。

选择芯片:同样选择 xc7z020clg400-1。

执行综合与导出:

Run C Synthesis。

Export RTL。

bash

Starting C synthesis ...

D:/Xilinx/Vivado/2018.3/bin/vivado_hls.bat C:/Users/admin/AppData/Roaming/Xilinx/Vivado/pool_core_prj/solution1/csynth.tcl

INFO: Applying HLS Y2K22 patch v1.2 for IP revision

INFO: [HLS 200-10] Running 'D:/Xilinx/Vivado/2018.3/bin/unwrapped/win64.o/vivado_hls.exe'

INFO: [HLS 200-10] For user 'admin' on host 'desktop-jd0ieba' (Windows NT_amd64 version 6.2) on Tue Dec 30 15:33:49 +0800 2025

INFO: [HLS 200-10] In directory 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado'

INFO: [HLS 200-10] Opening project 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/pool_core_prj'.

INFO: [HLS 200-10] Adding design file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/pool_core/pool_core.cpp' to the project

INFO: [HLS 200-10] Adding design file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/pool_core/pool_core.h' to the project

INFO: [HLS 200-10] Adding test bench file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/pool_core/main.cpp' to the project

INFO: [HLS 200-10] Opening solution 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/pool_core_prj/solution1'.

INFO: [SYN 201-201] Setting up clock 'default' with a period of 10ns.

INFO: [HLS 200-10] Setting target device to 'xc7z020clg400-1'

INFO: [SYN 201-201] Setting up clock 'default' with a period of 10ns.

INFO: [SCHED 204-61] Option 'relax_ii_for_timing' is enabled, will increase II to preserve clock frequency constraints.

INFO: [HLS 200-10] Analyzing design file 'D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/pool_core/pool_core.cpp' ...

INFO: [HLS 200-111] Finished Linking Time (s): cpu = 00:00:00 ; elapsed = 00:00:04 . Memory (MB): peak = 102.391 ; gain = 17.629

INFO: [HLS 200-111] Finished Checking Pragmas Time (s): cpu = 00:00:00 ; elapsed = 00:00:04 . Memory (MB): peak = 102.391 ; gain = 17.629

INFO: [HLS 200-10] Starting code transformations ...

INFO: [HLS 200-111] Finished Standard Transforms Time (s): cpu = 00:00:00 ; elapsed = 00:00:05 . Memory (MB): peak = 117.102 ; gain = 32.340

INFO: [HLS 200-10] Checking synthesizability ...

INFO: [HLS 200-111] Finished Checking Synthesizability Time (s): cpu = 00:00:00 ; elapsed = 00:00:05 . Memory (MB): peak = 124.746 ; gain = 39.984

INFO: [HLS 200-111] Finished Pre-synthesis Time (s): cpu = 00:00:01 ; elapsed = 00:00:05 . Memory (MB): peak = 155.117 ; gain = 70.355

INFO: [HLS 200-111] Finished Architecture Synthesis Time (s): cpu = 00:00:01 ; elapsed = 00:00:05 . Memory (MB): peak = 156.988 ; gain = 72.227

INFO: [HLS 200-10] Starting hardware synthesis ...

INFO: [HLS 200-10] Synthesizing 'Pool' ...

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-42] -- Implementing module 'Pool'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [SCHED 204-11] Starting scheduling ...

WARNING: [SCHED 204-21] Estimated clock period (11.2658ns) exceeds the target (target clock period: 10ns, clock uncertainty: 1.25ns, effective delay budget: 8.75ns).

WARNING: [SCHED 204-21] The critical path in module 'Pool' consists of the following:

'mul' operation of DSP[123] ('ret.V', D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/pool_core/pool_core.cpp:45) [121] (3.36 ns)

'add' operation of DSP[123] ('ret.V', D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/pool_core/pool_core.cpp:45) [123] (3.02 ns)

'add' operation ('ret.V', D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/pool_core/pool_core.cpp:45) [124] (0 ns)

'add' operation ('feature_in2_sum', D:/master/projectzoo/PYNQ-Z2-traffic-signs-recognition-master/HLS/pool_core/pool_core.cpp:45) [125] (4.89 ns)

INFO: [SCHED 204-11] Finished scheduling.

INFO: [HLS 200-111] Elapsed time: 4.816 seconds; current allocated memory: 107.625 MB.

INFO: [HLS 200-434] Only 0 loops out of a total 5 loops have been pipelined in this design.

INFO: [BIND 205-100] Starting micro-architecture generation ...

INFO: [BIND 205-101] Performing variable lifetime analysis.

INFO: [BIND 205-101] Exploring resource sharing.

INFO: [BIND 205-101] Binding ...

INFO: [BIND 205-100] Finished micro-architecture generation.

INFO: [HLS 200-111] Elapsed time: 0.061 seconds; current allocated memory: 108.639 MB.

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [HLS 200-10] -- Generating RTL for module 'Pool'

INFO: [HLS 200-10] ----------------------------------------------------------------

INFO: [RTGEN 206-500] Setting interface mode on port 'Pool/gmem' to 'm_axi'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Pool/CHin_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Pool/Hin_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Pool/Win_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Pool/Kx_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Pool/Ky_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Pool/mode_V' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Pool/feature_in' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on port 'Pool/feature_out' to 's_axilite & ap_none'.

INFO: [RTGEN 206-500] Setting interface mode on function 'Pool' to 's_axilite & ap_ctrl_hs'.

INFO: [RTGEN 206-100] Bundling port 'return', 'CHin_V', 'Hin_V', 'Win_V', 'Kx_V', 'Ky_V', 'mode_V', 'feature_in' and 'feature_out' to AXI-Lite port AXILiteS.

INFO: [SYN 201-210] Renamed object name 'Pool_fadd_32ns_32ns_32_5_full_dsp_1' to 'Pool_fadd_32ns_32bkb' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Pool_fdiv_32ns_32ns_32_16_1' to 'Pool_fdiv_32ns_32cud' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Pool_uitofp_32ns_32_6_1' to 'Pool_uitofp_32ns_dEe' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Pool_fcmp_32ns_32ns_1_1_1' to 'Pool_fcmp_32ns_32eOg' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Pool_udiv_16ns_8ns_16_20_seq_1' to 'Pool_udiv_16ns_8nfYi' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Pool_mul_mul_16s_16ns_32_1_1' to 'Pool_mul_mul_16s_g8j' due to the length limit 20

INFO: [SYN 201-210] Renamed object name 'Pool_mac_muladd_16ns_16s_48ns_48_1_1' to 'Pool_mac_muladd_1hbi' due to the length limit 20

INFO: [RTGEN 206-100] Generating core module 'Pool_fadd_32ns_32bkb': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Pool_fcmp_32ns_32eOg': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Pool_fdiv_32ns_32cud': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Pool_mac_muladd_1hbi': 3 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Pool_mul_mul_16s_g8j': 1 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Pool_udiv_16ns_8nfYi': 2 instance(s).

INFO: [RTGEN 206-100] Generating core module 'Pool_uitofp_32ns_dEe': 1 instance(s).

INFO: [RTGEN 206-100] Finished creating RTL model for 'Pool'.

INFO: [HLS 200-111] Elapsed time: 0.11 seconds; current allocated memory: 110.569 MB.

INFO: [RTMG 210-282] Generating pipelined core: 'Pool_udiv_16ns_8nfYi_div'

INFO: [HLS 200-111] Finished generating all RTL models Time (s): cpu = 00:00:01 ; elapsed = 00:00:06 . Memory (MB): peak = 166.703 ; gain = 81.941

INFO: [SYSC 207-301] Generating SystemC RTL for Pool.

INFO: [VHDL 208-304] Generating VHDL RTL for Pool.

INFO: [VLOG 209-307] Generating Verilog RTL for Pool.

INFO: [HLS 200-112] Total elapsed time: 6.045 seconds; peak allocated memory: 110.569 MB.

Finished C synthesis.

Starting export RTL ...

D:/Xilinx/Vivado/2018.3/bin/vivado_hls.bat C:/Users/admin/AppData/Roaming/Xilinx/Vivado/pool_core_prj/solution1/export.tcl

INFO: Applying HLS Y2K22 patch v1.2 for IP revision

INFO: [HLS 200-10] Running 'D:/Xilinx/Vivado/2018.3/bin/unwrapped/win64.o/vivado_hls.exe'

INFO: [HLS 200-10] For user 'admin' on host 'desktop-jd0ieba' (Windows NT_amd64 version 6.2) on Tue Dec 30 15:34:24 +0800 2025

INFO: [HLS 200-10] In directory 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado'

INFO: [HLS 200-10] Opening project 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/pool_core_prj'.

INFO: [HLS 200-10] Opening solution 'C:/Users/admin/AppData/Roaming/Xilinx/Vivado/pool_core_prj/solution1'.

INFO: [SYN 201-201] Setting up clock 'default' with a period of 10ns.

INFO: [HLS 200-10] Setting target device to 'xc7z020clg400-1'

INFO: [IMPL 213-8] Exporting RTL as a Vivado IP.

****** Vivado v2018.3 (64-bit)

**** SW Build 2405991 on Thu Dec 6 23:38:27 MST 2018

**** IP Build 2404404 on Fri Dec 7 01:43:56 MST 2018

** Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.

source run_ippack.tcl -notrace

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository 'D:/Xilinx/Vivado/2018.3/data/ip'.

WARNING: [IP_Flow 19-4832] The IP name 'Pool_ap_fadd_3_full_dsp_32' you have specified is long. The Windows operating system has path length limitations. It is recommended you use shorter names to reduce the likelihood of issues.

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'Pool_ap_fadd_3_full_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'Pool_ap_fadd_3_full_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'Pool_ap_fcmp_0_no_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'Pool_ap_fcmp_0_no_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'Pool_ap_fdiv_14_no_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'Pool_ap_fdiv_14_no_dsp_32'...

WARNING: [IP_Flow 19-4832] The IP name 'Pool_ap_uitofp_4_no_dsp_32' you have specified is long. The Windows operating system has path length limitations. It is recommended you use shorter names to reduce the likelihood of issues.

INFO: [IP_Flow 19-1686] Generating 'Synthesis' target for IP 'Pool_ap_uitofp_4_no_dsp_32'...

INFO: [IP_Flow 19-1686] Generating 'Simulation' target for IP 'Pool_ap_uitofp_4_no_dsp_32'...

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository 'D:/Xilinx/Vivado/2018.3/data/ip'.

INFO: [Common 17-206] Exiting Vivado at Tue Dec 30 15:34:31 2025...

Finished export RTL.完成以上两个步骤后,你将获得两个 IP 核(通常位于工程目录的 solution1/impl/ip 下),接下来的工作就是在 Vivado 中将它们连接起来。

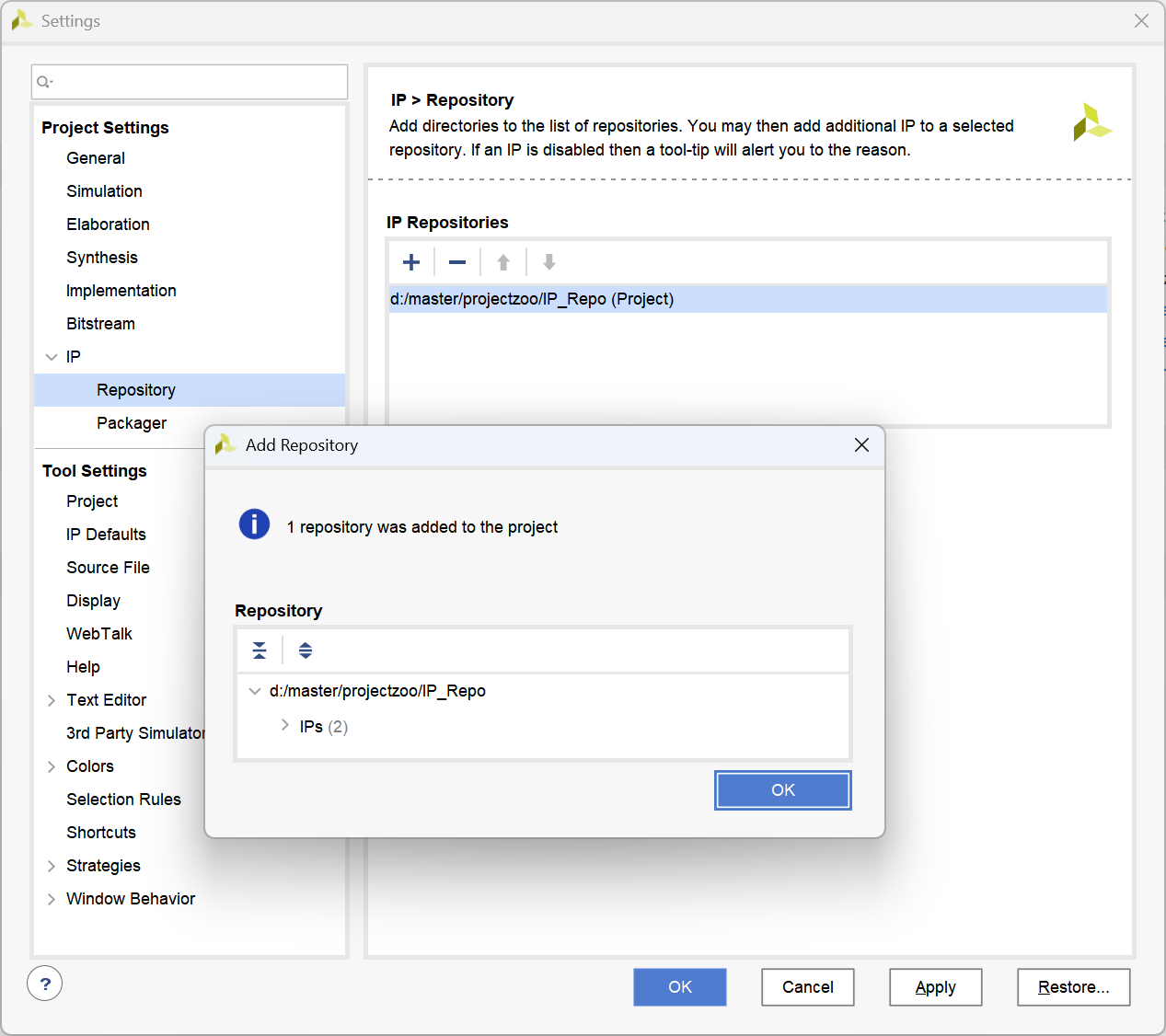

根据我的日志,我的IP核放在这个目录Loaded Vivado IP repository 'D:/Xilinx/Vivado/2018.3/data/ip'

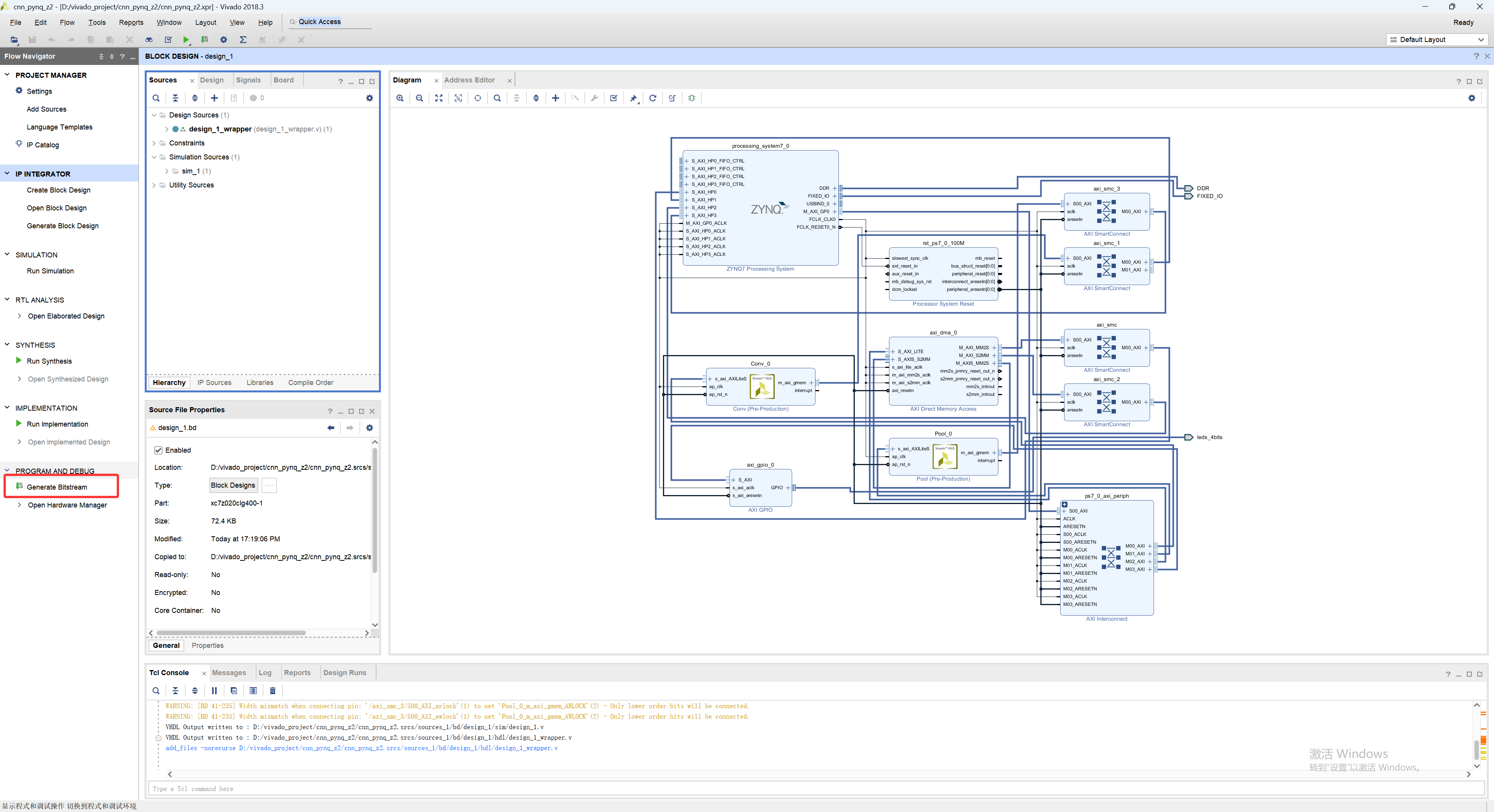

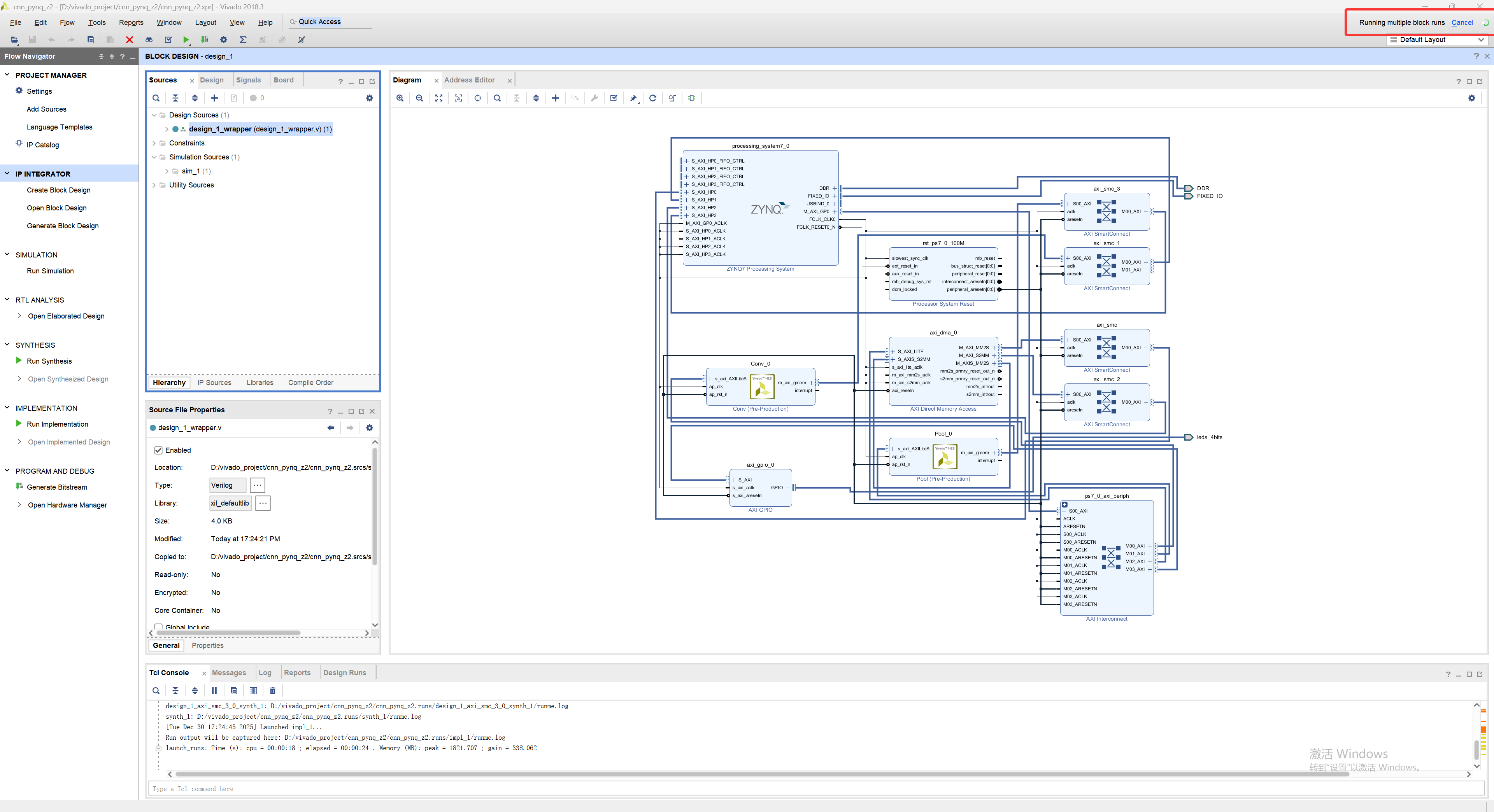

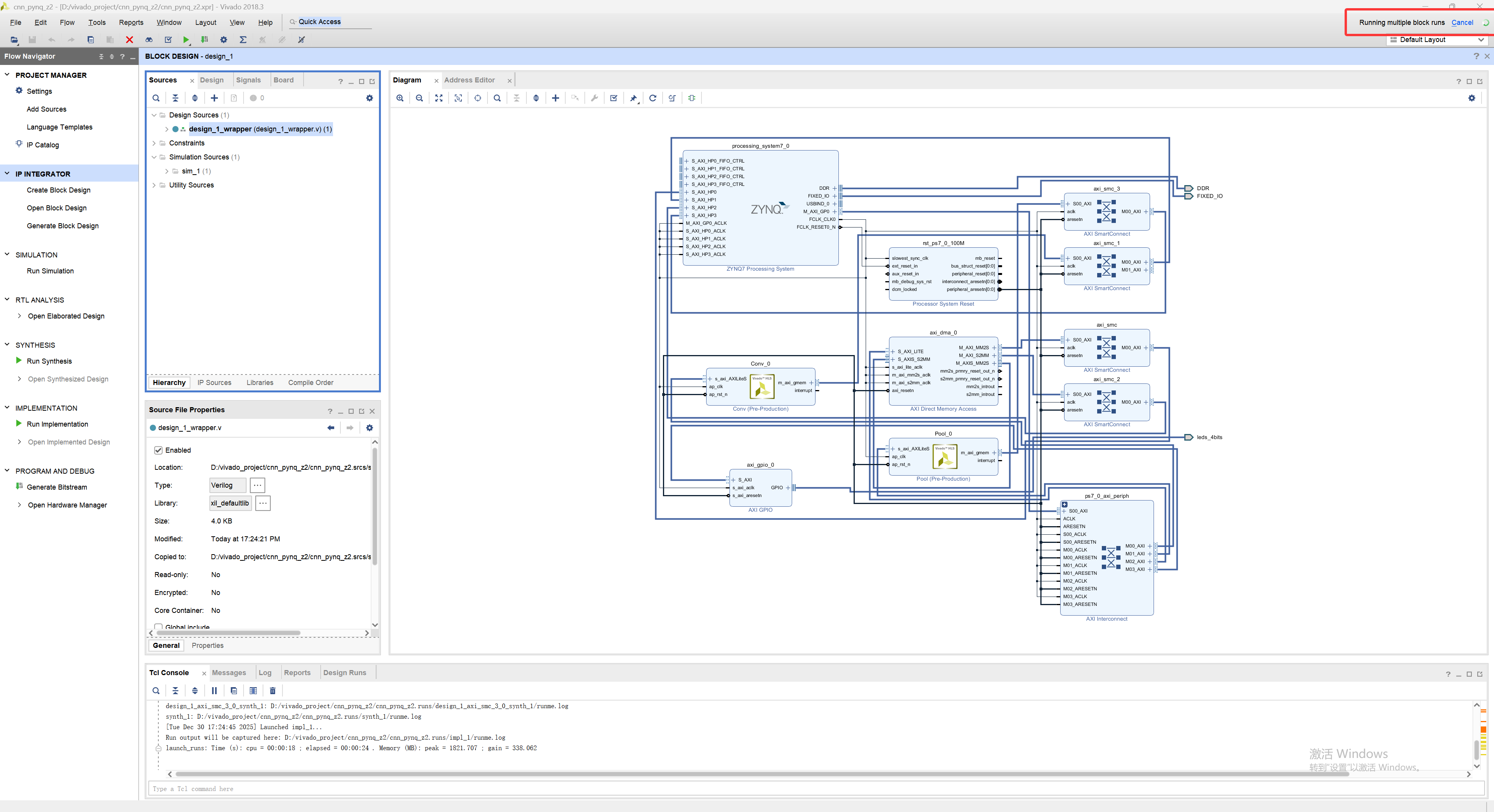

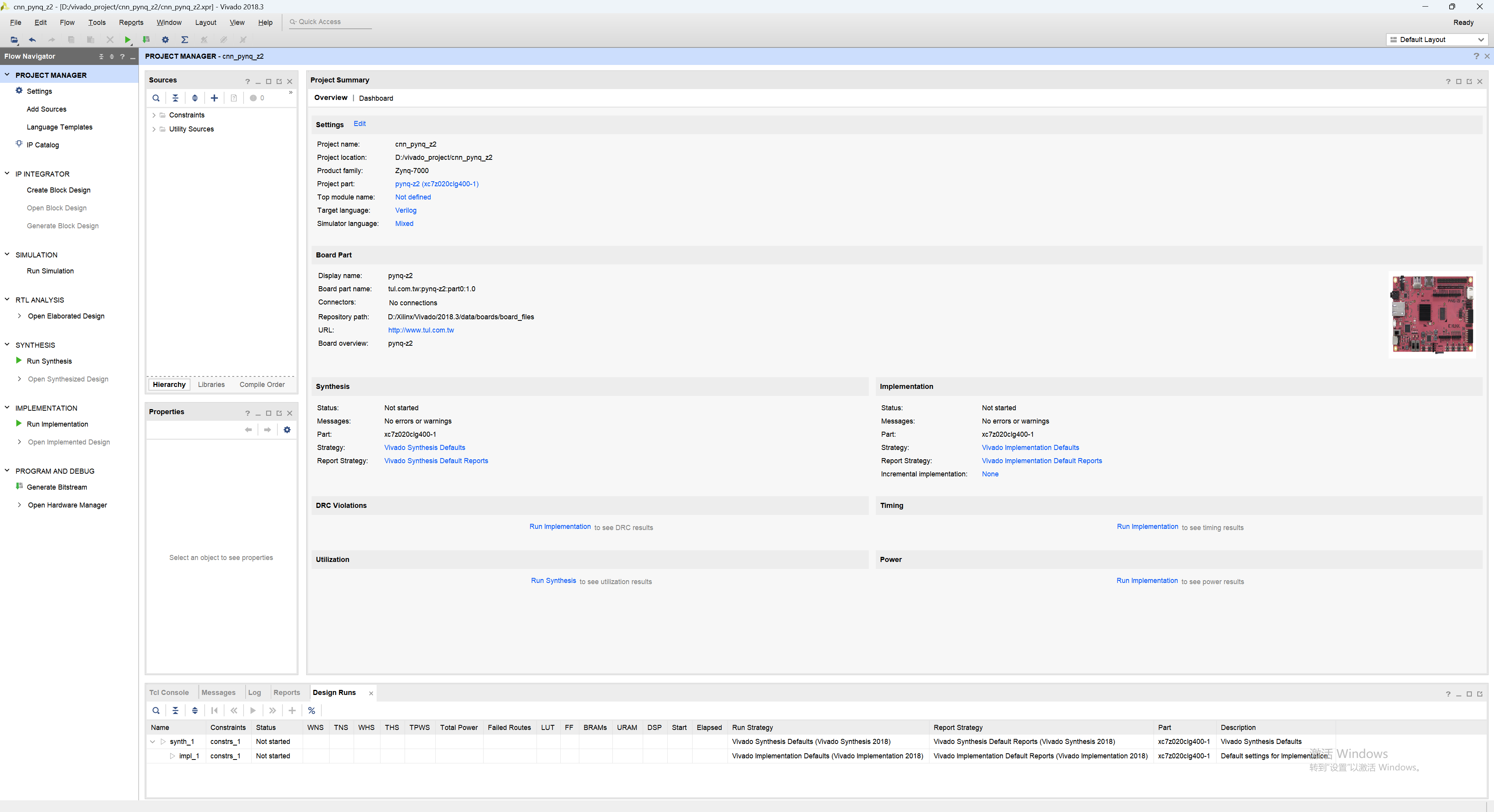

03 把所有"零件"(IP 核)都导入到了 Vivado

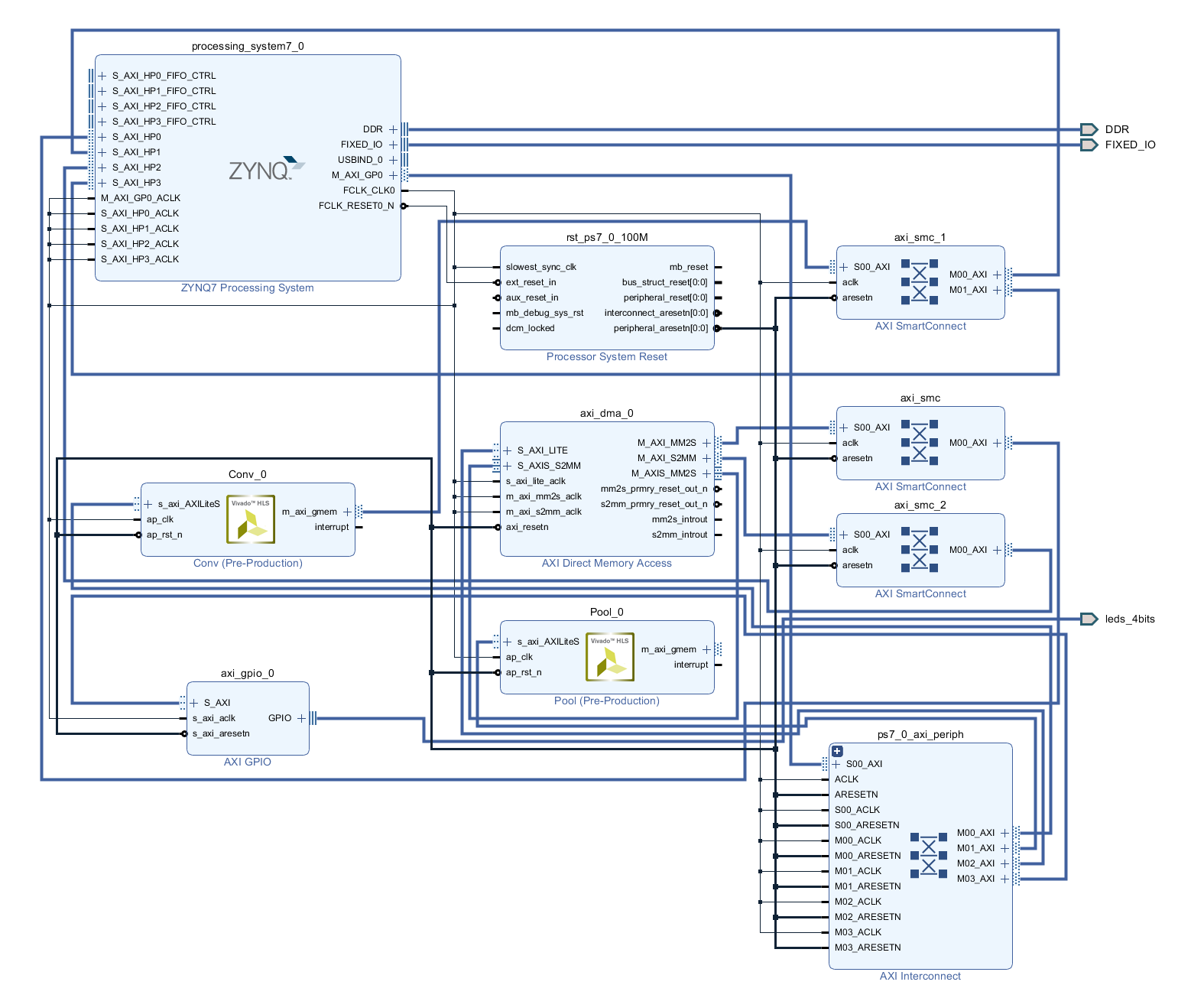

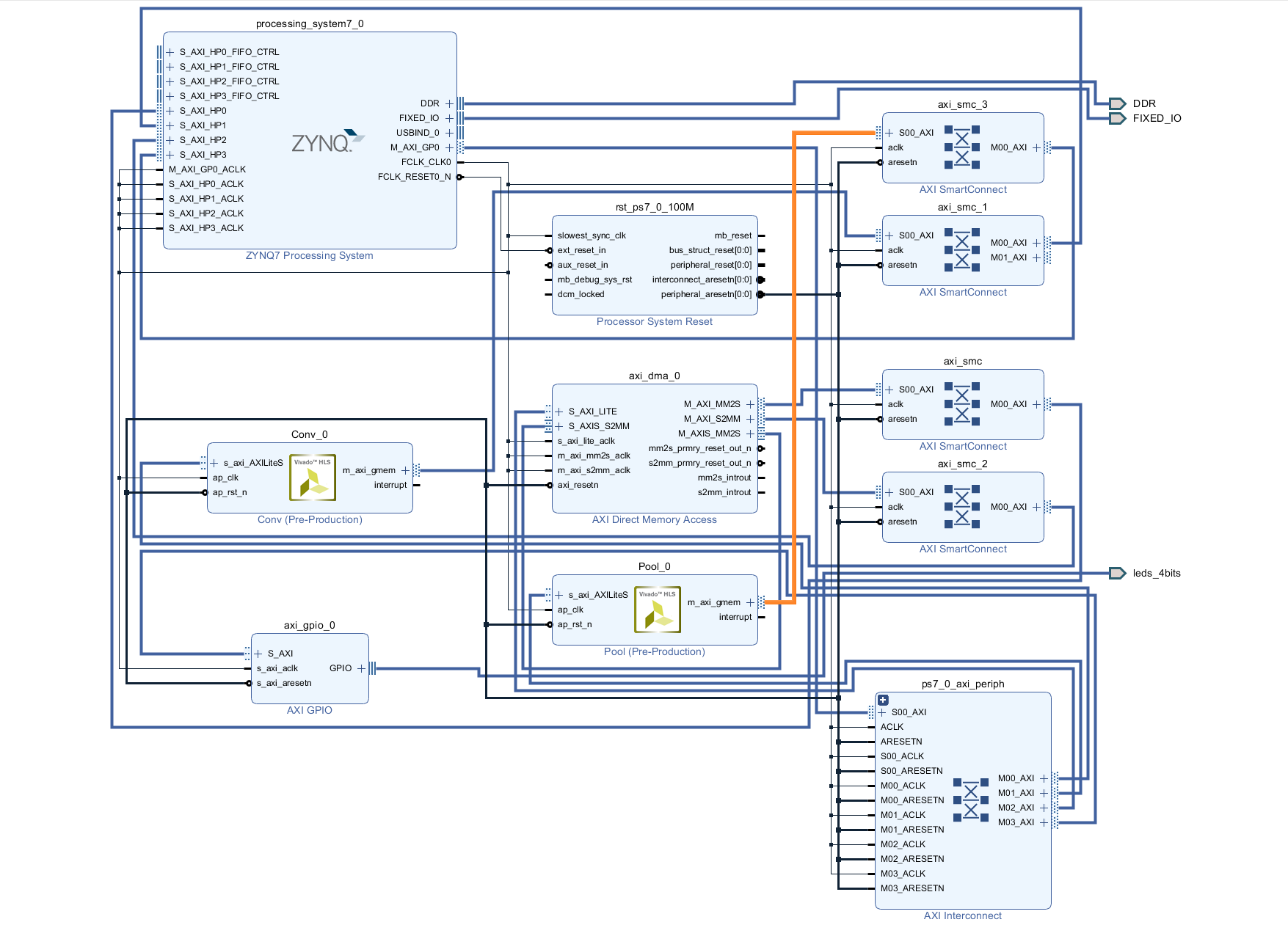

04 Vivado 里把这些 IP 核连起来

太棒了!既然你已经把所有"零件"(IP 核)都导入到了 Vivado,现在我们就进入最关键的组装环节(Block Design)。

我们需要在 Vivado 里把这些 IP 核连起来,让 CPU (PS端) 能控制它们,同时让它们能高速访问内存 (DDR)。

请按照以下详细步骤操作:

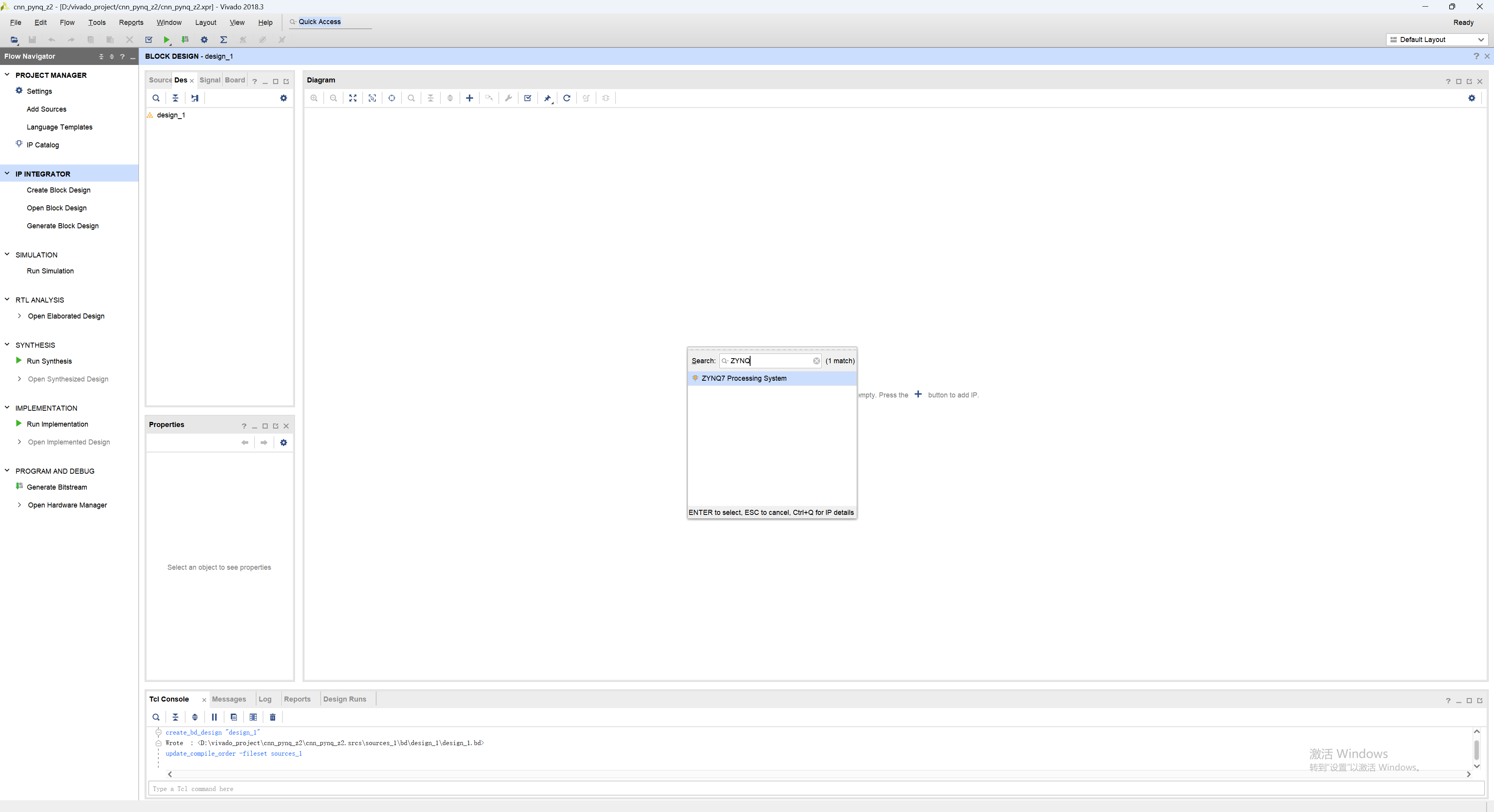

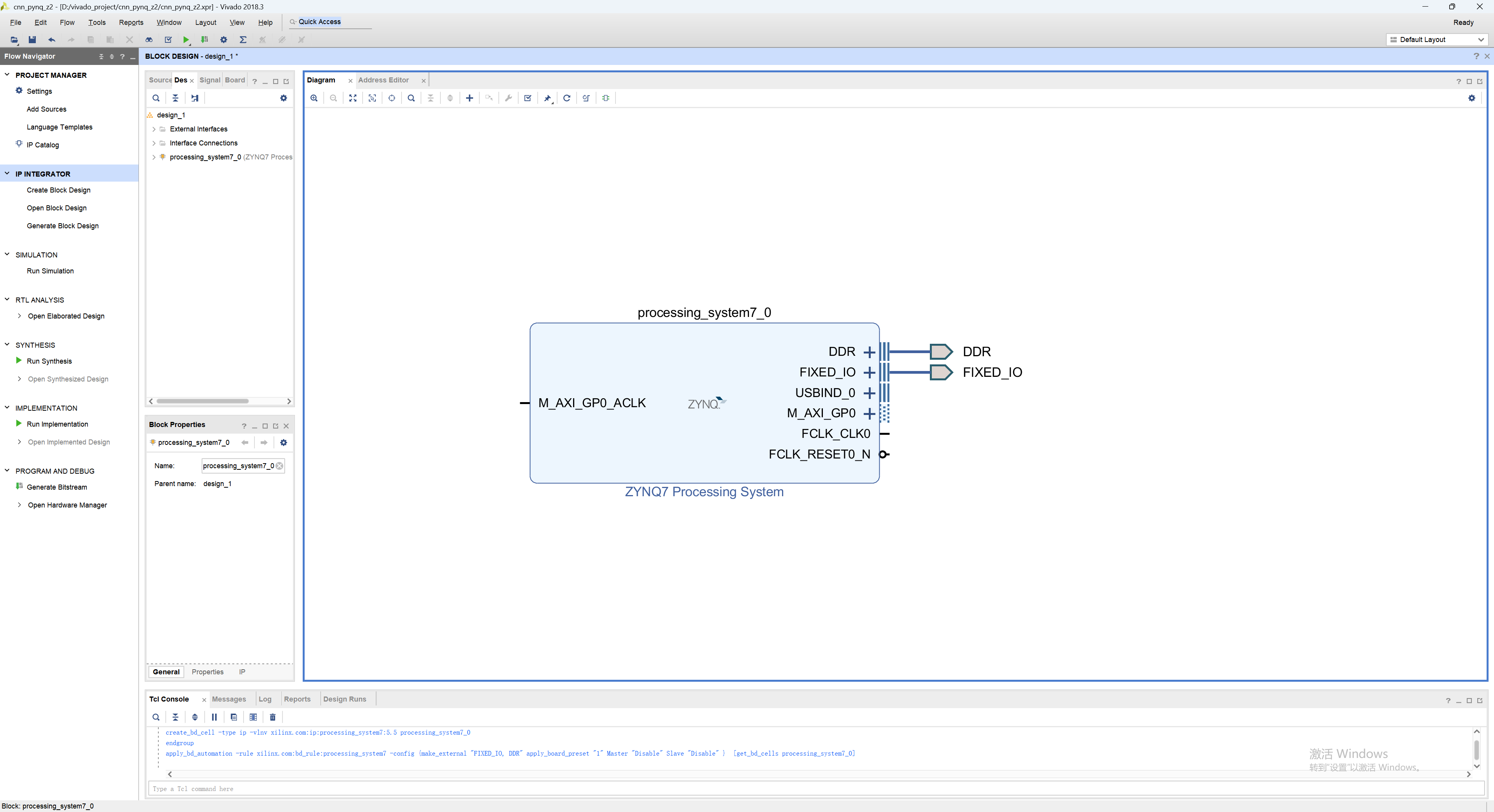

第一步:创建 Block Design

- 在 Vivado 左侧导航栏 (Flow Navigator) 中,点击 Create Block Design。

- 弹出的框里,名字可以默认叫

design_1,点击 OK。 - 你会看到一个空白的画布。

第二步:添加并配置 ZYNQ (大脑)

-

添加 IP :在画布空白处右键 -> Add IP ,搜索

ZYNQ,选择 ZYNQ7 Processing System 。

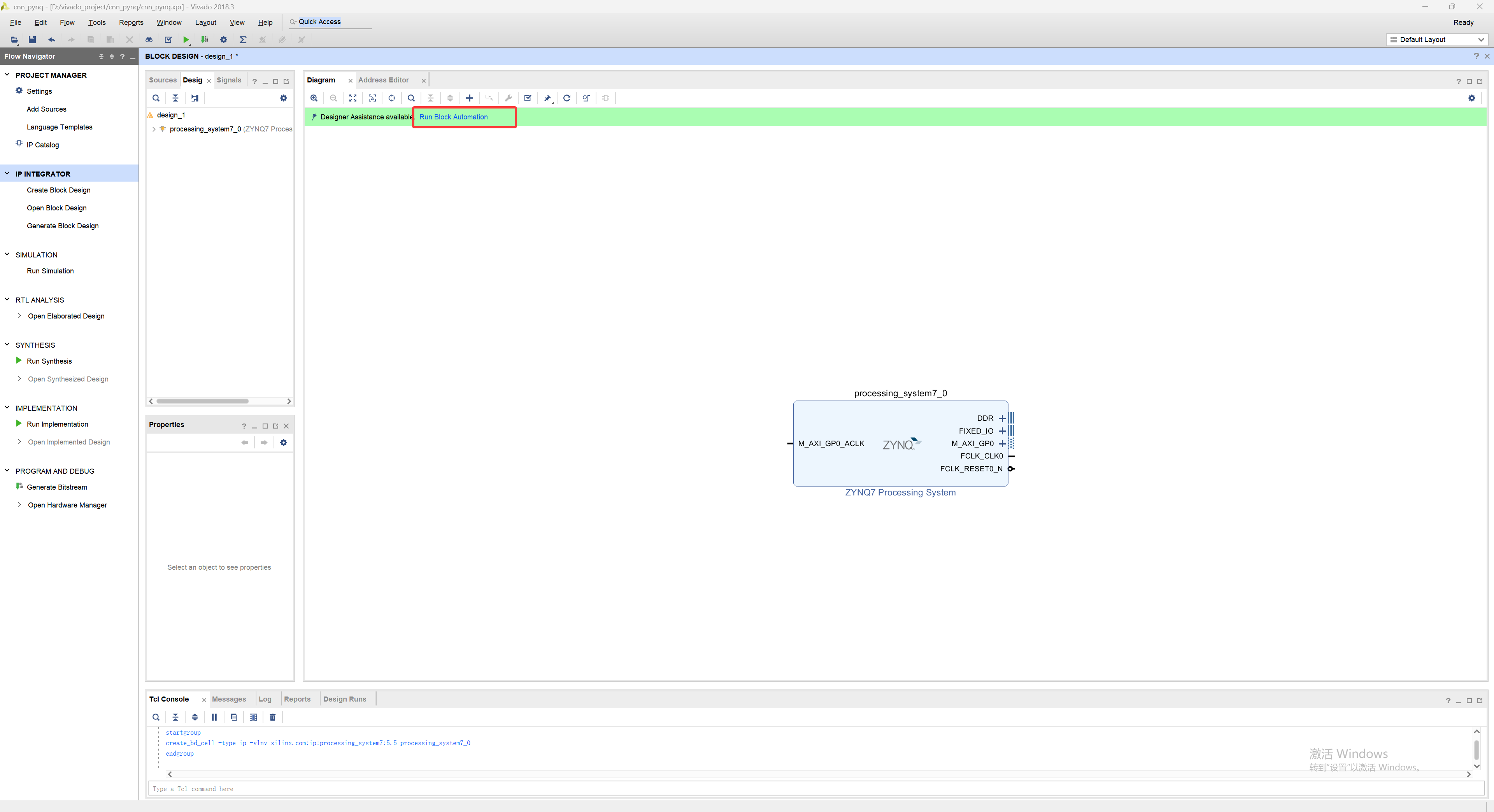

-

自动配置:

- 页面顶部会出现一个绿色横条 "Designer Assistance available. Run Block Automation"。

- 点击 Run Block Automation。

- 弹出的窗口保持默认(确保 Apply Board Preset 勾选了 PYNQ-Z2),点击 OK。

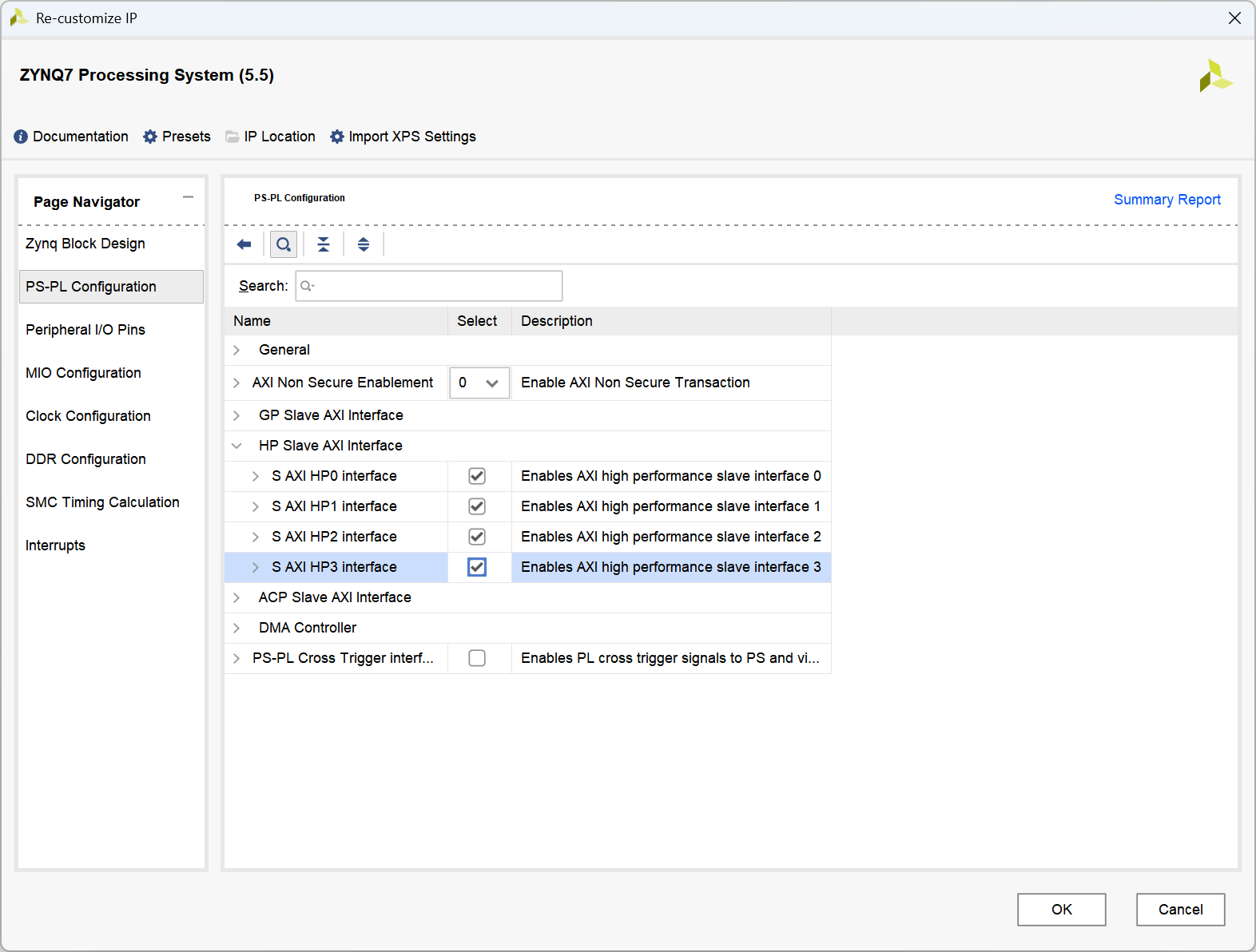

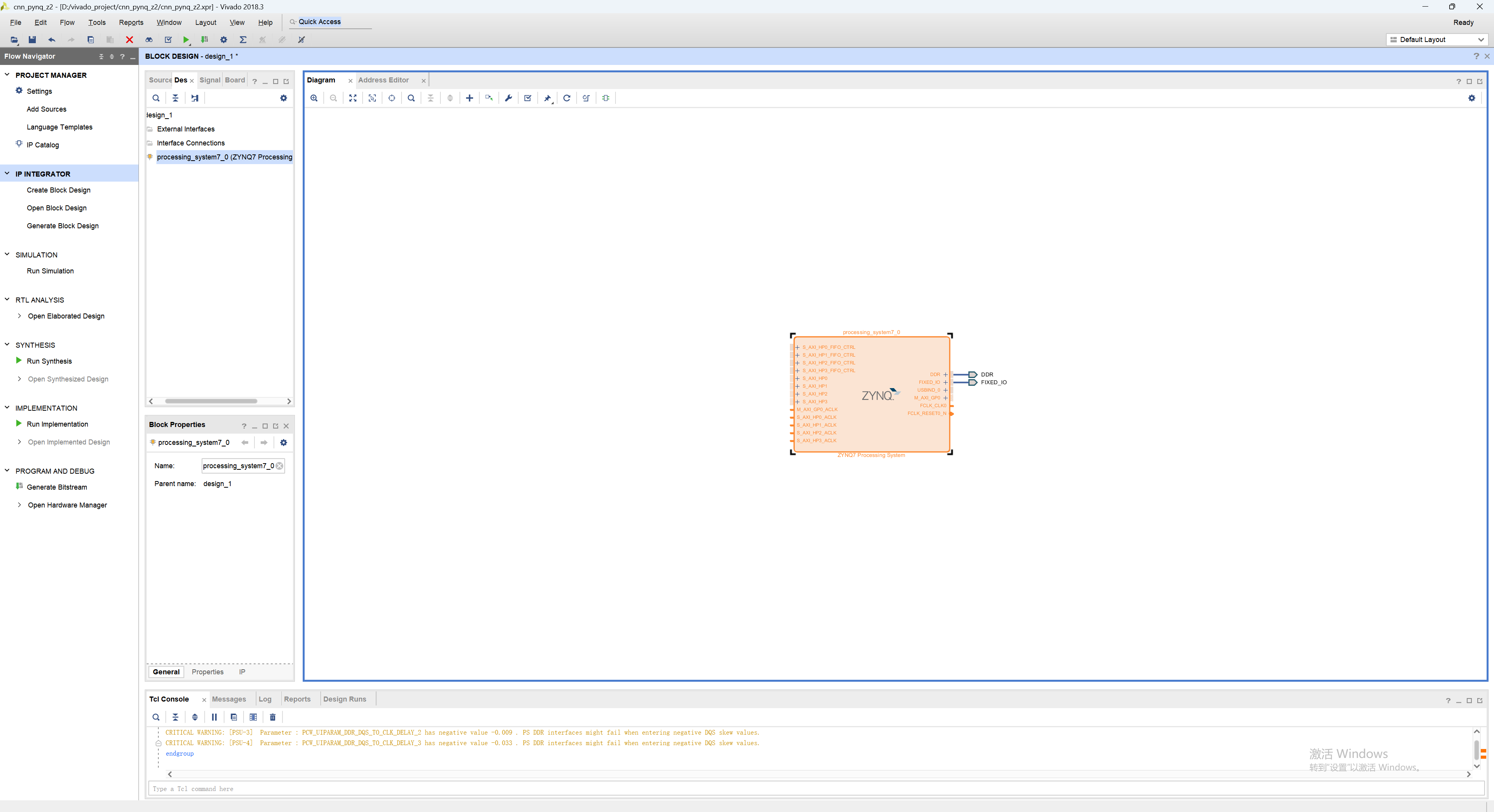

- 手动修改配置 (关键!):

- 双击 ZYNQ 图标进入设置。

- 在左侧菜单选 PS-PL Configuration。

- 展开 HP Slave AXI Interface。

- 勾选 HP0, HP1, HP2, HP3(把这四个全都勾上)。

- 原理:我们需要多条高速公路,让卷积、池化和 DMA 同时读写内存而不堵车。

- 点击 OK 保存。

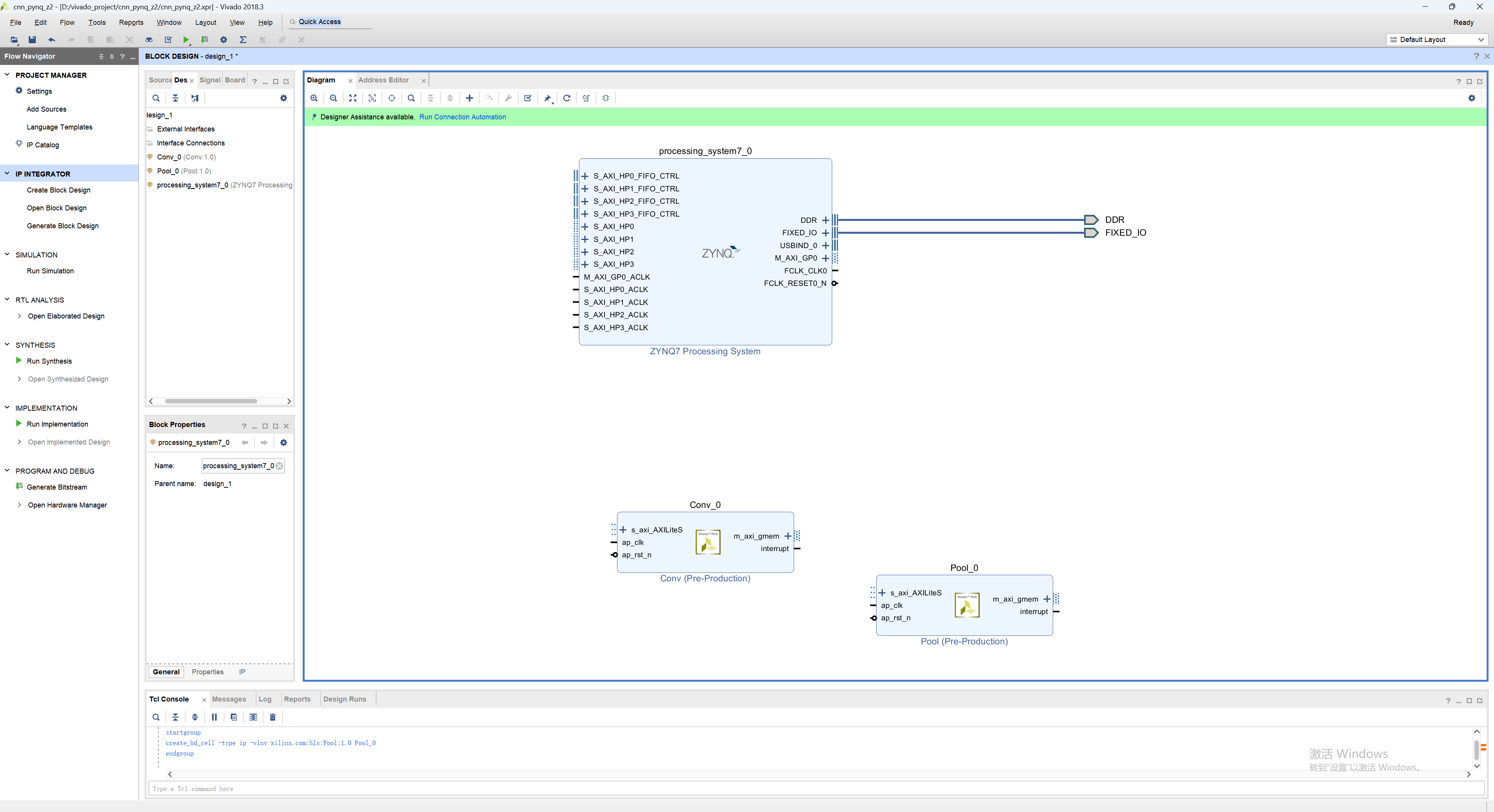

第三步:添加我们的加速器 (Conv & Pool)

- 添加 Conv :右键 Add IP,搜索

Conv,选中你刚才导入的ConvIP。 - 添加 Pool :右键 Add IP,搜索

Pool,选中PoolIP。

- 注意:你会发现它们身上都有

m_axi_gmem(读写内存用) 和s_axi_AXILiteS(CPU控制用) 接口。

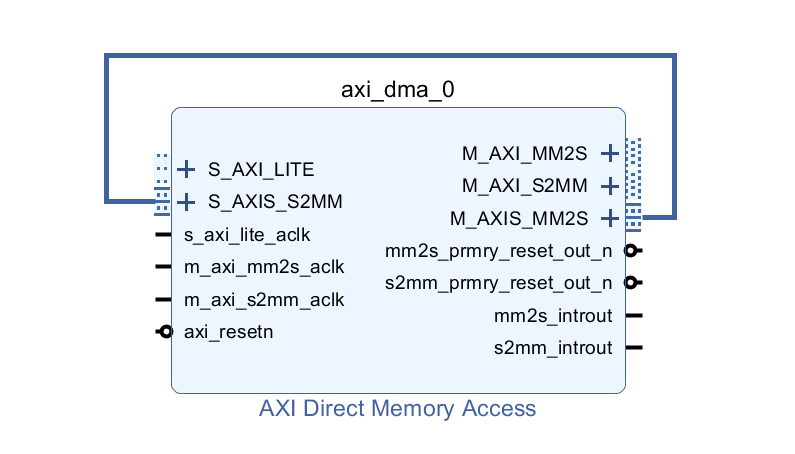

第四步:添加辅助 IP (DMA & GPIO)

根据原项目的设计,我们还需要两个辅助 IP:

- 添加 AXI DMA:

- 搜索并添加

AXI Direct Memory Access。 - 双击配置 :取消勾选 Enable Scatter Gather Engine (我们不需要这个复杂功能)。保持默认的 Simple DMA 模式。点击 OK。

- 特殊连线 (Loopback) :原项目做了一个回环测试设计。请在 DMA 模块上,把

M_AXIS_MM2S接口直接连到自己的S_AXIS_S2MM接口上(用鼠标拖过去连上)。

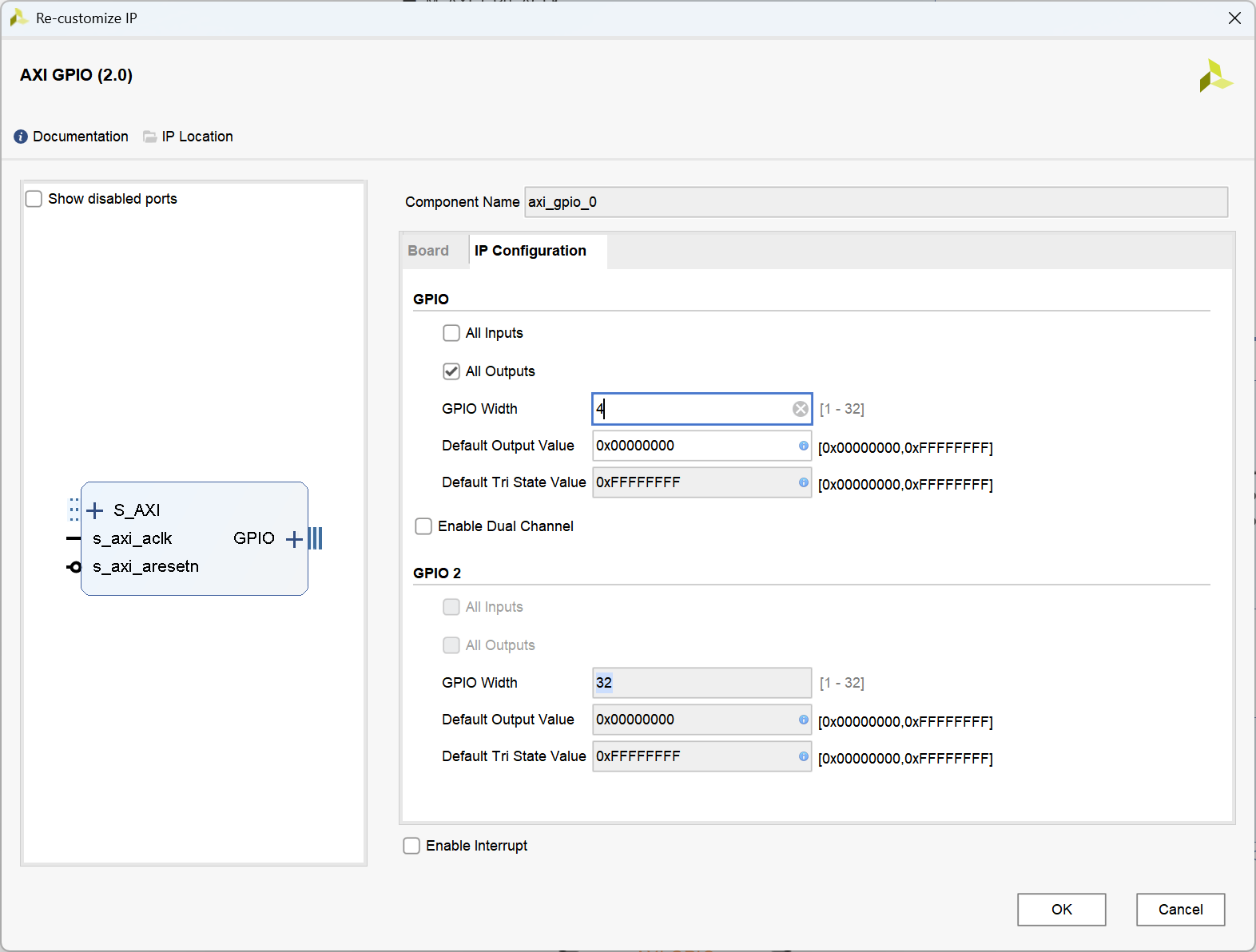

- 添加 AXI GPIO (可选,用于控制板载 LED):

- 搜索并添加

AXI GPIO。 - 双击配置:勾选 All Outputs ,GPIO Width 设为 4。点击 OK。

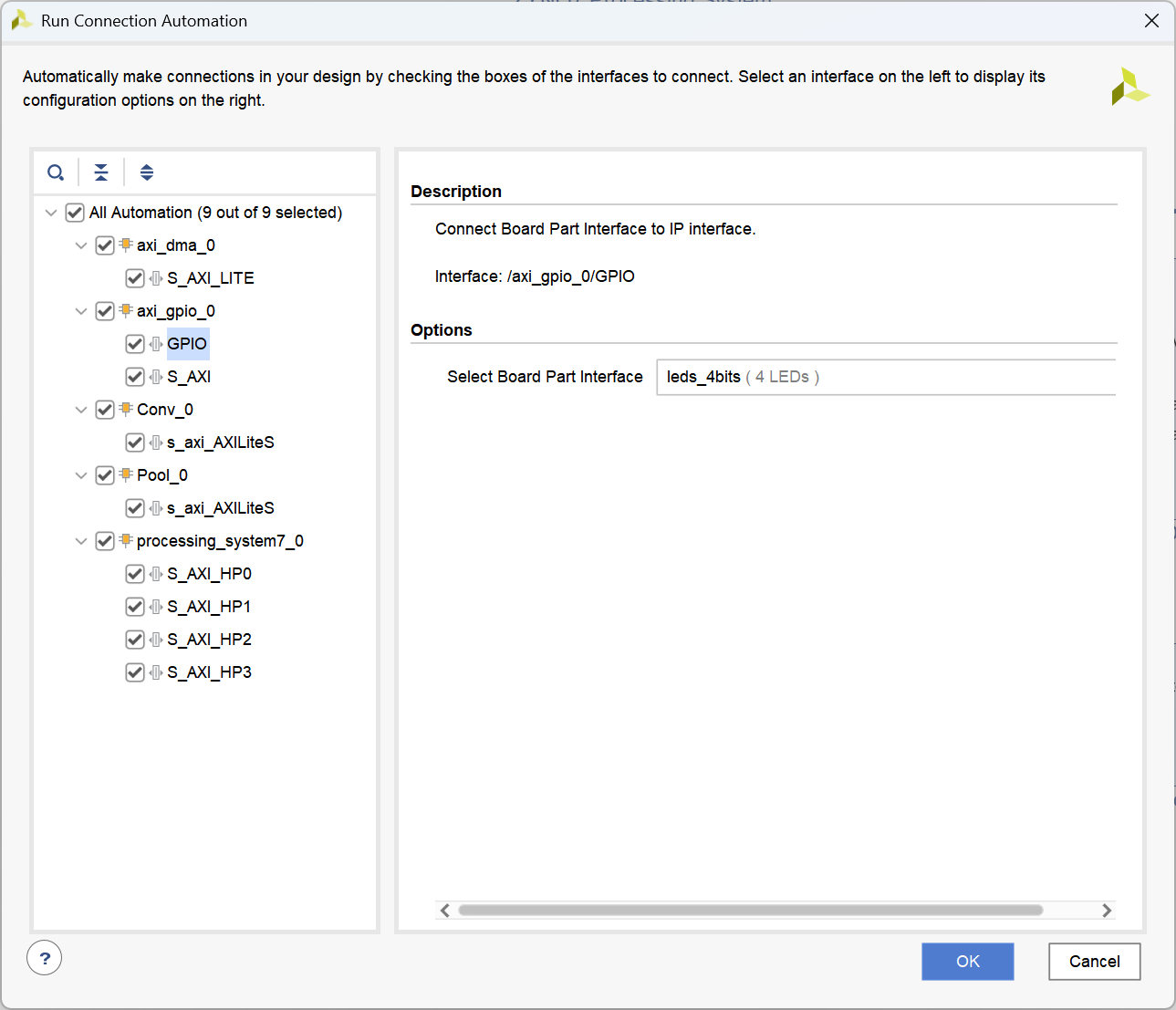

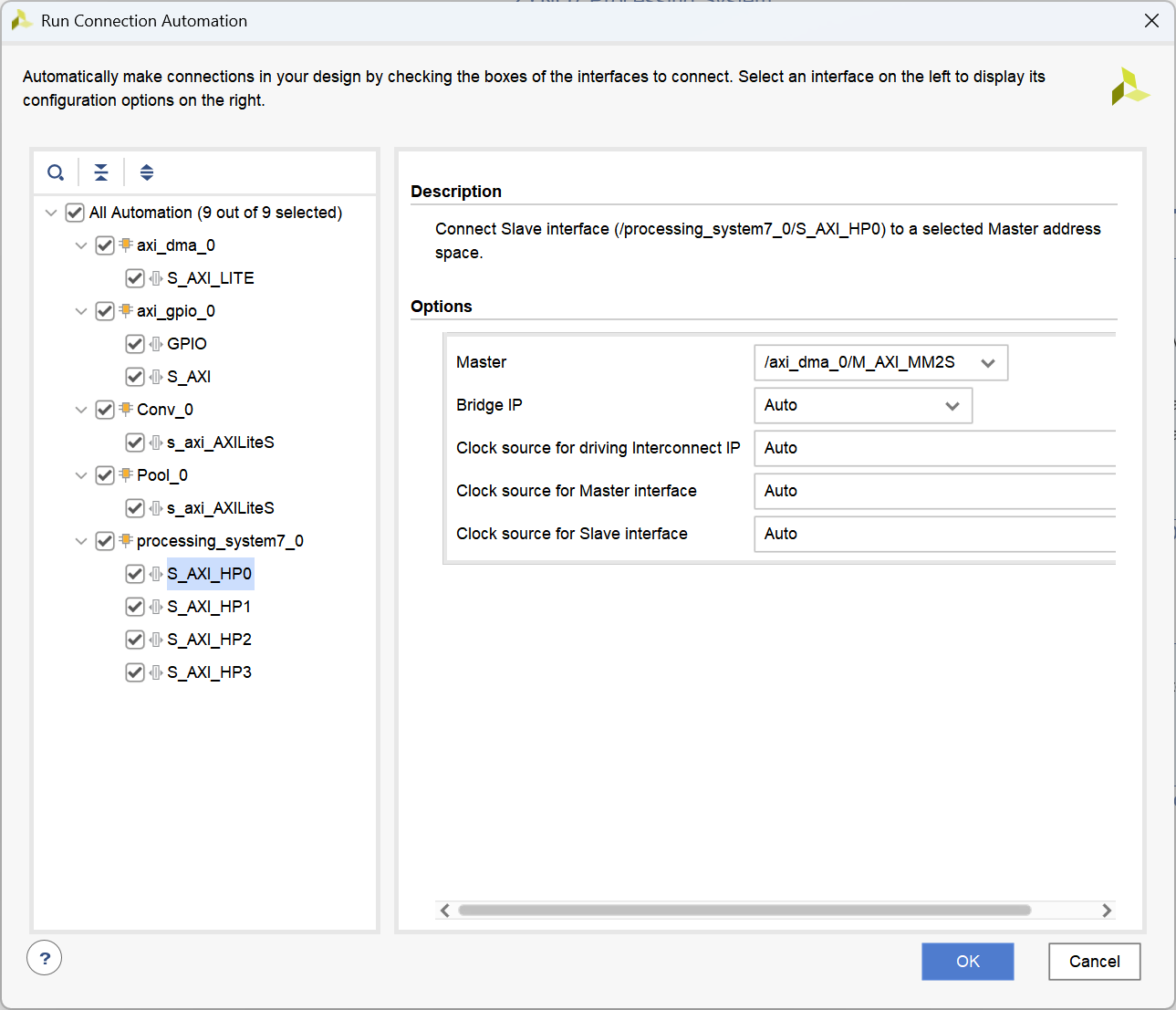

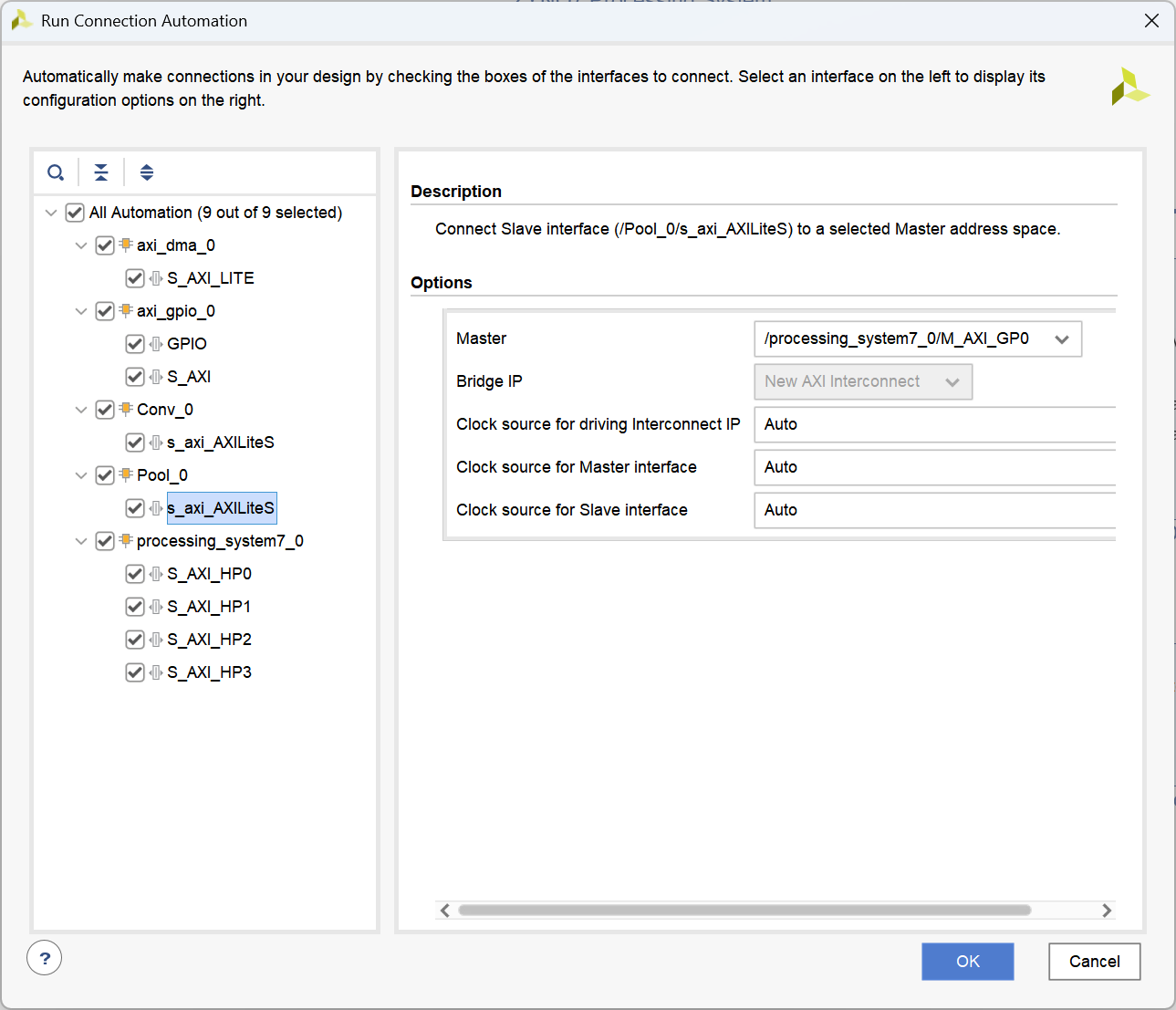

第五步:自动连线 (魔法时刻)

现在画布上有一堆散乱的模块,我们要用 Vivado 强大的自动连线功能。

- 页面顶部会出现绿色横条 "Run Connection Automation"。点击它。

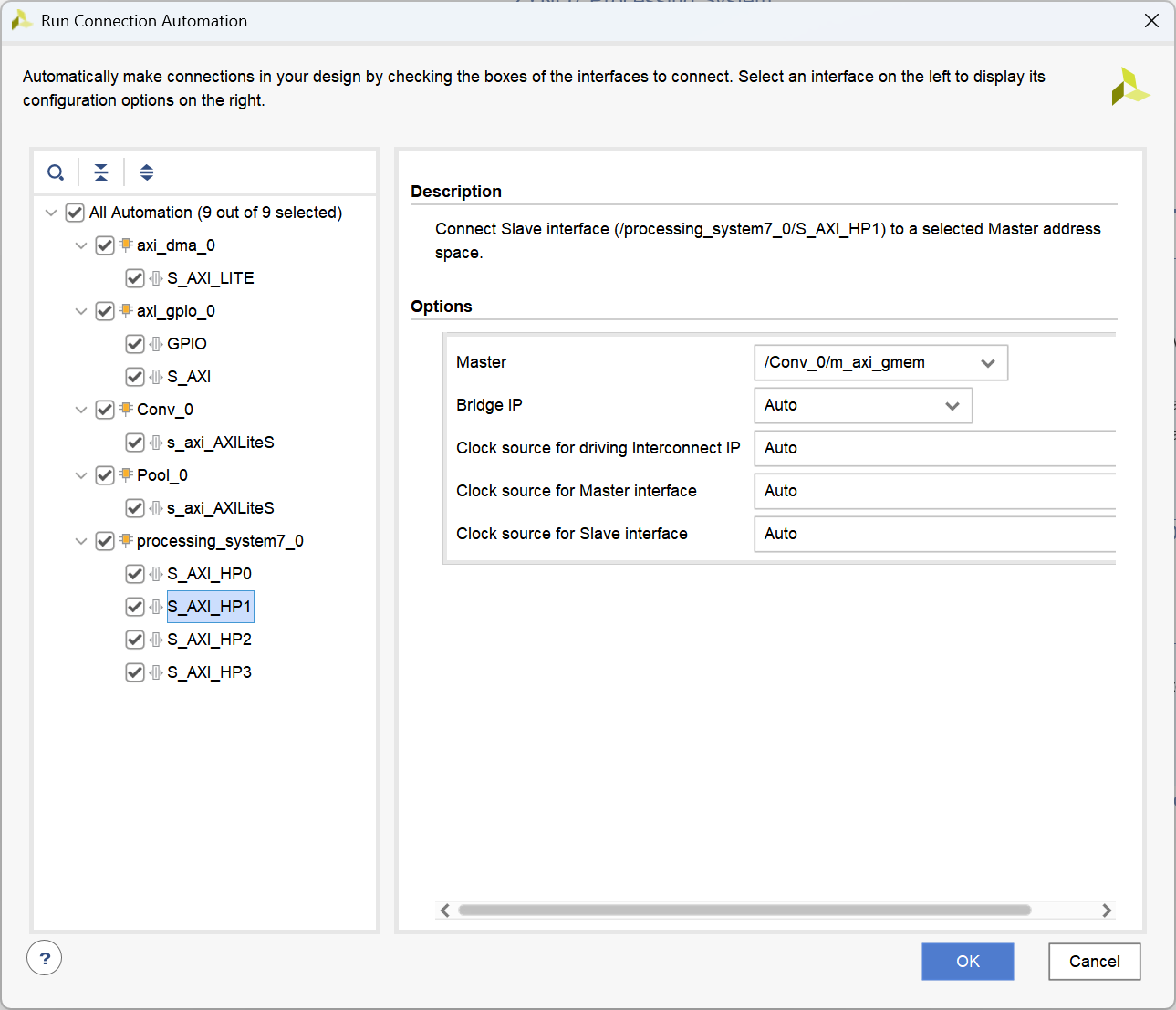

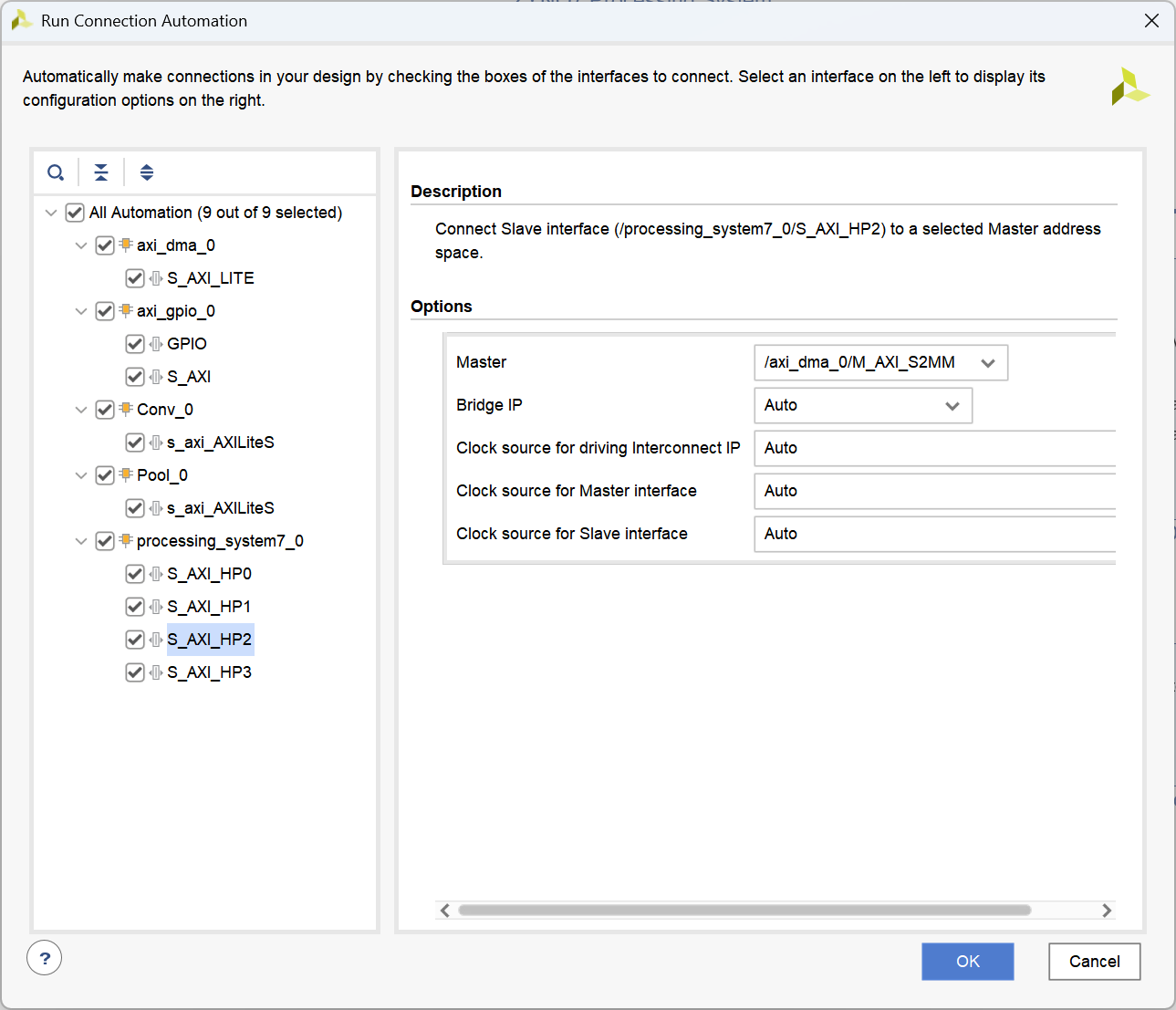

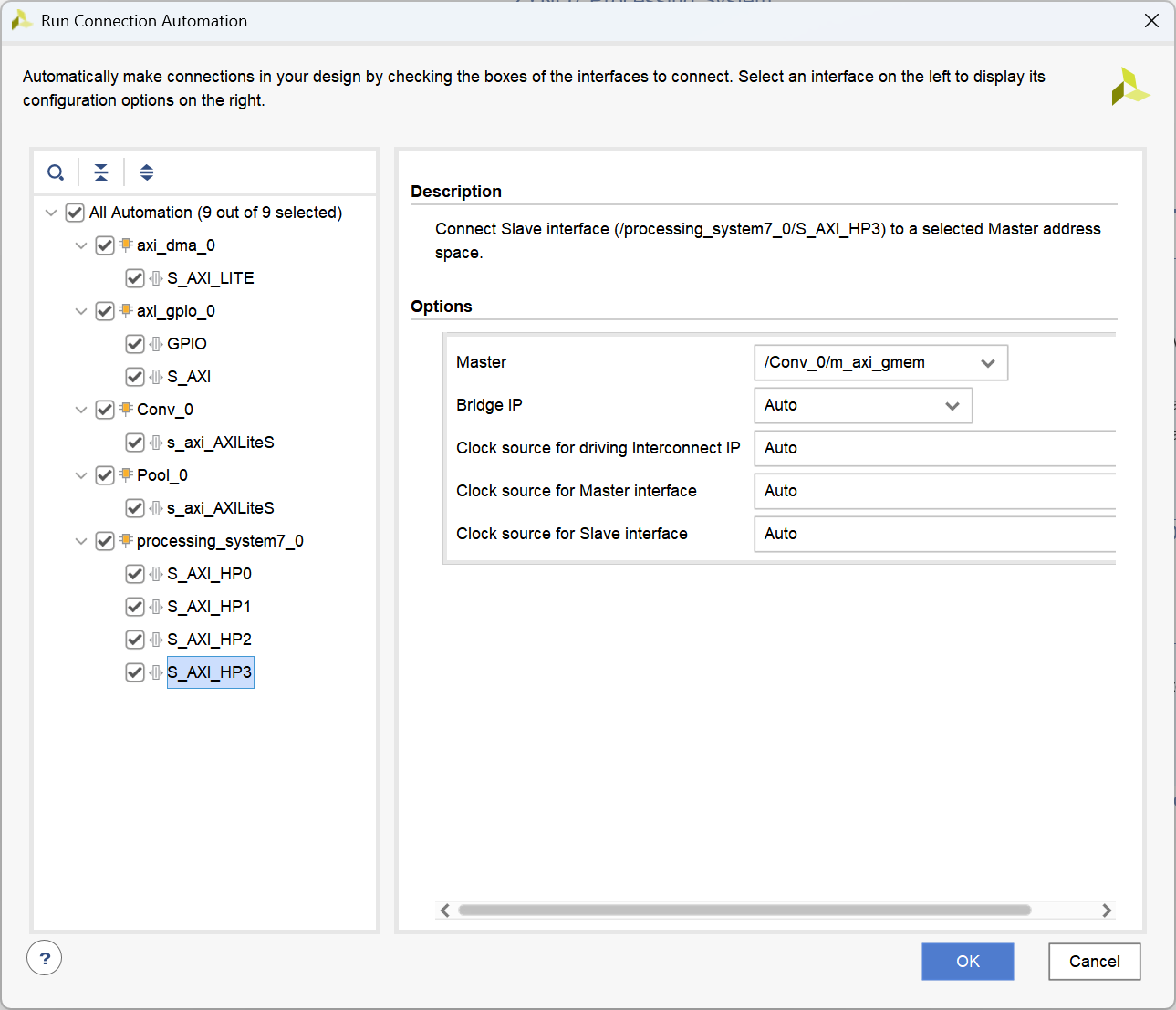

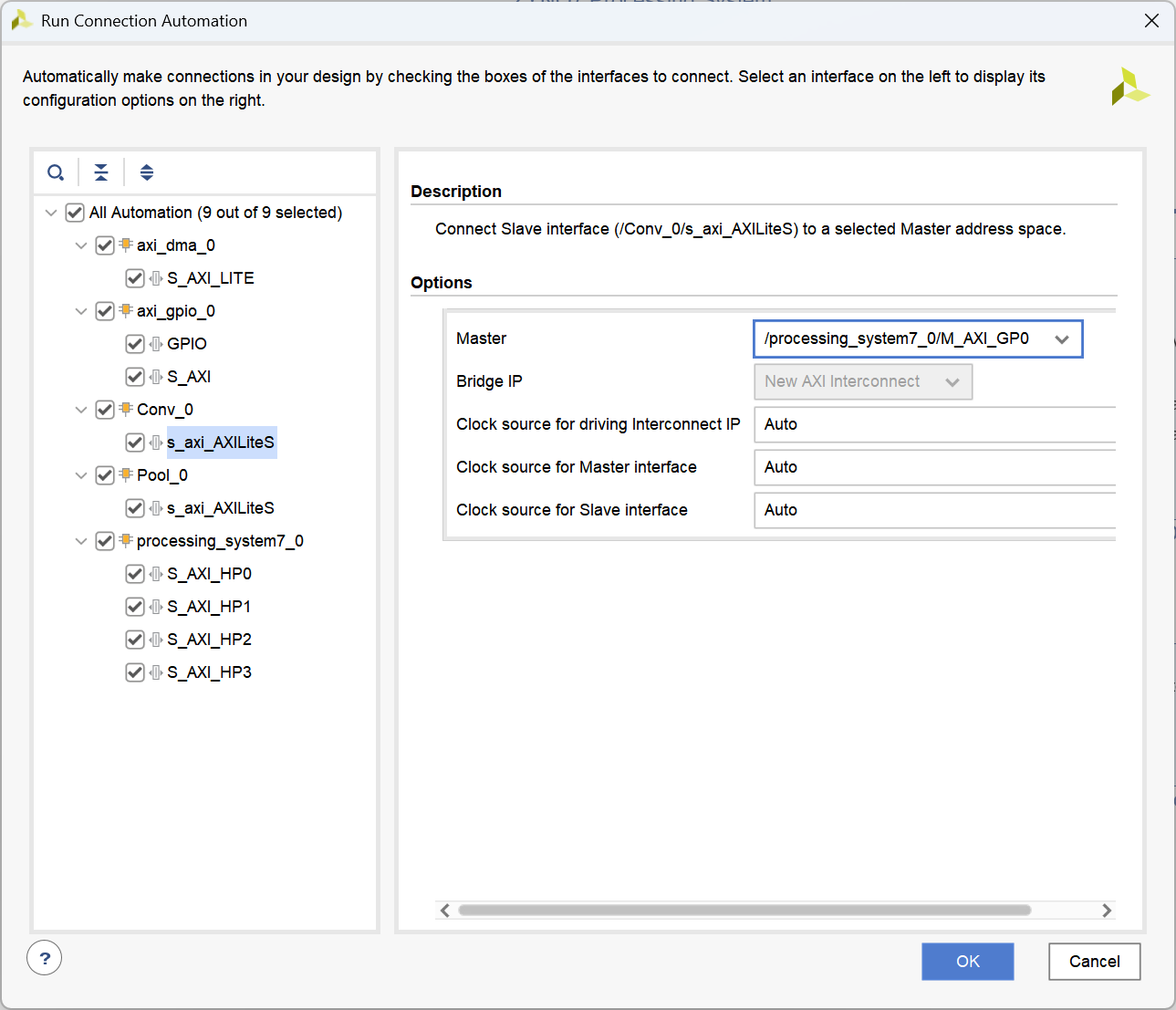

- 在弹出的窗口左侧,你会看到很多接口需要连接。不要直接点 OK,我们需要微调一下分配:

- 目标:把不同的 Master 分配到不同的 HP 端口,分散负载。

- 找到

Conv_0 / m_axi_gmem:在右侧选项里,把 "Master Interface" 对应的目标端口选为/processing_system7_0/S_AXI_HP1(或者 HP0/HP2/HP3 任意一个,尽量不重复)。 - 找到

Pool_0 / m_axi_gmem:目标选为/processing_system7_0/S_AXI_HP3。 - 找到

axi_dma_0 / M_AXI_MM2S:目标选为/processing_system7_0/S_AXI_HP0。 - 找到

axi_dma_0 / M_AXI_S2MM:目标选为/processing_system7_0/S_AXI_HP2。 - 其他的

s_axi_...接口(控制信号):保持默认,Vivado 会自动把它们连到 ZYNQ 的M_AXI_GP0。 GPIO接口:选择leds_4bits(如果有板卡预设) 或者Custom(如果不确定就选 Custom,之后手动把引脚引出,叫leds)。

- 点击 OK。

- Vivado 会自动添加

AXI Interconnect和Processor System Reset模块,并把线全部连好。等待进度条跑完。

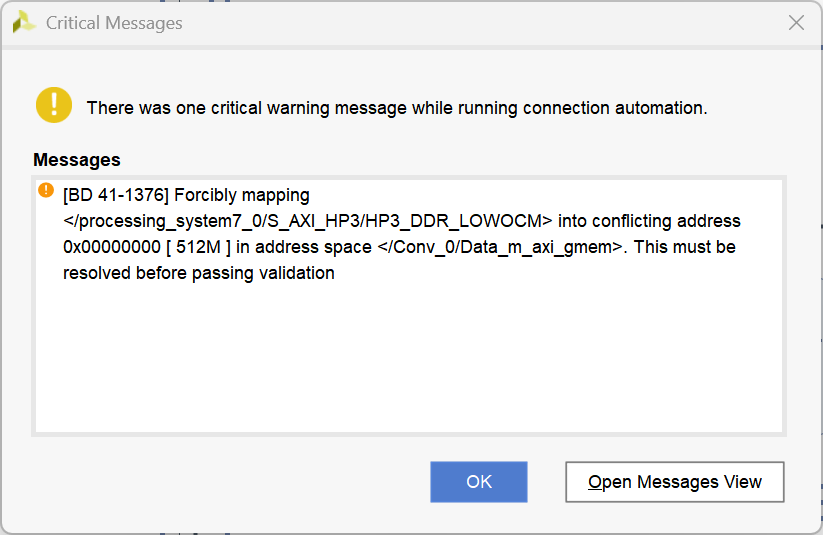

报错:

这是一个严重警告 (Critical Warning) ,但别慌,这在 Vivado 自动连线时非常常见。

错误分析

报错信息的核心是:

[BD 41-1376] Forcibly mapping ... HP3 ... in address space </Conv_0...>

这句话的意思是:你的 Conv_0(卷积核)正在试图通过 HP3 接口访问内存,并且在这个过程中发生了地址冲突(抢占了地址 0x00000000)。

这暗示了一个连接错误:

根据我们之前的规划:

Conv_0应该连 HP1。Pool_0应该连 HP3。

报错显示 Conv_0 出现在了 HP3 的地盘上,这说明**刚才在配置 S_AXI_HP3 时,你可能误选了 Conv_0,而不是 Pool_0**。这样导致 Conv_0 可能同时连了两个口(或者连错了口),从而引发冲突。

解决方法 (三步走)

请按顺序执行以下操作,一定能修好:

第一步:物理断线 (修正连线)

- 点击报错弹窗的 OK 关闭它。

- 在 Block Design 画布上,放大 ZYNQ 模块的左边。

- 找到

S_AXI_HP3接口。 - 顺藤摸瓜:看这根线连到了谁身上?

- 如果是连到了

Conv_0------ 错了! 请选中这根线,按 Delete 删掉。 - 如果是连到了

Pool_0------ 对了。 (如果对了还报错,直接看第二步)。

- 手动重连(如果刚才删了):

- 手动把

Pool_0的m_axi_gmem连到 ZYNQ 的S_AXI_HP3。 - (同理检查

HP1是否连的是Conv_0)。

第二步:重置地址 (关键修复)

无论连线是否有误,刚才的报错都已经把 Vivado 的"地址映射表"搞乱了,必须重置。

- 在 Vivado 编辑区顶部,点击 Address Editor 标签页(通常在

Diagram标签旁边)。

- 如果你找不到,点击顶部菜单

Window->Address Editor。

- 你会看到列表里可能有红色的条目,或者显示

Unmapped/Excluded。 - 在列表的任意空白处右键。

- 选择 Auto Assign Address (自动分配地址)。

- 这一步会让 Vivado 重新计算一遍所有人的门牌号,消除冲突。

第三步:再次验证

- 切回 Diagram 标签页。

- 再次点击工具栏上的 Validate Design (F6 / 紫色对勾)。

这一次应该就会弹出 "Validation Successful" 了!如果不成功,请截图你的 Block Design 连线图(ZYNQ 左侧连线部分)发给我。

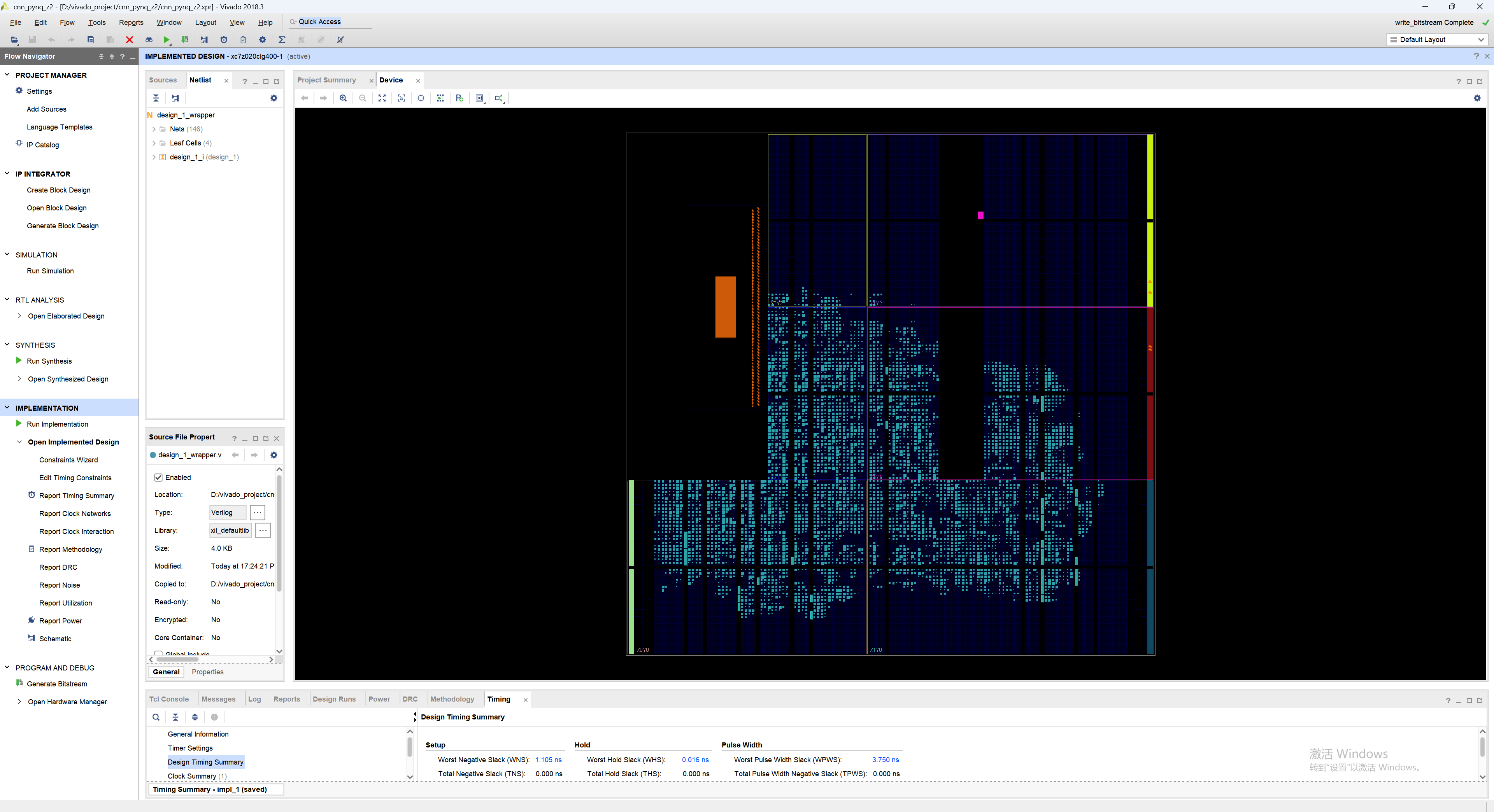

第六步:整理与验证

- 点击工具栏上的 Regenerate Layout (那个蓝色循环箭头图标),让乱糟糟的线变整齐。

- 点击 Validate Design (那个紫色对勾图标/F6)。

- 如果有报错,请告诉我。

- 如果提示 "Validation Successful",恭喜你,电路设计完成了!

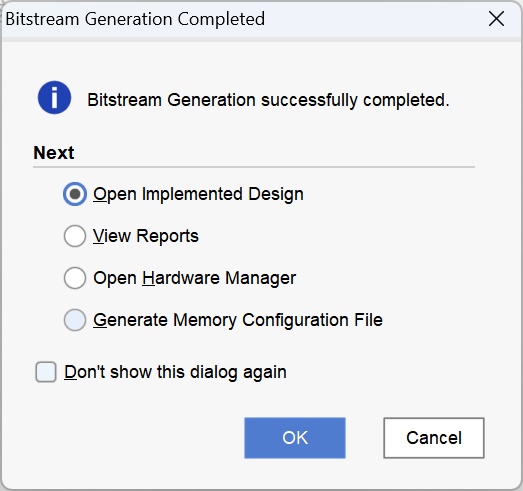

第七步:生成比特流 (Bitstream)

最后一步,把画好的图变成文件。

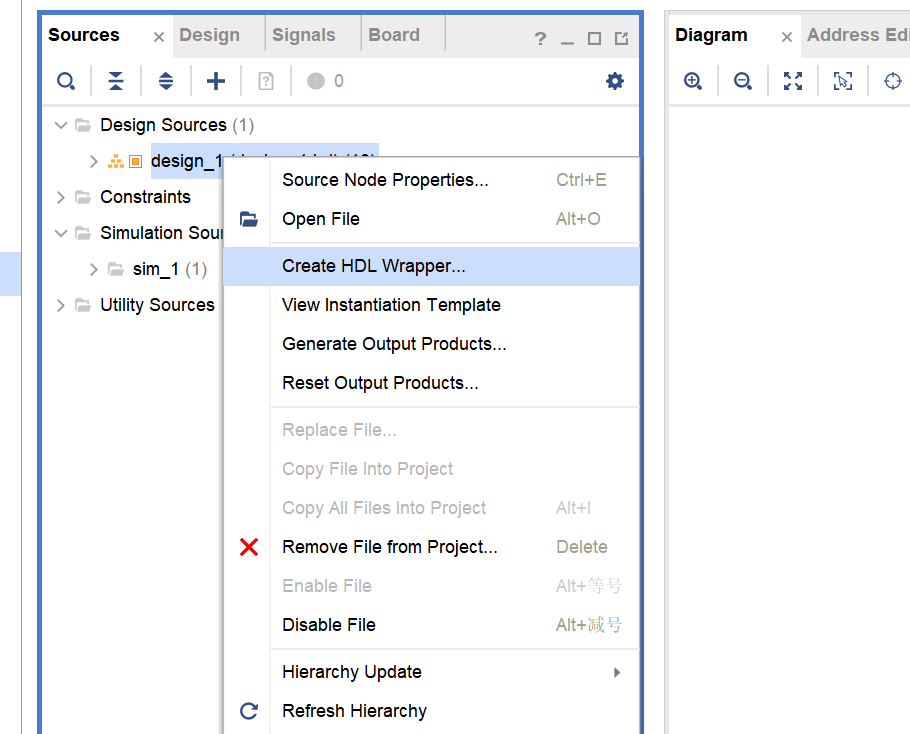

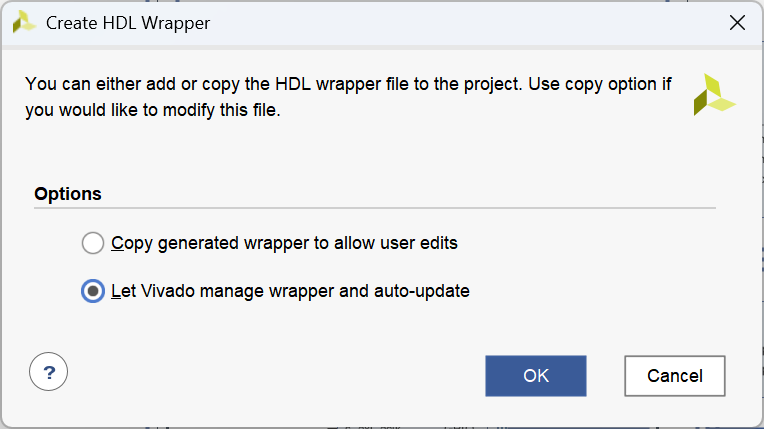

- 在 Sources 窗口,右键点击你的

design_1(或者你起的名字),选择 Create HDL Wrapper -> Let Vivado manage wrapper -> OK。 - 点击左侧 Flow Navigator 最下面的 Generate Bitstream。

- 这会跑很久(15-30分钟)。去喝杯咖啡吧!☕️

完成后,你会在工程目录下得到 design_1_wrapper.bit 和 design_1_wrapper.tcl (或 .hwh),这就是你要上传到 PYNQ 板子上的东西!

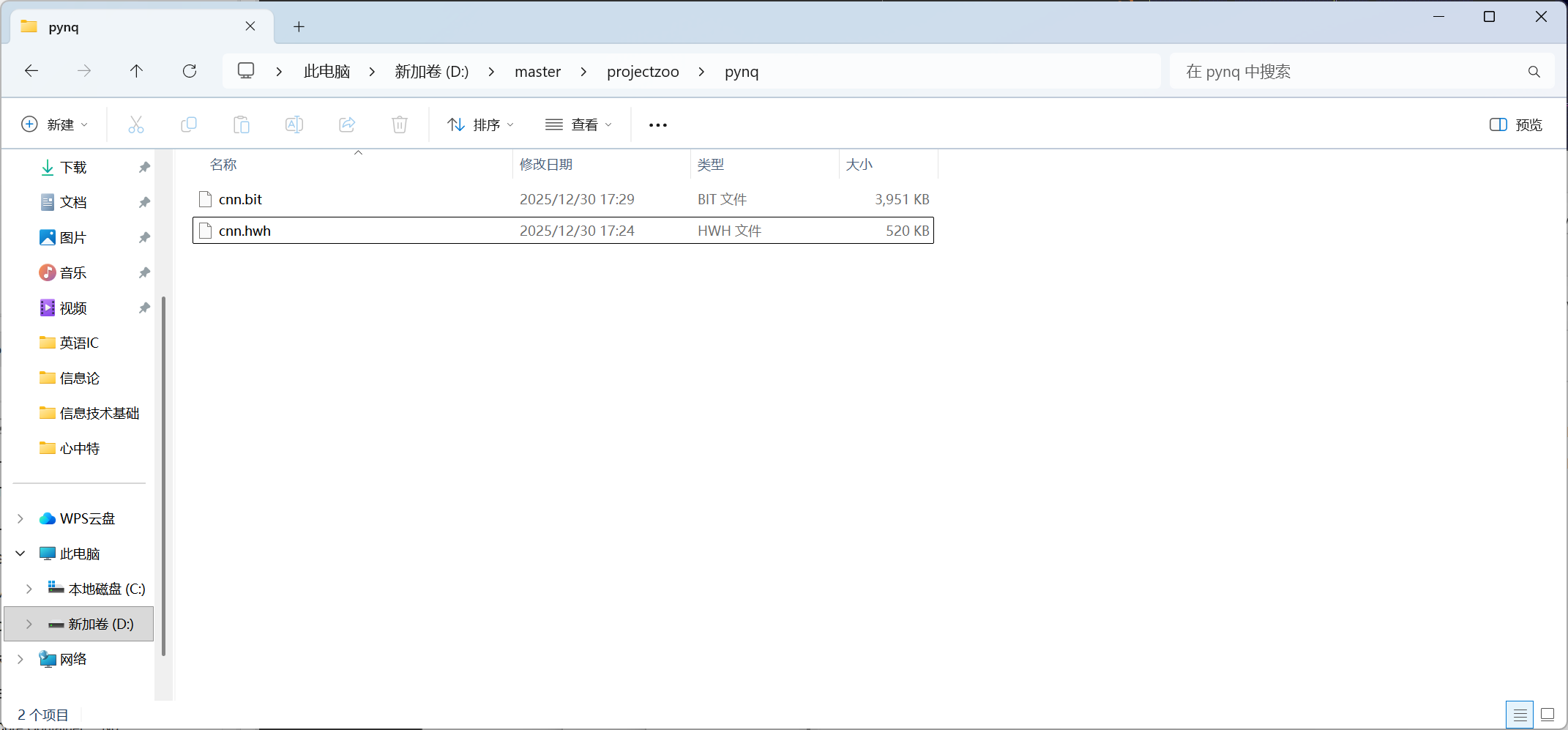

提取"硬件双雄"文件

恭喜你!🎉 这就是我们一直等待的胜利时刻!

这个弹窗标志着你所有的硬件设计工作已经圆满完成。Vivado 已经成功把你的 Block Design 转换成了可以在 PYNQ 板子上运行的二进制文件。

接下来只需最后一步:提取"硬件双雄"文件

现在你需要导出两个关键文件,以便稍后上传到 PYNQ 板子上使用。请按照以下步骤操作(你可以直接关掉那个弹窗,点击 Cancel 或 OK 都行,我们手动去找文件):

1. 找到 .bit 文件 (比特流)

这是 FPGA 的"大脑"配置文件。

- 位置 : 进入你的工程目录 ->

*.runs文件夹 ->impl_1文件夹。 - 文件名 : 通常叫

design_1_wrapper.bit。 - 操作 : 把它复制出来,改个好记的名字,比如

cnn.bit。

2. 找到 .hwh 文件 (硬件描述)

这是告诉 PYNQ 系统"我连了哪些线、地址是多少"的说明书。

- 位置 : 进入你的工程目录 ->

*.srcs->sources_1->bd->design_1->hw_handoff。 - 文件名 : 通常叫

design_1.hwh。 - 操作 : 把它复制出来,务必改成和 bit 文件完全一样的名字 (除了后缀),即

cnn.hwh。

✅ 总结

你现在应该手握这两个文件:

cnn.bitcnn.hwh

拿到这两个文件后,你的 Vivado 之旅就正式结束了!接下来的战场将转移到 Jupyter Notebook 上。

如果你找到了这两个文件,请告诉我,我们就可以开始在 PYNQ 上跑代码了! 🚀

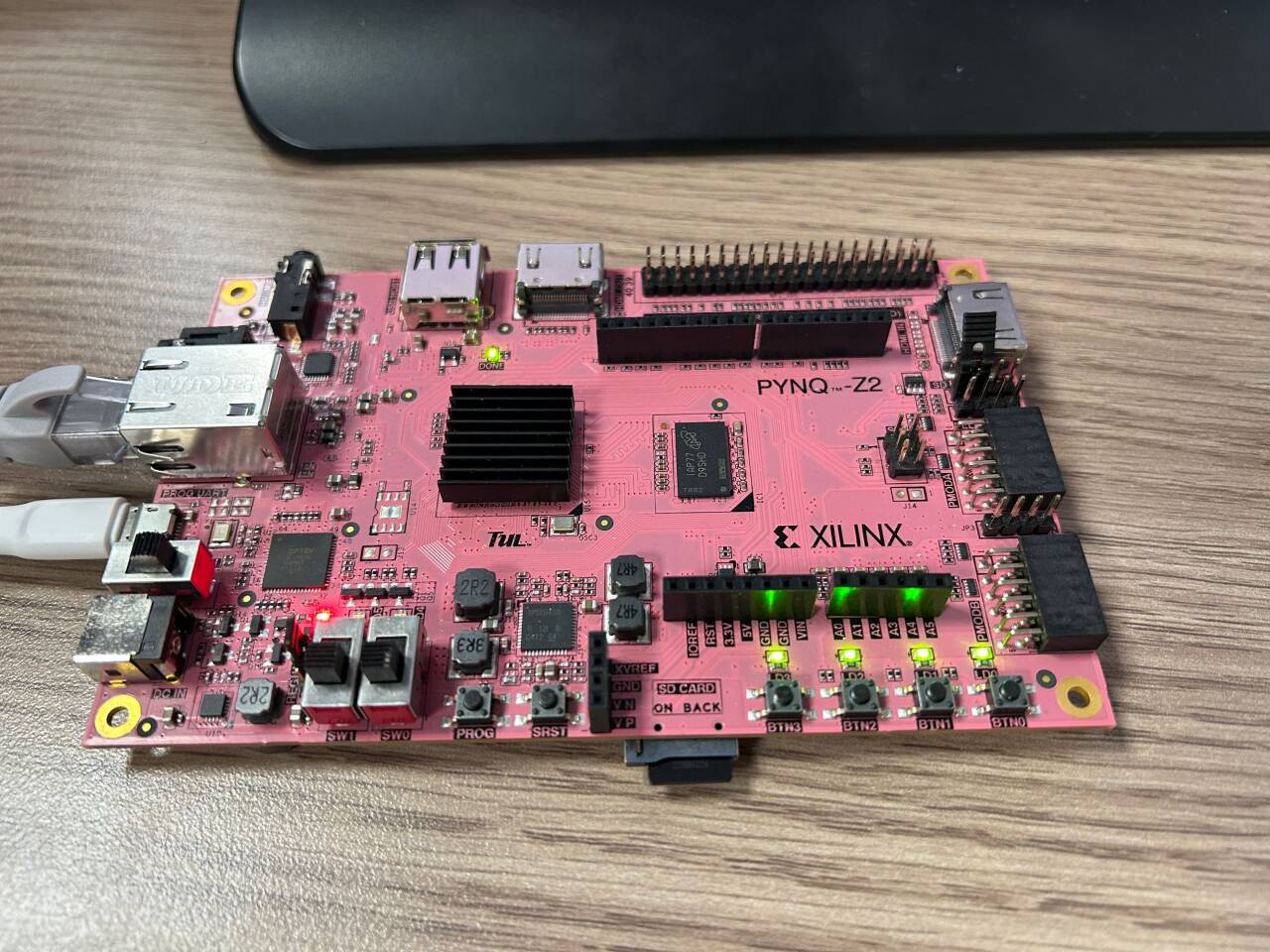

下载 PYNQ-Z2 板卡文件

这是一个非常经典的问题,原因很简单:Vivado 不知道你用的是 PYNQ-Z2 开发板,它以为你在用这个芯片(Zynq 7020)画一块全新的自定义电路板。

1. 为什么会出现这个问题?

在创建工程(New Project)时,你在 Default Part 界面选择了 "Parts" (芯片型号 xc7z020clg400-1),而没有去 "Boards" 标签页选择 "PYNQ-Z2"。

- 选芯片 (Part):Vivado 给你一个空的芯片。由于不知道外围电路(DDR 内存型号、网口引脚、时钟频率),它无法提供 "Board Preset"(板卡预设),你需要手动配置成百上千个参数。

- 选板卡 (Board) :Vivado 知道这块板子的所有外围电路信息,因此 Block Automation 会提供 "Apply Board Preset" 选项,一键帮你把 DDR 和 MIO 全部配好。

2. 解决方案(强烈推荐)

由于手动配置 DDR 参数极其复杂且容易出错(配错一个参数,板子就跑不起来),强烈建议你安装板卡文件并重新创建工程。这是一劳永逸的办法。

第一步:下载 PYNQ-Z2 板卡文件

你需要 PYNQ-Z2 的 Board Files。

- 你可以去 TUL 官网 或 PYNQ 官网下载。

- 或者直接搜索下载

pynq-z2.zip板卡文件包。

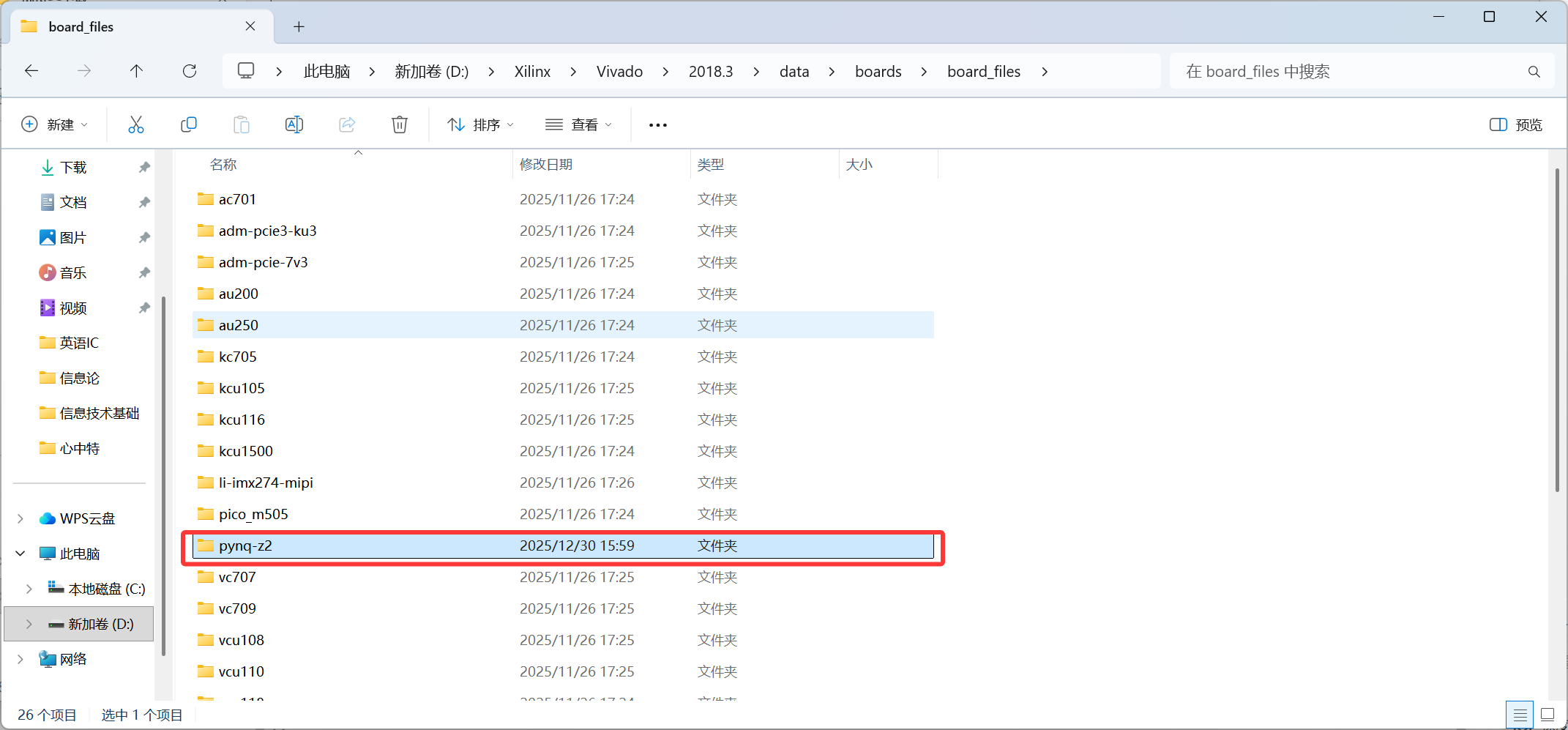

第二步:放入 Vivado 安装目录

- 解压下载的压缩包,你会得到一个

pynq-z2文件夹。 - 找到你的 Vivado 安装目录(根据你之前的日志):

👉D:\Xilinx\Vivado\2018.3\data\boards\board_files\ - 把

pynq-z2文件夹复制进去。

- *最终路径应类似:

...\board_files\pynq-z2\A.0\*

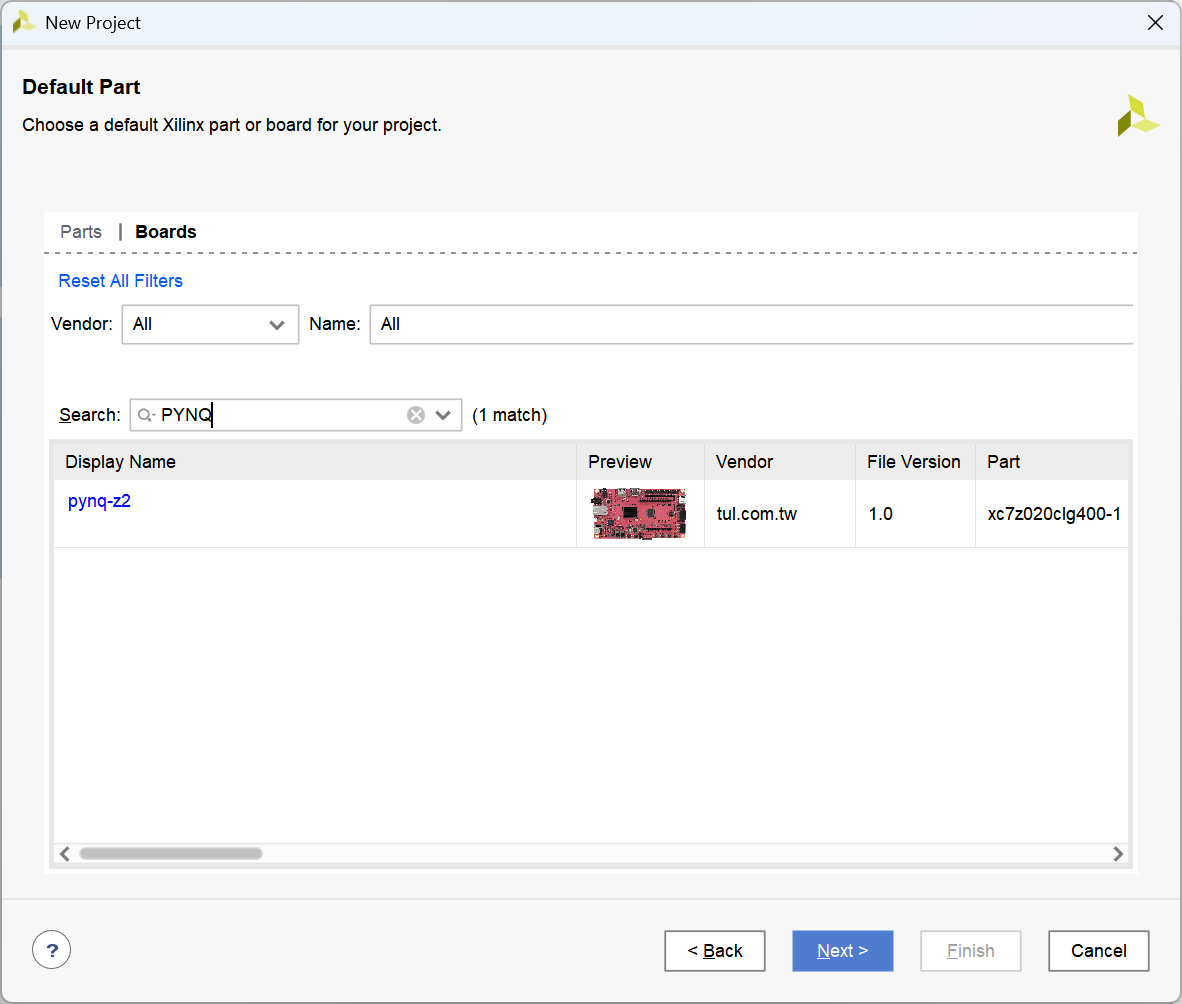

第三步:重建工程

- 关闭当前工程。

- Create New Project。

- 关键一步 :在选择芯片的界面,点击顶部的 "Boards" 标签。

- 搜索

PYNQ。 - 选中列表中的 PYNQ-Z2。

- (如果没有显示,说明板卡文件没放对位置,或者需要重启 Vivado) 。

- 完成创建。

第四步:重新添加 ZYNQ

现在,当你再次 Add IP -> ZYNQ7 Processing System -> Run Block Automation 时,你会发现 "Apply Board Preset" 的勾选项出现了!勾选它,点击 OK,DDR 和时钟就自动配好了。

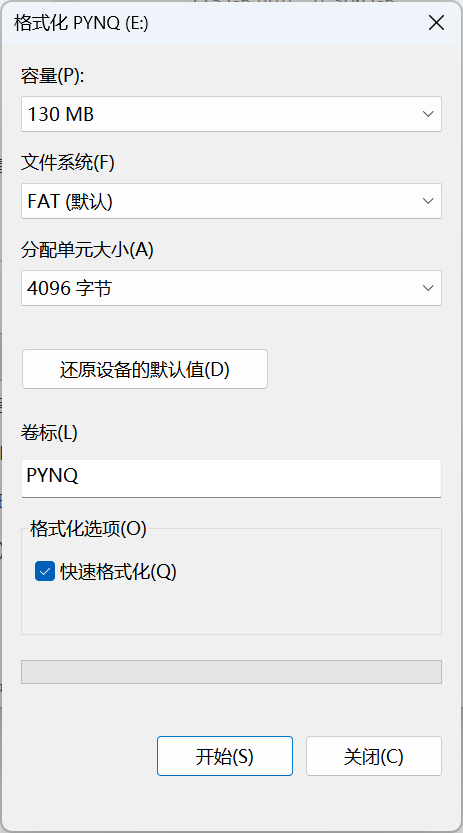

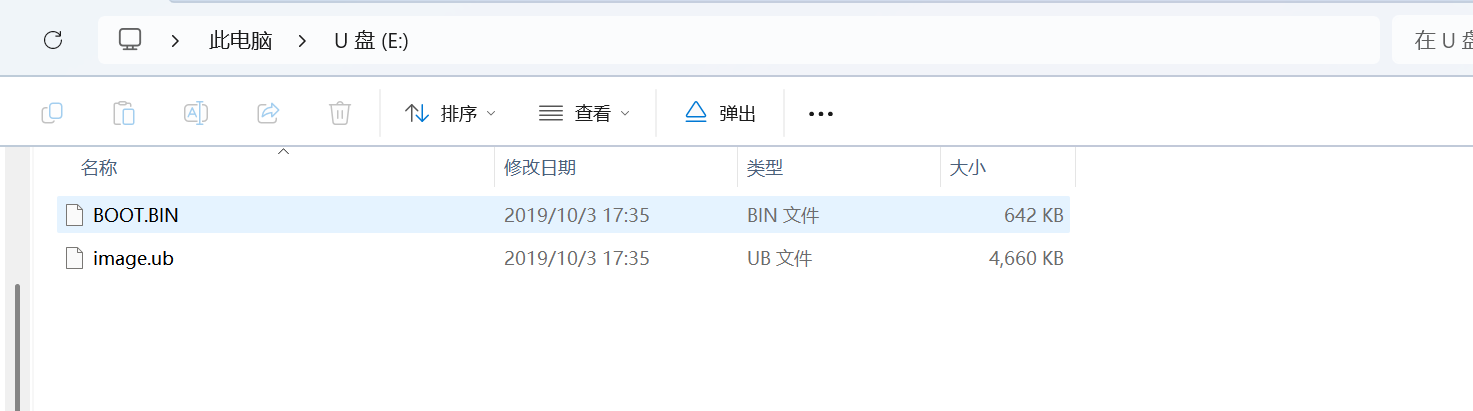

格式化SD卡

将SD卡插入读卡器,读卡器插入电脑上的USB口,然后去格式化SD卡

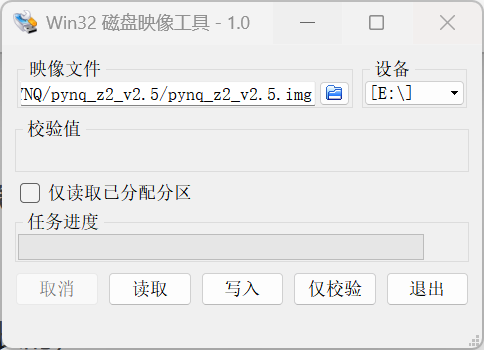

写入镜像文件

用镜像烧录工具 win32DiskImager写入镜像pynq_z2_v2.5.img

链接: https://pan.baidu.com/s/1PxDkWv4BL9H8Zxkz6OJoGQ?pwd=tp3n

提取码: tp3n

检查跳线帽

将做好的SD卡插入板子背面得卡槽

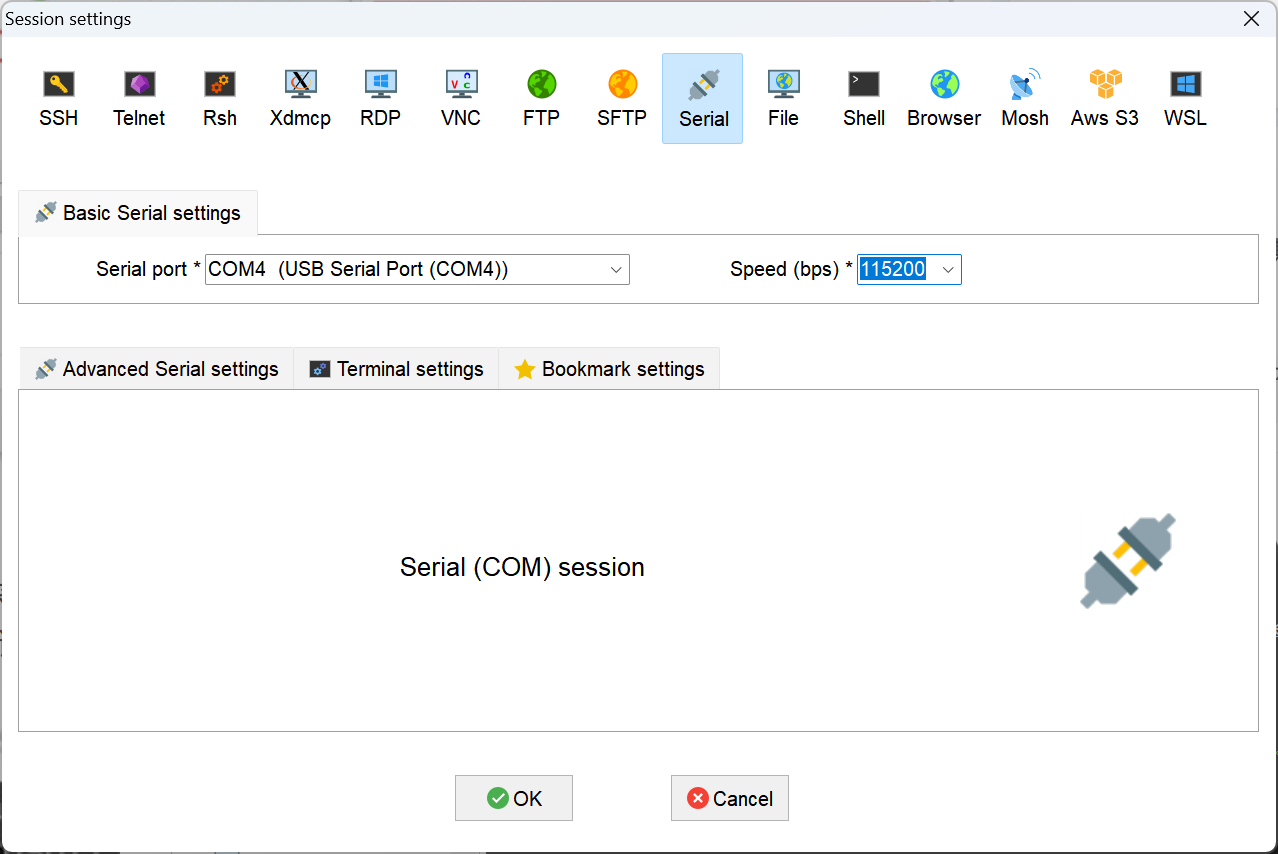

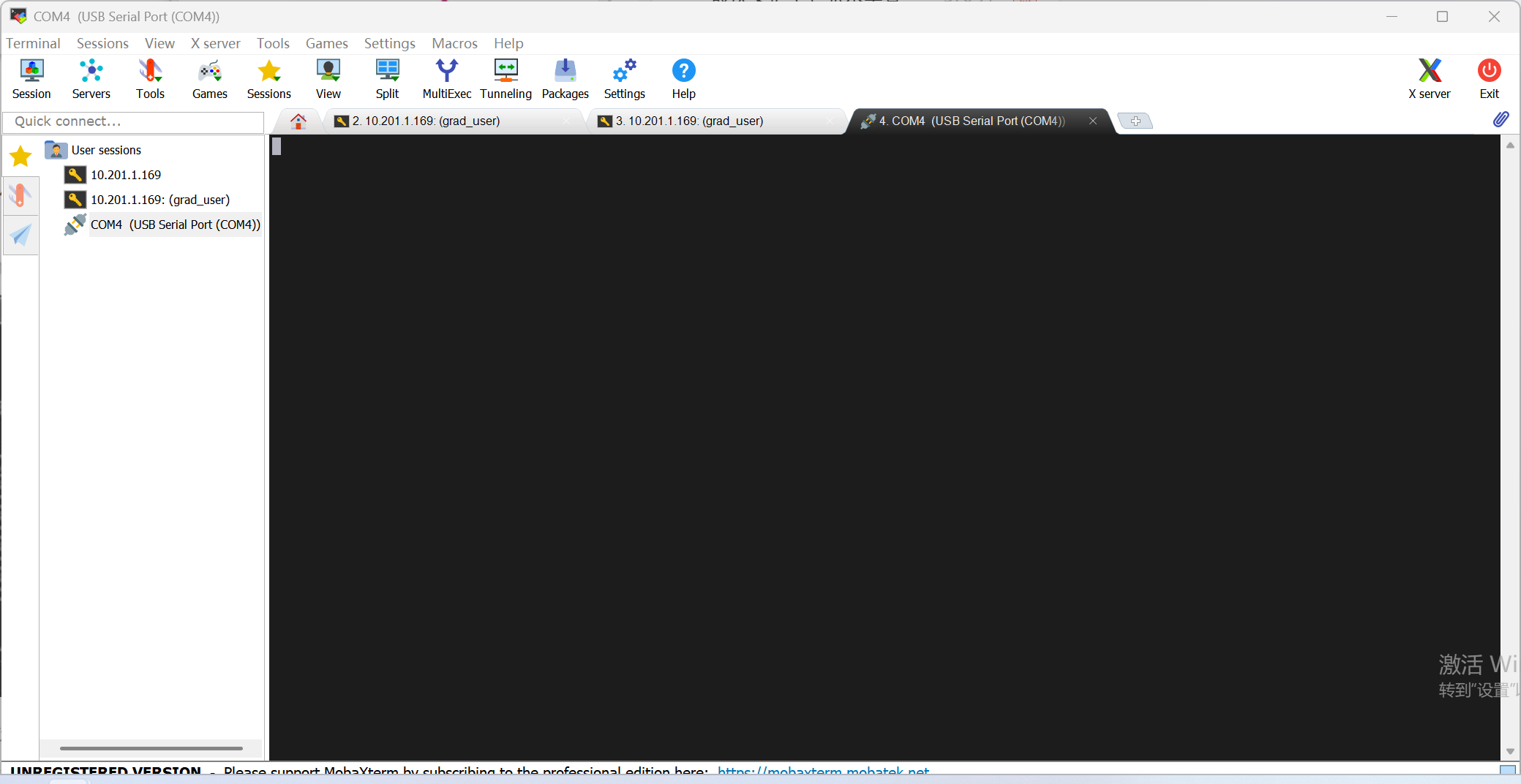

打开MobaXterm

重启板子,识别SD卡

重新开关机 直接把左下角的电源开关拨到 OFF,等灯灭了,再拨回 ON。

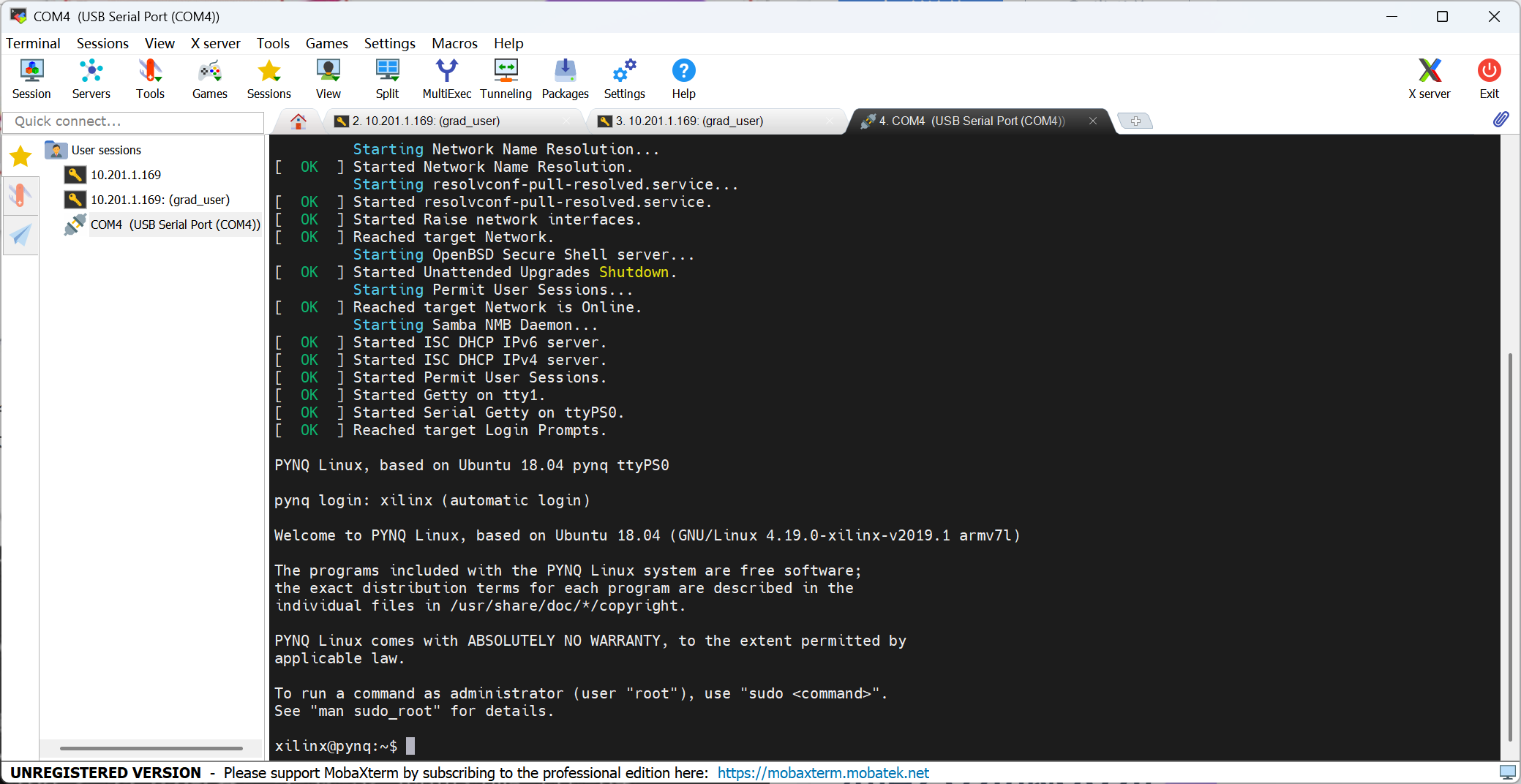

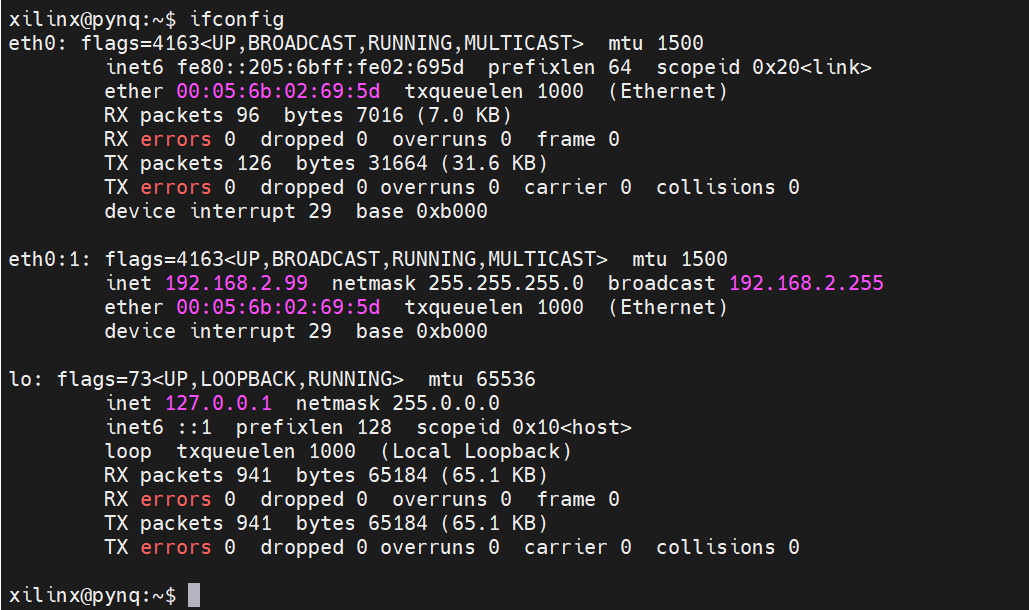

接下来我们要通过网线连接Jupyter Notebook

虽然现在你可以用这个黑框框敲命令,但 PYNQ 最强大的地方在于可以通过浏览器写 Python 代码。我们要利用你买的那根网线来实现这一点。

请按照以下步骤,获取板子的"身份证号"(IP 地址):

- 插好网线:确认网线一头插在板子上,一头插在电脑(或路由器)上。

- 注意:板子上的网口灯应该会亮起或闪烁。

- 查询 IP :

在刚才那个显示xilinx@pynq:~$的黑框框里,输入下面这个命令,然后按回车键:

bash

ifconfig

太棒了!找到了!

请看你截图中间偏下的位置,eth0:1 这一行显示了板子的固定 IP 地址:

👉 192.168.2.99

这意味着你的板子已经准备好接受连接了。

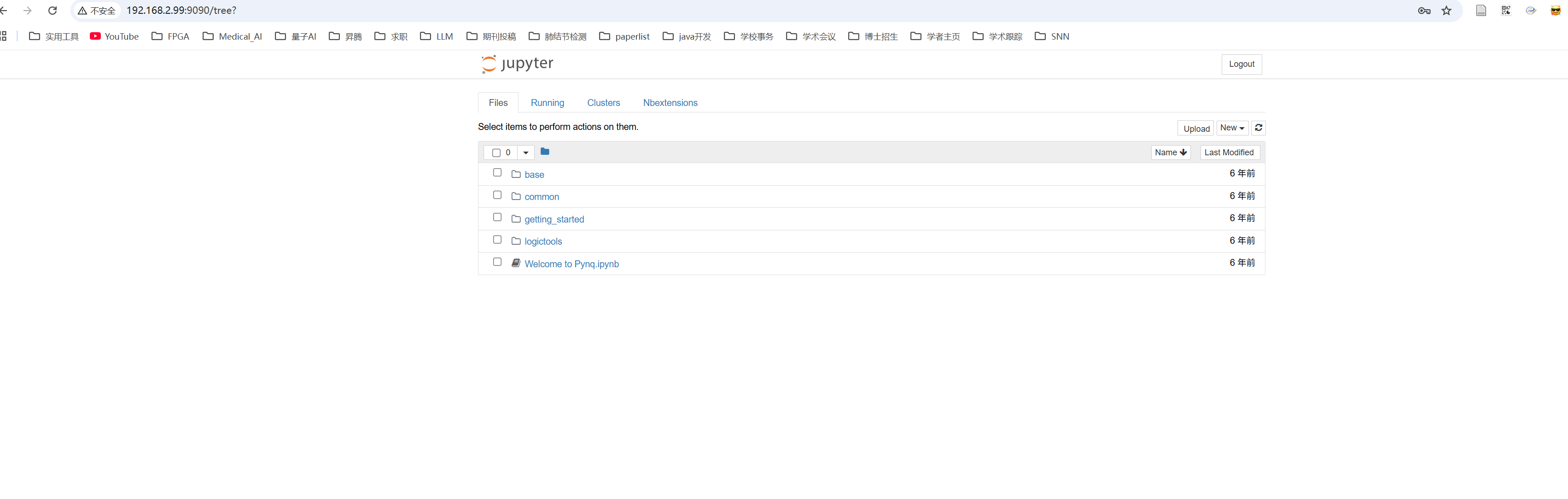

🚀 最后一步:在浏览器中打开它

请按照以下顺序操作(如果你运气好,第一步就能成功;如果不行,请看第二步):

1. 先直接试一试

- 打开你电脑上的 Chrome 浏览器(或 Edge)。

- 在顶部的地址栏输入:

192.168.2.99 - 按回车。

- 如果弹出一个登录框:

- Username (用户名) :

xilinx - Password (密码) :

xilinx - 点击登录,你应该就能看到 Jupyter Notebook 的界面了!

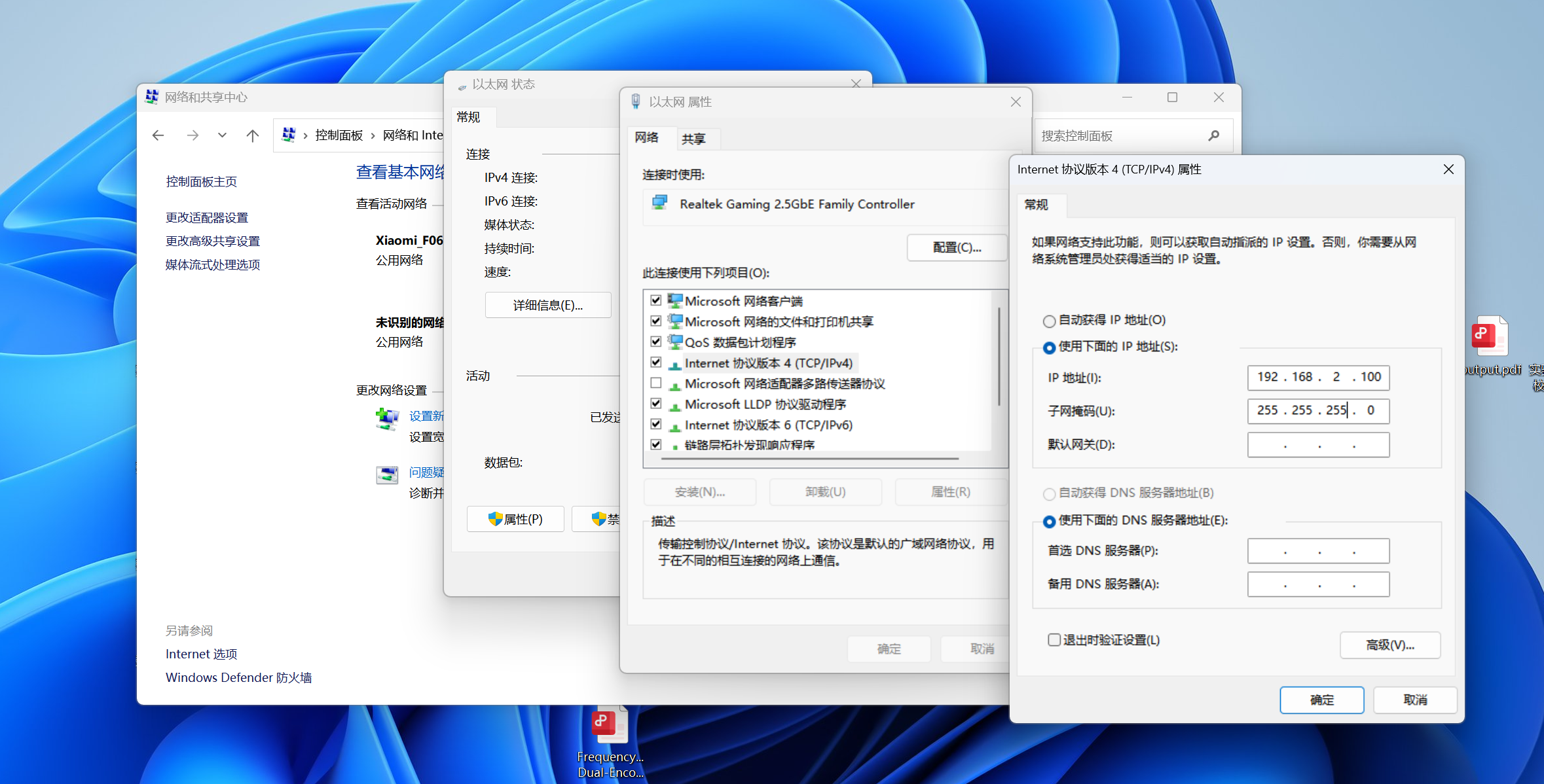

2. 如果网页打不开(一直在转圈)

这种情况非常常见,因为你是直接用网线把板子插在电脑上,你的电脑可能还不在同一个"频道"上。我们需要手动给电脑设置一个 IP。

请按以下步骤快速设置一下电脑:

- 打开网络设置:

- 在电脑右下角的网络图标(WiFi 或 电脑图标)上点右键 -> "网络和 Internet 设置"。

- 找到 "更改适配器选项" (Change adapter options) 或者 "更多网络适配器选项"。

- 找到网口:

- 你会看到好几个图标,找到那个连接着网线的"以太网"图标(通常没有红叉)。

- 右键 点击它 -> 属性 (Properties)。

- 修改 IPv4:

-

在列表里双击 "Internet 协议版本 4 (TCP/IPv4)"。

-

选择 "使用下面的 IP 地址":

-

IP 地址 :

192.168.2.100(注意最后一位是 100,不要和板子的 99 冲突) -

子网掩码 :

255.255.255.0 -

其他不用填。

-

点击 "确定" ,再点 "确定"。

- 重试:

- 设置好后,再次刷新浏览器里的

192.168.2.99,应该就能进去了!

快去试试,成功了给我看一眼那个网页长什么样!

基于你提供的源代码文件,尤其是 cnn.py 和 Traffic-Signs-Recognition.ipynb 的内容,这个项目的文件依赖关系非常严格。

源代码里写死了绝对路径(Hardcoded Paths),这意味着你不能随便把文件乱放,否则程序会找不到模型权重文件。

以下是你必须上传的文件清单和准确的目录结构:

1. 核心文件(放在项目根目录)

你需要从源代码的 jupyter_notebooks/GTSRB/ 文件夹里拿出这 4 个文件:

cnn.bit:比特流文件。cnn.hwh:你之前生成的硬件描述文件(如果源代码里只有cnn.tcl,你可以尝试用它,但为了稳定性,强烈建议使用你之前 Vivado 生成的.hwh文件 ,并将其重命名为cnn.hwh)。cnn.py:驱动程序。注意,这个文件里写死了读取数据的路径。Traffic-Signs-Recognition.ipynb:主运行笔记本。

2. 数据文件夹(必须上传!)

源代码 cnn.py 的第 176-224 行显示,它会去读取 data 文件夹里的二进制权重文件。

你需要上传 jupyter_notebooks/GTSRB/data/ 目录下的所有 .bin 文件:

w_conv1.bin,b_conv1.binw_conv2.bin,b_conv2.binw_fc1.bin,b_fc1.binw_fc2.bin,b_fc2.bin

3. 图片文件夹(用于测试)

笔记本中使用了 image 文件夹里的图片进行测试。

你需要上传 jupyter_notebooks/GTSRB/image/ 目录下的图片:

00000.png

⚠️ 关键:目录结构必须长这样

由于作者在 cnn.py 中使用了绝对路径 /home/xilinx/jupyter_notebooks/GTSRB/data/...,你必须 在 PYNQ 板子上建立一模一样的文件夹结构,否则运行会报错 FileNotFoundError。

请在 PYNQ 的 jupyter_notebooks 目录下创建一个叫 GTSRB 的文件夹,然后把东西放进去,结构如下:

text

/home/xilinx/jupyter_notebooks/ <-- PYNQ板子的默认根目录

│

└── GTSRB/ <-- 你必须新建这个文件夹,名字不能错!

│

├── cnn.bit <-- 核心文件

├── cnn.hwh <-- 核心文件 (注意名字要和bit文件一致)

├── cnn.py <-- 核心文件

├── Traffic-Signs-Recognition.ipynb

│

├── data/ <-- 新建这个文件夹

│ ├── w_conv1.bin <-- 放入所有 .bin 权重文件

│ ├── b_conv1.bin

│ └── ... (共8个bin文件)

│

└── image/ <-- 新建这个文件夹

└── 00000.png <-- 放入测试图片