这个共享内存大小是怎么计算出来的?入队列大小和出队列大小是什么意思?

struct SimBricksBaseIfEstablishData ests[2];

struct SimbricksProtoNetIntro net_intro;

struct SimbricksProtoPcieHostIntro pcie_h_intro;

unsigned n_bifs = 0;

if (netParams) {

if (SimbricksBaseIfInit(netif, netParams)) {

perror("SimbricksNicIfInit: SimbricksBaseIfInit net failed");

return -1;

}

if (SimbricksBaseIfListen(netif, &nicif->pool)) {

perror("SimbricksNicIfInit: SimbricksBaseIfListen net failed");

return -1;

}

memset(&net_intro, 0, sizeof(net_intro));

ests[n_bifs].base_if = netif;

ests[n_bifs].tx_intro = &net_intro;

ests[n_bifs].tx_intro_len = sizeof(net_intro);

ests[n_bifs].rx_intro = &net_intro;

ests[n_bifs].rx_intro_len = sizeof(net_intro);

n_bifs++;

}

if (pcieParams) {

if (SimbricksBaseIfInit(pcieif, pcieParams)) {

perror("SimbricksNicIfInit: SimbricksBaseIfInit pcie failed");

return -1;

}

if (SimbricksBaseIfListen(pcieif, &nicif->pool)) {

perror("SimbricksNicIfInit: SimbricksBaseIfListen pcie failed");

return -1;

}

ests[n_bifs].base_if = pcieif;

ests[n_bifs].tx_intro = di;

ests[n_bifs].tx_intro_len = sizeof(*di);

ests[n_bifs].rx_intro = &pcie_h_intro;

ests[n_bifs].rx_intro_len = sizeof(pcie_h_intro);

n_bifs++;

}

return SimBricksBaseIfEstablish(ests, n_bifs);

} // NOLINT(whitespace/indent)解释一下这段代码,ests[2]是什么意思,为什么是2, unsigned n_bifs是什么

int SimbricksBaseIfInit(struct SimbricksBaseIf *base_if,

struct SimbricksBaseIfParams *params) {

/* ensure latency >= sync interval in synchronization case */

bool must_check_sync = params->sync_mode == kSimbricksBaseIfSyncOptional ||

params->sync_mode == kSimbricksBaseIfSyncRequired;

if (must_check_sync && params->link_latency < params->sync_interval) {

fprintf(stderr,

"SimbricksBaseIfInit: latency must be larger or equal to sync"

" interval\n");

return -1;

}

memset(base_if, 0, sizeof(*base_if));

base_if->params = *params;

return 0;

}

int SimbricksBaseIfListen(struct SimbricksBaseIf *base_if,

struct SimbricksBaseIfSHMPool *pool) {

struct sockaddr_un saun;

int flags;

struct SimbricksBaseIfParams *params = &base_if->params;

/* make sure the socket path does not exceed the limits of saun.sun_path */

if (strlen(params->sock_path) >= sizeof(saun.sun_path)) {

fprintf(stderr,

"SimbricksBaseIfListen: socket path %s is too long "

"(exceeding %lu characters)\n",

params->sock_path, sizeof(saun.sun_path) - 1);

errno = ENAMETOOLONG;

return -1;

}

/* make sure we have enough space in the memory pool */

base_if->shm = pool;

size_t in_len = params->in_num_entries * params->in_entries_size;

size_t out_len = params->out_num_entries * params->out_entries_size;

if (pool->pos + in_len + out_len > pool->size) {

fprintf(stderr,

"SimbricksBaseIfListen: not enough memory available in "

"pool");

return -1;

}

if ((base_if->listen_fd = socket(AF_UNIX, SOCK_STREAM, 0)) == -1) {

perror("SimbricksBaseIfListen: socket failed");

return -1;

}

if (!params->blocking_conn) {

flags = fcntl(base_if->listen_fd, F_GETFL);

if (flags == -1 ||

fcntl(base_if->listen_fd, F_SETFL, flags | O_NONBLOCK) < 0) {

perror("SimbricksBaseIfListen: fcntl set nonblock failed");

goto out_error;

}

}

memset(&saun, 0, sizeof(saun));

saun.sun_family = AF_UNIX;

strncpy(saun.sun_path, params->sock_path, sizeof(saun.sun_path) - 1);

if (bind(base_if->listen_fd, (struct sockaddr *)&saun, sizeof(saun))) {

perror("SimbricksBaseIfListen: bind failed");

goto out_error;

}

if (listen(base_if->listen_fd, 5)) {

perror("SimbricksBaseIfListen: listen failed");

goto out_error;

}

/* initialize queues */

base_if->in_queue = pool->base + pool->pos;

base_if->in_pos = 0;

base_if->in_elen = params->in_entries_size;

base_if->in_enum = params->in_num_entries;

base_if->in_timestamp = 0;

pool->pos += in_len;

base_if->out_queue = pool->base + pool->pos;

base_if->out_pos = 0;

base_if->out_elen = params->out_entries_size;

base_if->out_enum = params->out_num_entries;

base_if->out_timestamp = 0;

pool->pos += out_len;

base_if->conn_state = kConnListening;

base_if->listener = true;

return (AcceptOnBaseIf(base_if) < 0 ? -1 : 0);

out_error:

close(base_if->listen_fd);

base_if->listen_fd = -1;

return -1;

}

int SimBricksBaseIfEstablish(struct SimBricksBaseIfEstablishData *ifs,

size_t n) {

struct pollfd pfds[n];

unsigned n_pfd;

size_t established = 0;

int ret;

while (established < n) {

size_t i;

n_pfd = 0;

established = 0;

for (i = 0; i < n; i++) {

struct SimbricksBaseIf *bif = ifs[i].base_if;

// woops something went wrong on this connection

if (bif->conn_state == kConnClosed) {

fprintf(stderr,

"SimBricksBaseIfEstablish: connection %zu is "

"closed\n",

i);

return -1;

}

// check if it is connected yet (this might change that)

ret = SimbricksBaseIfConnected(bif);

if (ret < 0) {

fprintf(stderr, "SimBricksBaseIfEstablish: connecting %zu failed\n", i);

return -1;

} else if (ret > 0) {

pfds[n_pfd].fd = SimbricksBaseIfConnFd(bif);

pfds[n_pfd].events =

(bif->conn_state == kConnListening ? POLLIN : POLLOUT);

pfds[n_pfd].revents = 0;

n_pfd++;

assert(n_pfd <= n);

}

// next check if we are now ready to send the handshake

if ((bif->conn_state == kConnAwaitHandshakeTx ||

bif->conn_state == kConnAwaitHandshakeRxTx) &&

SimbricksBaseIfIntroSend(bif, ifs[i].tx_intro, ifs[i].tx_intro_len) !=

0) {

fprintf(stderr,

"SimBricksBaseIfEstablish: Sending intro on %zu "

"failed\n",

i);

return -1;

}

// finally check if we can receive the handshake now

if (bif->conn_state == kConnAwaitHandshakeRx) {

ret = SimbricksBaseIfIntroRecv(bif, ifs[i].rx_intro,

&ifs[i].rx_intro_len);

if (ret < 0) {

fprintf(stderr,

"SimBricksBaseIfEstablish: Receiving intro on %zu "

"failed\n",

i);

return -1;

} else if (ret > 0) {

pfds[n_pfd].fd = SimbricksBaseIfIntroFd(bif);

pfds[n_pfd].events = POLLIN;

pfds[n_pfd].revents = 0;

n_pfd++;

assert(n_pfd <= n);

}

}

if (bif->conn_state == kConnOpen) {

established++;

}

}

if (n_pfd == 0 && established != n) {

fprintf(stderr,

"SimBricksBaseIfEstablish: no poll events to wait for "

"but not all established (BUG)\n");

abort();

} else if (n_pfd > 0) {

ret = poll(pfds, n_pfd, -1);

if (ret < 0) {

fprintf(stderr, "SimBricksBaseIfEstablish: poll failed\n");

return -1;

}

}

}

return 0;

}解释一下BaseIfInit和BaseIfListen方法,在最后还有SimBricksBaseIfEstablish(ests, n_bifs);,这几个方法有什么区别,都在干啥;还有在计算共享内存大小时,这个in,out的条目数量,不应该是随时变化的吗?为什么在NicIfInit时参与初始化的计算,难道in,out_num_entries是常数?

if (!params->blocking_conn) {

flags = fcntl(base_if->listen_fd, F_GETFL);

if (flags == -1 ||

fcntl(base_if->listen_fd, F_SETFL, flags | O_NONBLOCK) < 0) {

perror("SimbricksBaseIfListen: fcntl set nonblock failed");

goto out_error;

}

}这两段代码中,为什么要先对listen_fd的文件进行F_GETFL操作?后面进行的==-1判断以及进行fcntl操作时,flags|O_NONBLOCK是什么意思?为什么要|,?!params->blocking_conn是什么判断?

struct sockaddr_un

{

_SOCKADDR_COMMON (sun);

char sun_path[108]; /* Path name. */

}; struct sockaddr_un saun;这个结构体的名字是什么含义,就是_un后缀是什么意思?saun什么意思?sun_path,我知道path是路径,sun又是代表什么?以及在sockaddr_un中没有sun_family成员,但是后面用到了saun.sun_family = AF_UNIX;?还有socket到底是怎么工作的,通过socket构造出了一个fd,那直接用这个fd不就行了,bind又是在干什么?

什么是宏?为什么要用宏?宏展开又是什么?宏在什么时候展开?如何判断一段代码是否用了宏,以及展开后的代码是怎样的?

举一些socket使用的实例/代码/场景,现在还是觉得有些抽象,因为我觉得就是可以直接保存fd,然后用fd就行了,你所谓的"设置手机号"进行的strcpy和bind操作,看不出来有什么用

// check if it is connected yet (this might change that)

ret = SimbricksBaseIfConnected(bif);

if (ret < 0) {

fprintf(stderr, "SimBricksBaseIfEstablish: connecting %zu failed\n", i);

return -1;

} else if (ret > 0) {

pfds[n_pfd].fd = SimbricksBaseIfConnFd(bif);

pfds[n_pfd].events =

(bif->conn_state == kConnListening ? POLLIN : POLLOUT);

pfds[n_pfd].revents = 0;

n_pfd++;

assert(n_pfd <= n);

}这段代码什么意思?尤其是ret>0时的那些

Tx,Rx什么意思?

if ((bif->conn_state == kConnAwaitHandshakeTx ||

bif->conn_state == kConnAwaitHandshakeRxTx)这些状态是指什么意思?RxTx组合起来又是啥意思?

所谓" 等待 PCIe 和网络都完成连接 + 完成互相自我介绍"是什么意思?什么叫完成连接?如果是进行模拟的话,是否意味着多线程,每个线程模拟的一个模拟器,然后模拟器都在进行连接的操作?

我想要知道的是,simcxl中的文件目录结构,各目录、文件夹,以及文件的意义和作用;以及在使用时,如何从最顶层的语言封装一层层往下调用,直到代码实际运行的

m5是什么,python标准库->m5绑定时什么意思?

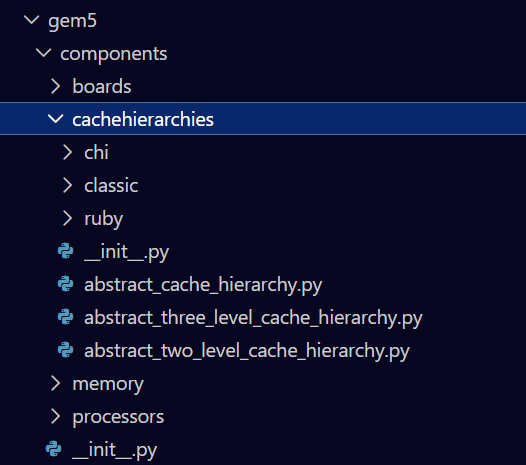

详细解释SimCXL的python/gem5/components的cache组件的目录结构与文件,尤其是chi是什么意思?

在simcxl中,如果设备发起Load/Store操作,如果只有CXL设备,那么SimCXL代码的执行流程,调用链是怎样的?都有哪些代码发挥了作用?要求按顺序一一列出,并要求完整

4.1 Type 3(内存扩展器)Classic 模式完整链条

用户运行:

gem5.opt x86-cxl-type3-with-classic.py

│

▼

[Python 初始化阶段]

1. 创建 SimpleBoard / X86Board

2. 配置 PrivateL1PrivateL2SharedL3CacheHierarchy

(L1 32K/32K + L2 512K + L3 96M, MESI)

3. 创建 DIMM_DDR5_4400 × 2

- memory[0]: 3GB 主机内存 @ 0x00000000

- memory[1]: 8GB CXL 内存 @ 0xC0000000 (CXL 地址空间)

4. 注入 CXLBridge(位于 L3 缓存与 CXL DRAM 控制器之间)

5. set_kernel_disk_workload(vmlinux, disk_img, cmd)

6. simulator.run()

│

▼

[gem5 事件驱动模拟启动]

7. KVM CPU 快速启动 Linux 内核(跳过 Boot 细节)

8. Linux 内核通过 ACPI/SRAT 发现 CXL NUMA 节点

9. m5 exit 事件触发 → 切换到 TIMING/O3 CPU

│

▼

[基准测试执行阶段]

10. 用户程序发起内存访问(例如 numactl --membind=1 ./test)

│

▼

[CPU 访问 CXL 内存的周期级模拟路径]

CPU 核心(O3/TIMING)

→ L1D Cache(MESI 查找)

→ L2 Cache(MESI 查找)

→ L3 Cache(共享,MESI 查找)

→ Cache Miss → 发送 MemReq 包到内存总线

│

▼

CoherentXBar(一致性总线)

→ 地址解码:命中 CXL 地址范围?

→ Yes → 路由到 CXLBridge

│

▼

CXLBridge::BridgeResponsePort::recvTimingReq()

→ 检查地址是否在 cxl_range 内

→ 计算 total_delay = bridge_lat + proto_proc_lat

→ 设置 pkt->cxl_cmd = M2SReq(读)/ M2SRwD(写)

→ 将包推入 reqQueue,调度 schedTimingReq 事件

│

[等待 total_delay 周期]

│

▼

CXLBridge::BridgeRequestPort 发送请求

→ CXL 设备侧 MemCtrl::recvTimingReq()

→ DRAM Interface 计算 DRAM 时序(tCL, tRCD, tRP...)

→ 生成响应包,pkt->cxl_cmd = S2MDRS(含数据)

│

[等待 DRAM 访问延迟]

│

▼

CXLBridge::BridgeResponsePort 接收响应

→ 推入 respQueue

→ 调度 schedTimingResp 事件

│

[等待 bridge_lat 返回延迟]

│

▼

CoherentXBar → L3 Cache 填充

→ L2 Cache 填充

→ L1D Cache 填充

→ CPU 寄存器文件获得数据

│

▼

[周期计数更新,统计延迟/带宽指标]这段流程还是有点抽象,我是刚接触的博士生,再为我讲解一下