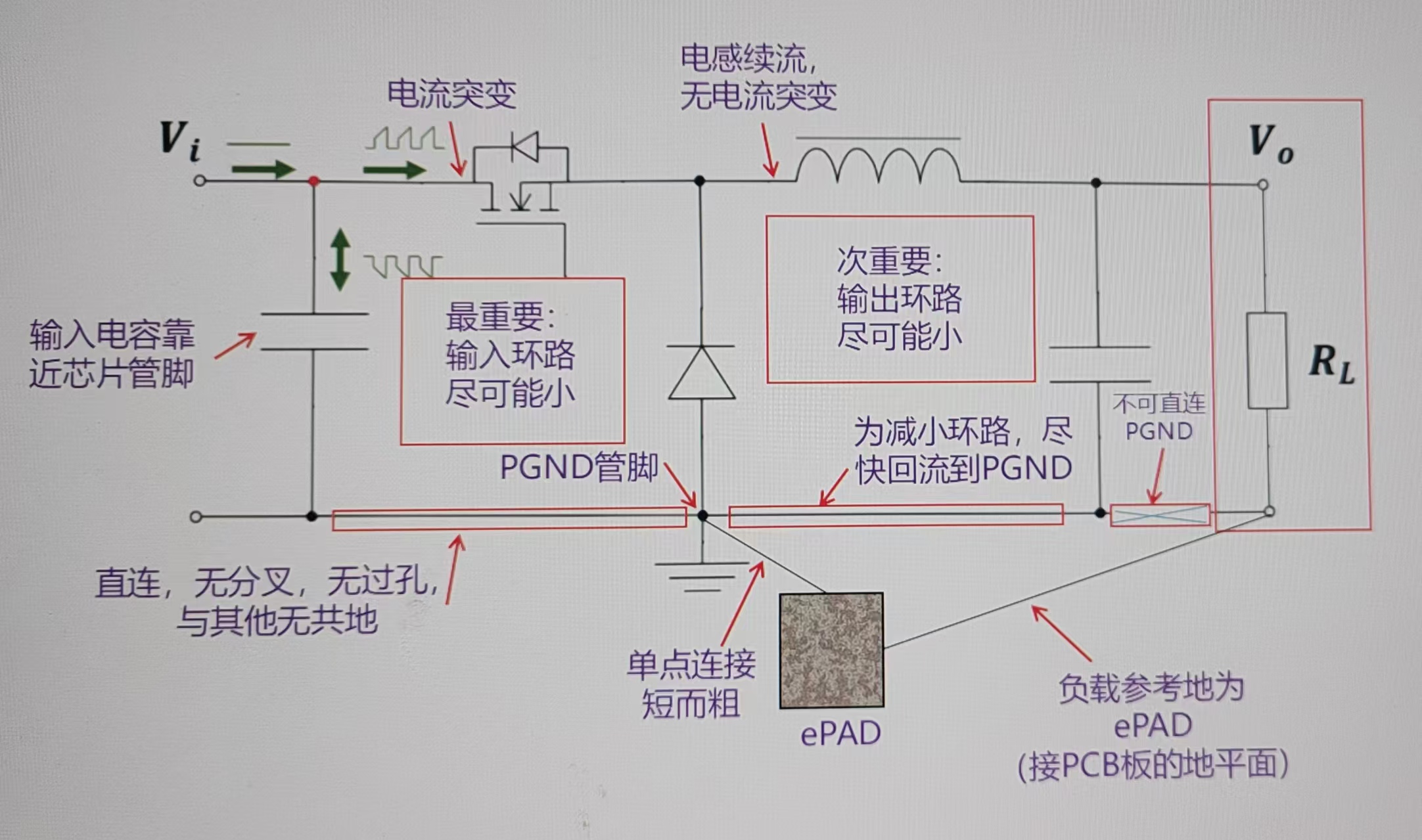

本文的讨论基于以下这个原理图。注意,续流二极管用于异步buck电路中,在同步buck电路中,为MOS下管。

一、电感续流与电流突变核心问题

1. 电感的电流方向到底会不会突变?

答 :绝对不会。电感的核心电气特性就是电流不能突变 ,这里的不能突变既包含电流大小的瞬间剧变,也包含电流方向的瞬间翻转,这是由电感的电磁感应原理决定的。

当电感处于储能状态时,会储存磁场能量,一旦电路中的开关管(上管/下管)状态发生切换,电感会立刻产生感应电动势,强行维持原有电流的流动方向和连续流动的状态 ,绝不允许电流突然中断或者方向突然改变。

前面提到的"电流突变",并非电感自身电流的突变,而是开关节点、芯片SW引脚处电流路径、电流流入流出方向的切换,电感本身的电流始终是连续且缓慢变化的,方向从头到尾保持一致,这一点是开关电源续流工作的核心基础,也是后续所有布局和EMC分析的前提。

2. 续流二极管(或MOS下管)的作用是什么,它和电感电流的关系是什么?

答 :续流二极管(同步Buck电路中也可用下管MOS管替代)的核心作用就是为电感提供续流通道,配合电感实现电流连续 。

当Buck电路上管关断、下管导通时,电感无法瞬间改变电流,此时电感释放储存的磁场能量,电流会通过续流二极管/下管形成闭合回路,继续沿着原来的方向流动,直到电感能量逐步释放完毕、电流缓慢衰减。

这个过程中,续流二极管只是提供低阻抗通路,完全不会改变电感电流的原有方向,也不会让电流出现突变,它的存在就是为了顺应电感"电流不能突变"的特性,避免开关管关断时产生高压尖峰,同时保证输出能量持续传递,最终让整个输出环路的电流保持平稳过渡,没有剧烈的状态突变。

3. 输出环路的两个电流路径,哪个电流突变更大?

答:首先明确定义本次讨论中两条输出环路电流路径:

- 路径一(开关续流内环路径):芯片SW节点 → 电感 → 输出主电容 → 回到芯片GND/SW,这是紧贴芯片、电感、主电容的高频小闭合续流内环,也是开关瞬态动作的核心回路;

- 路径二(远端负载供电外环路径):芯片SW节点 → 电感 → 输出主电容 → 长线走线 → 远端实际负载 → 远端回流地 → 最终回到芯片GND/SW,这是带长线、带远端负载的外部供电外环,负责向负载输送稳定能量。

明确两条路径后,核心结论:路径一(开关续流内环)的电流突变、电流切换剧烈程度,远大于路径二(远端负载外环) 。当然,路径二包含了路径一。

具体原因:上管导通切换为上管关断、下管续流导通的一瞬间,SW节点的电流流向会在路径一内部发生极速切换------原本从输入端灌向电感的电流,瞬间切为通过下管/续流二极管流向电感,这个切换全部发生在极小的内环里,电流方向在开关节点极速换向,电流变化率(di/dt)极高,是输出环路中突变的核心来源;

而路径二的远端负载外环,已经经过电感的缓冲作用、主电容的滤波作用,高频瞬态突变全部被截留在路径一内部,传到长线与负载端的只剩平稳直流+极低纹波,几乎看不到任何电流突变,整体波形平滑稳定。

简单总结:输出环路的突变只集中在紧贴芯片的续流内环(路径一),远端负载外环(路径二)全程干净平缓,无明显突变。

4. 输出环路整体有没有状态突变?

答 :从最终效果、电感电流本身来看,输出环路没有明显的状态突变。

因为电感的储能续流特性+续流二极管的通路配合,把开关管动作带来的潜在电流突变,全部转化成了平缓、连续、缓慢衰减的电流变化,没有出现电流突然中断、方向突然翻转、电压剧烈跳变的情况。

但从开关动作的瞬间、回路电流通路切换来看,存在极短时间内的电流路径切换------也就是上面定义的路径一(续流内环)内部的极速切换,只是这种切换被电感缓冲,不会对环路的稳定状态造成破坏性突变,最终输出的电流和电压都是平稳过渡的,这也是输出环路相比输入环路更"干净"的核心原因。

二、输出电容摆放位置与负载适配问题

1. 电感后面的输出电容,摆放位置对电路有影响吗?离芯片/电感远一点有问题吗?

答:输出电容的摆放位置影响极大,绝对不能离芯片和电感太远,远距离摆放会带来三个严重问题,直接影响电路稳定性和EMC性能:

- 走线过长会产生寄生电感,寄生电感会与输出电容形成谐振,大幅削弱电容的高频滤波效果,导致输出纹波、噪声急剧增大,无法有效滤除开关电源的高频干扰;

- 长线走线会增加回路阻抗,当负载出现电流突变时,输出电容无法快速响应,无法及时为负载提供瞬态电流,导致负载端电压跌落、波动过大,影响负载正常工作;

- 长走线会扩大输出环路(尤其是路径一续流内环)的面积,增大EMC辐射风险,让电路更容易对外产生干扰,也更容易受到外部干扰的影响。

因此,输出主电容必须紧邻电感输出端和芯片的输出引脚、地引脚,尽量缩短电容与电感、芯片之间的走线,最小化路径一的环路面积,这是保证滤波效果、电路稳定性和EMC性能的关键,也是我们讨论中明确的核心布局原则。

2. 负载在远端时,输出电容应该靠近负载,还是靠近电感/芯片?

答:采用"主电容+远端辅助电容"的双电容布局方案,两者缺一不可,且分工明确,分别对应输出环路的两条路径,贴合我们全程讨论的逻辑:

- 主输出电容:必须优先靠近电感和芯片摆放,核心作用是收紧路径一(续流内环),滤除开关电源产生的高频纹波、吸收开关节点的噪声,稳定芯片输出端的电压,同时承担核心的能量缓冲作用,抑制内环的电流突变,是保证输出环路基础稳定性的关键;

- 远端辅助电容:在远端负载附近额外并联,核心作用是适配路径二(远端负载外环),补偿负载长线传输带来的寄生效应,稳定负载端的电压,应对负载端的电流突变,避免长线导致的电压衰减和噪声叠加,保证远端负载工作稳定。

绝对不能只把电容放在远端、远离电感和芯片------否则路径一的核心滤波效果完全失效,开关噪声无法抑制,电路会出现纹波超标、EMC不合格、负载响应差等一系列问题;也不能只放主电容、不放远端辅助电容------负载远端会因长线寄生参数出现电压不稳、瞬态响应差的问题,影响负载正常工作。

3. 远端辅助电容的容量怎么选,和主电容相比有什么区别?

答:辅助电容和主电容的容量、功能、选型逻辑完全不同,核心区别围绕两条输出路径的需求设计,具体如下:

- 主输出电容(服务于路径一:续流内环):容量较大,一般根据负载电流、开关频率、纹波要求选择,常见规格为几十μF~几百μF,通常采用"电解电容/固态电容+大容量陶瓷电容"的组合;核心功能是低频滤波、储存能量、滤除开关纹波的低频分量,响应速度相对较慢,但储能能力强,主要用于抑制内环的开关突变,稳定芯片输出端电压。

- 远端辅助电容(服务于路径二:远端负载外环):容量远小于主电容,一般选择0.1μF~10μF,优先选用高频特性好的陶瓷电容(如X7R、X5R材质);核心功能是高频滤波、快速响应负载突变、补偿长线寄生电感,响应速度极快,虽然储能较小,但能瞬间释放电流,应对负载的瞬态电流需求,同时滤除长线引入的高频噪声,稳定负载端电压。

如果负载突变幅度很大(比如大电流负载、频繁启停的负载),可以在远端辅助电容旁边再并联一个10μF~47μF的中等容量电容,形成"小容量高频陶瓷电容+中等容量储能电容"的组合,兼顾快速响应和储能能力,完美承接负载突变的电流需求,避免出现小电容储能不足无法应对大突变的情况。

三、输入电流、输入电容容量计算公式及实例计算

1. Buck电路输入电流计算公式(适用于非同步/同步Buck,连续导通模式CCM)

(1)输入平均电流计算公式

公式:IIN(AVG)=VOUT×IOUTη×VINI_{IN(AVG)} = \frac{V_{OUT} \times I_{OUT}}{\eta \times V_{IN}}IIN(AVG)=η×VINVOUT×IOUT

参数含义(清晰标注,方便工程选型):

- IIN(AVG)I_{IN(AVG)}IIN(AVG):输入平均电流,单位A(安培),是外部供电进线的核心参考电流;

- VOUTV_{OUT}VOUT:电源输出电压,单位V(伏特),根据负载需求设定;

- IOUTI_{OUT}IOUT:电源最大输出负载电流,单位A(安培),按负载最大功耗计算;

- η\etaη:电源转换效率,Buck电路一般取0.850.95(85%95%),高频小电流电路取0.85,大电流高效电路取0.95;

- VINV_{IN}VIN:电源输入电压,单位V(伏特),为外部供电电压(如12V、24V)。

(2)输入纹波电流峰值计算公式(输入环路突变电流核心参考)

公式:IIN(RIPPLE)=IOUT×VOUT×(VIN−VOUT)VIN2I_{IN(RIPPLE)} = I_{OUT} \times \sqrt{\frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN}^2}}IIN(RIPPLE)=IOUT×VIN2VOUT×(VIN−VOUT)

参数含义:

- IIN(RIPPLE)I_{IN(RIPPLE)}IIN(RIPPLE):输入纹波电流峰值,单位A(安培),是输入环路电流突变的核心指标,直接决定输入电容的选型;

- 其余参数与输入平均电流公式一致,无需额外定义。

2. Buck电路输入电容容量计算公式(满足纹波电压要求,CCM模式)

(1)输入电容容量核心公式

公式:CIN≥IIN(RIPPLE)×(1−D)fSW×ΔVINC_{IN} \geq \frac{I_{IN(RIPPLE)} \times (1 - D)}{f_{SW} \times \Delta V_{IN}}CIN≥fSW×ΔVINIIN(RIPPLE)×(1−D)

参数含义(贴合工程实际,避免歧义):

- CINC_{IN}CIN:输入电容最小所需容量,单位F(法拉),实际选型需转换为μF(1F=10^6μF);

- DDD:占空比,Buck电路占空比计算公式为 D=VOUTVIND = \frac{V_{OUT}}{V_{IN}}D=VINVOUT,无单位,反映开关管导通时间占比;

- fSWf_{SW}fSW:芯片开关频率,单位Hz(赫兹),由DCDC芯片规格书确定;

- ΔVIN\Delta V_{IN}ΔVIN:允许的输入纹波电压峰峰值,一般取输入电压的1%~3%,小噪声电路可取0.5%,单位V(伏特);

- 其余参数与输入电流公式一致。

(2)简化实用公式(工程常用,忽略效率微调)

公式:CIN≥IOUT×VOUT×(VIN−VOUT)fSW×VIN2×ΔVINC_{IN} \geq \frac{I_{OUT} \times V_{OUT} \times (V_{IN} - V_{OUT})}{f_{SW} \times V_{IN}^2 \times \Delta V_{IN}}CIN≥fSW×VIN2×ΔVINIOUT×VOUT×(VIN−VOUT)

说明:该公式无需单独计算输入纹波电流和占空比,直接代入输出参数即可快速估算输入电容最小容量,适合现场快速选型,误差在工程允许范围内。

3. 实际工程计算实例

已知设计参数(常规Buck电路):

Buck电路,输入电压VIN=12VV_{IN}=12VVIN=12V,输出电压VOUT=5VV_{OUT}=5VVOUT=5V,最大输出电流IOUT=2AI_{OUT}=2AIOUT=2A,开关频率fSW=500kHzf_{SW}=500kHzfSW=500kHz,转换效率η=0.9\eta=0.9η=0.9,允许输入纹波电压ΔVIN=0.24V\Delta V_{IN}=0.24VΔVIN=0.24V(12V的2%,符合常规纹波要求)。

(1)计算输入平均电流

IIN(AVG)=VOUT×IOUTη×VIN=5V×2A0.9×12V=1010.8≈0.926AI_{IN(AVG)} = \frac{V_{OUT} \times I_{OUT}}{\eta \times V_{IN}} = \frac{5V \times 2A}{0.9 \times 12V} = \frac{10}{10.8} ≈ 0.926AIIN(AVG)=η×VINVOUT×IOUT=0.9×12V5V×2A=10.810≈0.926A

结论:外部供电进线的平均电流约为0.93A,可作为外部电源选型参考。

(2)计算输入纹波电流峰值

IIN(RIPPLE)=IOUT×VOUT×(VIN−VOUT)VIN2=2A×5V×(12V−5V)12V2≈2×0.493≈0.986AI_{IN(RIPPLE)} = I_{OUT} \times \sqrt{\frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN}^2}} = 2A \times \sqrt{\frac{5V \times (12V - 5V)}{12V^2}} ≈ 2 \times 0.493 ≈ 0.986AIIN(RIPPLE)=IOUT×VIN2VOUT×(VIN−VOUT) =2A×12V25V×(12V−5V) ≈2×0.493≈0.986A

结论:输入环路的纹波电流峰值约为0.99A,是输入电容选型的核心依据。

(3)计算占空比D

D=VOUTVIN=5V12V≈0.417D = \frac{V_{OUT}}{V_{IN}} = \frac{5V}{12V} ≈ 0.417D=VINVOUT=12V5V≈0.417

结论:Buck电路占空比约为41.7%,反映上管导通时间占比。

(4)计算输入电容最小容量

CIN≥IIN(RIPPLE)×(1−D)fSW×ΔVIN=0.986A×(1−0.417)500000Hz×0.24V≈0.575120000≈4.79×10−6F≈4.79μFC_{IN} \geq \frac{I_{IN(RIPPLE)} \times (1 - D)}{f_{SW} \times \Delta V_{IN}} = \frac{0.986A \times (1 - 0.417)}{500000Hz \times 0.24V} ≈ \frac{0.575}{120000} ≈ 4.79×10^{-6}F ≈ 4.79μFCIN≥fSW×ΔVINIIN(RIPPLE)×(1−D)=500000Hz×0.24V0.986A×(1−0.417)≈1200000.575≈4.79×10−6F≈4.79μF

结论:输入电容最小所需容量约为4.8μF,实际选型需考虑容差和高频特性。

(5)工程实际选型建议

理论最小容量约4.8μF,考虑电容容值偏差(一般±10%~±20%)、温度漂移、高频滤波需求,实际选型为:10μF高频陶瓷电容(X7R材质)+ 22μF固态电容并联 。

说明:陶瓷电容负责吸收高频纹波、应对电流突变,固态电容负责储存能量、稳定低频电压,两者并联兼顾滤波效果和储能能力,完全满足该电路的输入需求,也贴合我们讨论中"输入电容就近贴装、多容值并联"的原则。

4. 升压/升降压电路输入电流公式补充

通用输入平均电流公式:IIN(AVG)=POUTη×VINI_{IN(AVG)} = \frac{P_{OUT}}{\eta \times V_{IN}}IIN(AVG)=η×VINPOUT

说明:

- POUTP_{OUT}POUT:输出功率,单位W(瓦特),计算公式为POUT=VOUT×IOUTP_{OUT}=V_{OUT}×I_{OUT}POUT=VOUT×IOUT;

- 其余参数与Buck电路一致;

- 适用场景:所有开关电源拓扑(升压、升降压),其中升压电路中输入电流大于输出电流,纹波电流更大,输入电容容量需按此公式计算结果放大1.2~1.5倍,避免纹波超标。

四、关键实测答疑:理论有输入电流突变,为何示波器看供电端波形很平滑?

1.明明理论上输入环路存在剧烈电流突变,上管会切断通路,为什么示波器测外部供电进线,看不到尖锐电流突变、波形一直平顺?

答:这一条完全贴合核心逻辑------输入电容是永久并联在整机供电输入端,永远不会被MOS管切断;依靠前端母线持续对输入电容充电补能,把外部进线电流彻底抹平,具体原理分层讲透,结合我们全程讨论的重点:

第一,抓住最核心本质:输入电容全程并联、永不脱网,前端电源一直在给电容续流充电。

DCDC上MOS管开通/关断,只切断「外部电源→MOS管→电感」这条内部开关主通路;但靠近芯片的输入滤波电容、主输入储能电容,是死死并联在外部供电母线上的,MOS管关断瞬间,电容绝不会断电、绝不会脱离供电回路。

当内部上管突然关断时,整个过程分为两步,完美缓冲电流突变:

① 瞬时峰值抽流,先由就近并联的输入电容瞬间放电,为内部开关回路提供能量,扛下全部尖锐突变------这也是我们之前强调"输入电容就近贴装、按公式选型"的核心原因;

② 电容放出少量电荷、电压轻微跌落的同时,外部主供电会立刻、持续反向给这个并联电容充电,补满电压与电荷,维持电容的储能状态。

这个「电容放电供内部突变→前端电源缓慢充电补电容」的动态循环,是连续不间断的。站在外部供电进线的视角看:它永远只在做一件事------平稳、持续给输入电容缓慢充电补能量,没有突然断流、也没有突然猛抽电流;内部MOS管那种一刀切断的剧烈突变,被电容的充放电循环完美承接、隐藏,外部进线电流自然看不到任何陡变。

第二,严格区分两条完全独立的电流回路(我们全程反复强调,避免混淆):

① 内部开关小环路电流:MOS管、就近输入电容、SW节点之间,这里真实存在通断、真实存在超高di/dt突变,是EMC最大源头,也是我们布局时优先压制的区域;

② 外部进线总线电流:只负责稳稳给并联的输入电容长期补电、慢慢充电,全程连续顺滑,没有突变。

示波器只要夹在外部进线测,测的永远是第二条「缓慢补电的充电电流」,根本测不到第一条内部开关的突变电流;不是突变消失了,是突变被电容隔离在内部小闭环里,外部无法检测到。

第三,叠加辅助因素进一步加固平滑效果(补充说明,贴合实测场景):

- 就近高频MLCC小电容,纳秒级吸收最尖锐的开关尖峰,内部就地消化,不向外扩散,进一步减少突变对外的影响;

- 示波器探头带宽、接地方式、电流采样的响应速度限制------普通探头带宽不足,会把极窄的瞬时尖峰直接滤除,只能拍到平缓的充电均值;探头接地绕圈、采样线过长,也会钝化尖峰,导致看不到突变;

- 前端适配器、前级大电解、母线储能的惯性作用------这些器件储能极大、响应偏慢,哪怕后端DCDC输入一瞬间抽尖锐脉冲电流,前级大储能单元会瞬间补流,把外部进线的电流波动牢牢按住,让进线侧电流变得非常平稳;

- 优质PCB布局的抑制作用------合规PCB会严格压缩输入环路面积、缩短VIN走线、强化地回流,把高频突变的能量锁死在极小区域,不耦合到供电主线,让外部波形进一步干净。

第四,落地总结:

① 内部上管开关的电流突变100%真实存在,EMC风险丝毫未降,输入环路依旧是PCB布局最高优先级,不能因为示波器看不到突变就放松布局要求;

② 示波器看不到外部突变,核心原因就是:输入电容永久并联、前端电源持续充电补能,用电容充放电把突变"藏在内部",外部进线只保留顺滑的补电电流;

③ 也正因这个原理,前文的输入电容计算公式、必须就近贴装、多容值并联选型才至关重要:电容容量不足、贴远了,补电+吸峰能力不够,突变就会漏到外部,示波器立马能看到尖峰,EMC也会直接超标。

五、输入环路与输出环路EMC优先级及电流大小问题

1. 从EMC角度,输入环路、输出环路1(芯片-电感-主电容-芯片)、输出环路2(芯片-电感-主电容-负载-芯片)三个区域,哪个影响最大?优先级怎么排?

答 :从EMC辐射、噪声干扰的严重程度和影响优先级来看,三个区域的优先级排序为:输入环路 > 输出环路1 > 输出环路2,这是结合开关电源的工作原理、电流变化率(di/dt)、辐射风险综合得出的结论,同时贴合我们全程讨论的核心逻辑,具体分析如下:

(1)第一优先级:输入环路(EMC风险最高)

输入环路是电流变化率(di/dt)最高、EMC辐射最强烈的区域,也是PCB布局中必须最先保证、最核心的区域。

核心原因:输入环路包含上管、输入电容,上管开启和关断的瞬间,输入电流会出现剧烈的突变------输入环路没有电感的缓冲作用,电流瞬间通断,di/dt极大,会产生极强的高频辐射和噪声,是开关电源EMC问题的主要源头。

结合上述计算实例,输入纹波电流峰值接近1A,突变幅度极大,若输入环路布局不当(环路面积大、走线长、输入电容远离芯片),会直接导致辐射超标、干扰周边电路,甚至无法通过EMC测试,所以必须优先保证输入环路的紧凑布局,且输入电容选型需严格按照公式计算,避免容量不足导致纹波放大。

(2)第二优先级:输出环路1(对应输出路径一:续流内环)

输出环路1是芯片、电感、主输出电容形成的闭合小回路,也就是我们之前定义的"开关续流内环"。

虽然有电感缓冲电流,电流变化率远低于输入环路,但依旧存在开关动作带来的纹波电流和电流切换,是输出噪声的核心传递路径,也存在一定的EMC辐射风险。

该区域布局不当(主电容远离电感、环路面积大),会导致输出纹波增大、滤波失效,同时产生二次辐射,影响EMC性能,因此需要第二优先级保证紧凑布局,收紧环路面积。

(3)第三优先级:输出环路2(对应输出路径二:远端负载外环)

输出环路2包含远端负载和长线,也就是我们之前定义的"远端负载供电外环"。

经过输入环路、输出环路1的双重滤波后,高频噪声和纹波已经被大幅衰减,该环路的电流以直流分量为主,高频成分极少,电流变化率(di/dt)极低,EMC辐射风险远低于前两个区域。

布局时只需在负载端加辅助电容、尽量缩短回流线即可,无需优先布局,重点保证长线走线的合理性,避免引入额外寄生参数。

2. 输入环路的电流为什么比输出环路电流变化更剧烈?依据是什么?

答:核心依据是电感的缓冲作用+开关动作的电流特性+功率守恒原理,两者的差异非常明显,结合我们全程讨论的重点,具体分析如下:

(1)输入环路:无电感缓冲,电流突变剧烈

输入环路是硬开关回路,没有电感的限流和缓冲作用,上管开启时,输入电流瞬间从0上升到峰值;上管关断时,输入电流瞬间从峰值降到0,电流通断是瞬间完成的,电流变化率(di/dt)极高,属于"脉冲式大电流突变"。

结合之前的计算实例,输入纹波电流峰值接近1A,瞬间通断产生的di/dt远超输出环路,会产生极强的高频电磁场,辐射干扰能力极强,这也是输入环路EMC风险最高的核心原因------EMC风险的核心影响因素是电流变化率,而非平均电流大小。

(2)输出环路:有电感缓冲,电流无突变

输出环路有电感串联,电感的"电流不能突变"特性,会强行将电流的快速变化转化为缓慢的连续变化,即使开关管动作,电感电流也只是缓慢上升或下降,没有瞬间的通断,电流变化率(di/dt)极低。

输出环路的电流始终是连续的,只是回路通路切换(比如路径一和路径二的切换),不存在输入环路那种瞬间的电流剧变,因此电流变化平缓,噪声和辐射远小于输入环路。

另外,从功率守恒角度补充说明:Buck电路中输入电压高于输出电压,输入电流的平均值小于输出电流平均值,但输入电流的峰值、变化率、突变幅度远大于输出电流------这也进一步证明,不能用平均电流大小判断EMC风险,核心要看电流变化率(di/dt),同时输入电容容量需严格按纹波电流计算,保证能吸收突变电流,抑制EMC干扰。

3. 输出环路和输入环路相比,哪个更干净?为什么?

答:输出环路比输入环路干净很多,尤其是输出环路2(远端负载外环),几乎没有高频突变和噪声,核心原因有两点,贴合我们全程讨论的逻辑:

第一,输出环路有电感的缓冲作用,彻底消除了电流的瞬间突变------输出环路串联的电感,会强行将开关动作带来的电流变化转化为平缓、连续的变化,没有输入环路那种脉冲式的剧烈电流变化,从源头减少了噪声和辐射。

第二,输出环路有输出主电容+续流二极管的双重滤波和稳压作用------主电容滤除高频纹波、储存能量,续流二极管保证电流连续,两者配合进一步平滑电流和电压,减少噪声传递;而输入环路只有输入电容,没有电感缓冲,噪声和突变无法被有效抑制,只能依靠输入电容吸收,因此输入环路的噪声和突变更明显。

简单来说,输入环路是"高频突变、强辐射"的脏回路,输出环路(尤其是远端负载外环)是"连续平缓、弱辐射"的干净回路,这也是布局时优先处理输入环路的核心原因。

4. 三个环路布局的核心注意事项分别是什么?

答:结合EMC优先级,每个环路的布局核心要点的如下,完全贴合我们全程讨论的结论,可直接用于PCB设计:

(1)输入环路(最高优先级)

- 输入电容必须紧邻芯片的输入引脚和地引脚,缩短输入电容与上管、芯片电源端的走线,最小化输入环路面积,杜绝长走线、大环路------这是抑制输入环路EMC辐射的关键;

- 输入电容按公式计算选型,优先选用高频特性好的陶瓷电容+大容量电解/固态电容组合,快速吸收输入突变电流,避免容量不足导致纹波超标;

- 输入环路的走线尽量短、粗,减少寄生电感和电阻,避免突变电流产生的高压尖峰;

- 输入电容的接地端尽量靠近芯片地,减少接地阻抗,提升滤波效果。

(2)输出环路1(次高优先级,对应续流内环)

- 主输出电容紧邻电感输出端和芯片地,电感与芯片SW引脚的走线尽量短且粗,减小环路面积,避免寄生电感影响滤波效果;

- 电感下方尽量不走线,减少干扰耦合,避免电感的磁场干扰周边电路;

- 主输出电容的接地端与芯片地、电感接地端尽量靠近,形成完整的小闭环,提升续流和滤波效果。

(3)输出环路2(一般优先级,对应远端负载外环)

- 负载端并联辅助电容(0.1μF~10μF高频陶瓷电容,必要时加中等容量电容),稳定负载端电压;

- 缩短负载的电源走线和回流地线,尽量让电源走线和地线并行,减小远端环路面积,避免长线引入寄生参数;

- 负载回流地线尽量短,避免形成大的辐射环路,减少EMC风险;

- 长线走线尽量远离输入环路和输出环路1,避免干扰耦合。

六、核心技术要点总结

1. 电感核心特性

- 电感电流大小和方向均不能突变,续流二极管仅提供续流通道,不改变电流方向;

- 输出环路无实质性状态突变,仅在续流内环(路径一)存在局部电流切换,且被电感缓冲。

2. 实测波形核心逻辑

- 输入MOS管开关突变100%真实存在,EMC风险未降;

- 示波器测外部供电端无突变,核心原因是:输入电容永久并联在供电端,前端电源持续给电容充电补能,用电容充放电掩盖外部进线突变。

3. 输出电容布局原则

- 主电容:紧邻电感和芯片,服务续流内环,滤除高频纹波、吸收突变;

- 远端辅助电容:靠近负载,服务负载外环,补偿长线寄生、应对负载突变;

- 负载突变大时,负载端并联中等容量电容,兼顾快速响应和储能。

4. 输入电流与电容计算

- 输入平均电流:IIN(AVG)=VOUT×IOUTη×VINI_{IN(AVG)} = \frac{V_{OUT} \times I_{OUT}}{\eta \times V_{IN}}IIN(AVG)=η×VINVOUT×IOUT

- 输入纹波电流峰值:IIN(RIPPLE)=IOUT×VOUT×(VIN−VOUT)VIN2I_{IN(RIPPLE)} = I_{OUT} \times \sqrt{\frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN}^2}}IIN(RIPPLE)=IOUT×VIN2VOUT×(VIN−VOUT)

- 输入电容容量:CIN≥IIN(RIPPLE)×(1−D)fSW×ΔVINC_{IN} \geq \frac{I_{IN(RIPPLE)} \times (1 - D)}{f_{SW} \times \Delta V_{IN}}CIN≥fSW×ΔVINIIN(RIPPLE)×(1−D)

- 工程选型:理论容量基础上放大1.2~2倍,并联高低频电容,就近贴装。

5. EMC布局优先级

- 最高优先级:输入环路(无电感缓冲,突变最剧烈,EMC风险最高);

- 次高优先级:输出环路1(续流内环,有局部突变,需收紧环路);

- 一般优先级:输出环路2(负载外环,无明显突变,辅助滤波即可)。

6. 电流与EMC关系

- EMC风险的核心影响因素是电流变化率(di/dt),而非平均电流大小;

- 输入环路di/dt远高于输出环路,因此输入环路EMC影响最大,需优先优化。