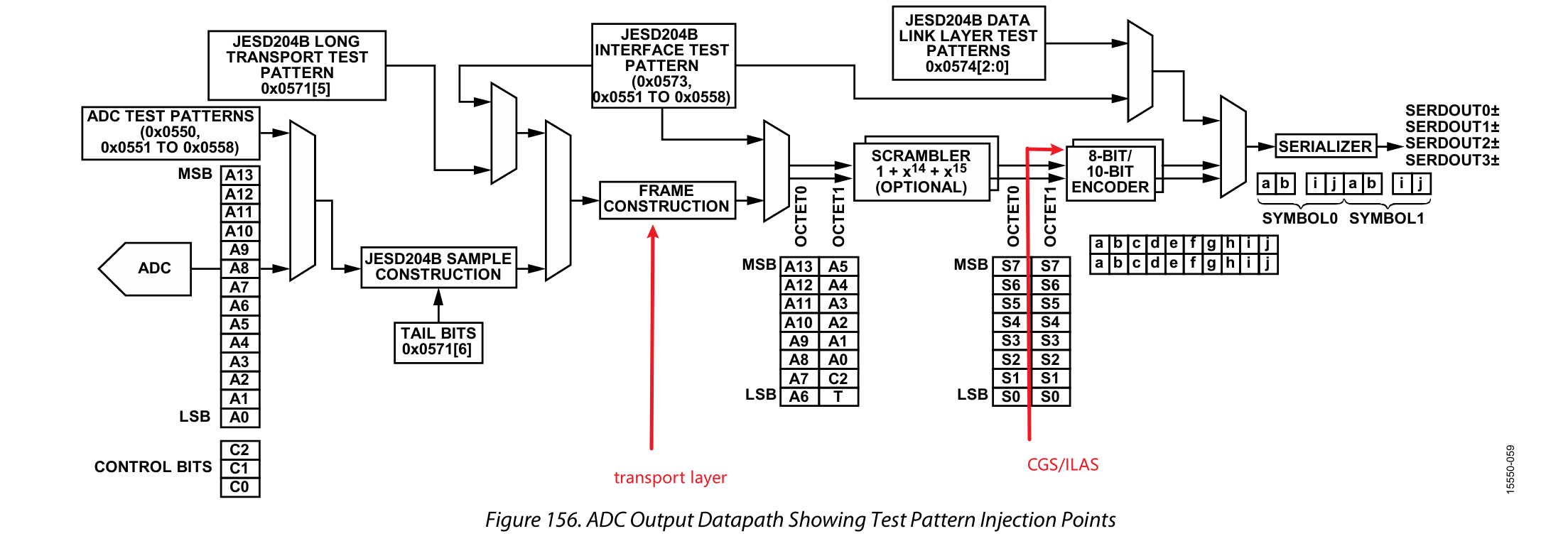

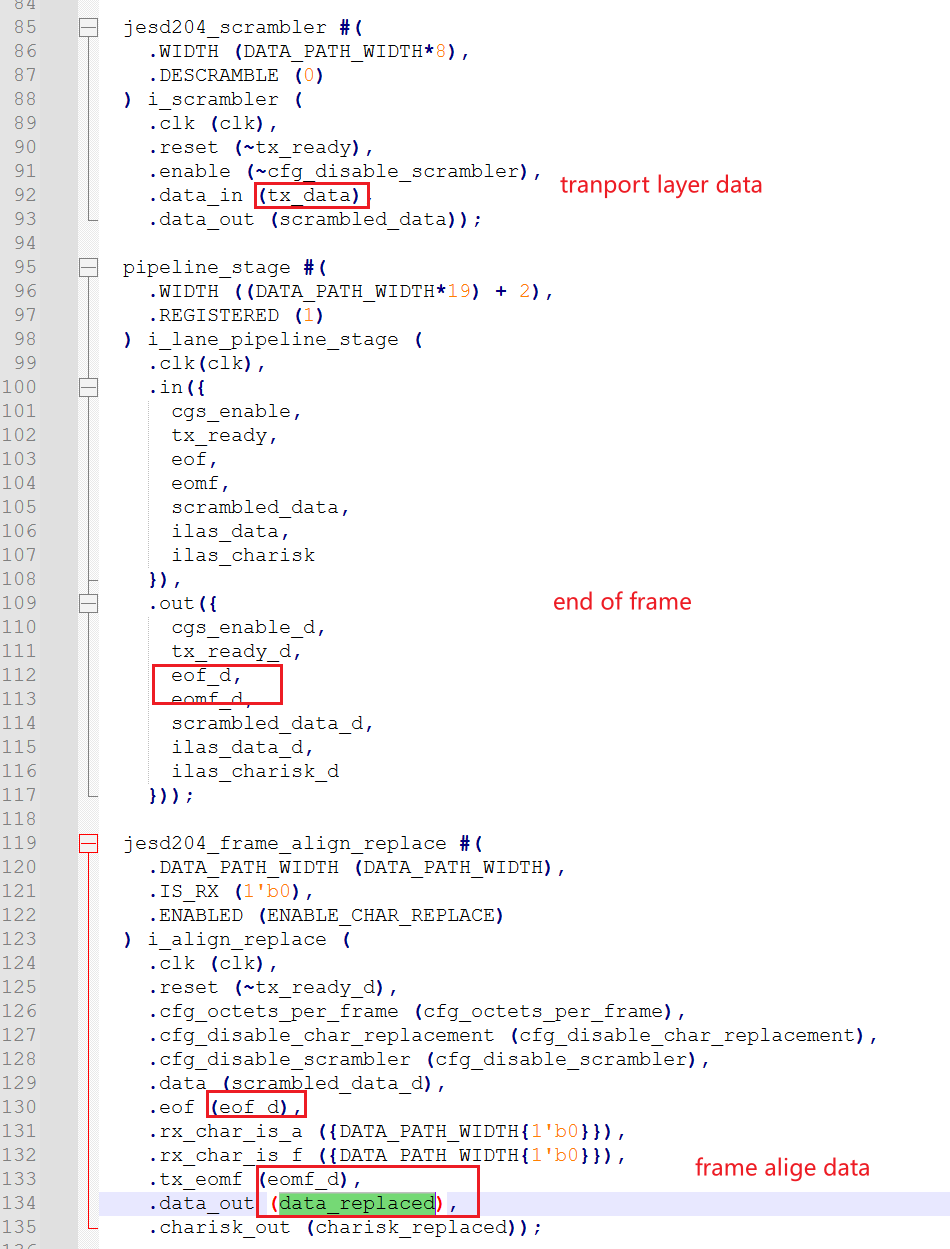

jesd 204b分为物理层、数据链路层和传输层,在传输层和数据链路层之前存在着一个可选的扰码器。物理层负责并行数据的串行化,在实际的物理通道中发送数据;数据链路层主要实现8b/10b编码、CGS和 ILAS;传输层实现数据在不同lane上的映射,但在很多场景下,M会等于L,且S=F',此时传输层基本上可以等同于bypass。我们看一下ADI的datashhet中的ADC test partern的数据流向图,其实也是一个完整的JESD 204B TX的数据流向图。

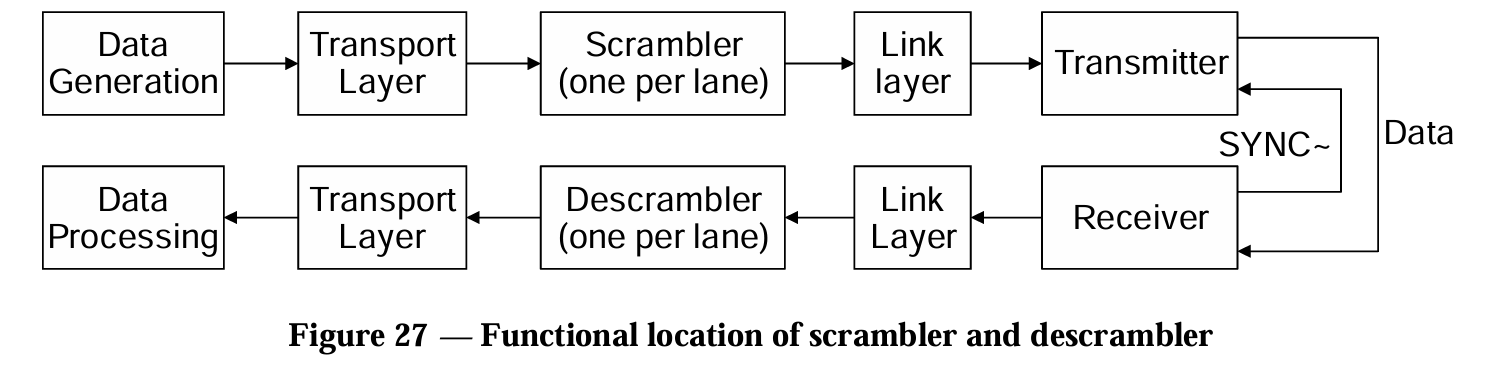

下图是204b协议原文中的数据流向图:

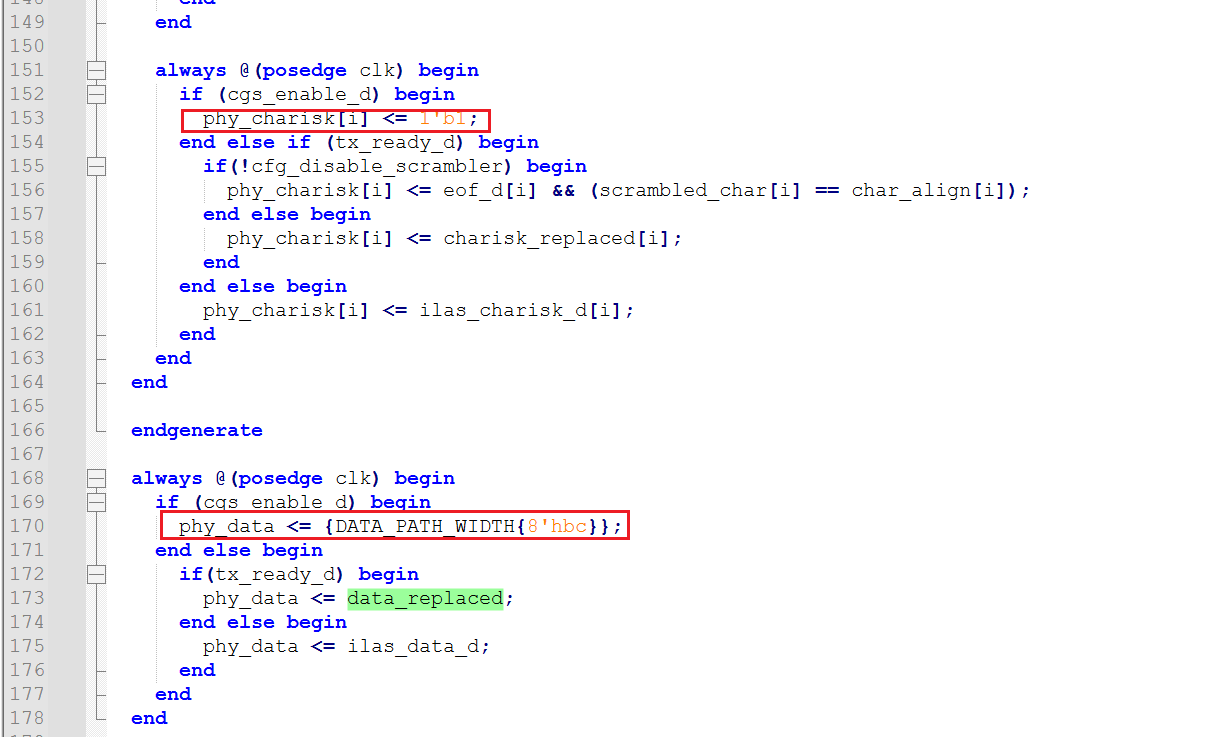

首先来看一下数据链路层,数据链路层的功能如下:

1、8b/10b编码

2、链路操作:

(1) cgs:

这个比较简单,网上内容也比较多,不作介绍;

(2) 大小端模式:JESD 204B使用大端模式,MSB first;

(3)初始帧对齐:

TX:在CGS期间,TX始终发送/K28.5/符号的完整帧,CGS结束后,TX发送有效数据,如果TX发出了ILAs序列,第一个非/K28.5/符号是为/K28.0/。我其实没有弄清楚协议中为什么这么说,因为ILAs应该不是一个可选的过程,我的理解协议作者可能是认为可能存在链路层的测试模式,协议中明确的说了,RX设备应存在抑制 ILAS缺失报错的能力,以使得测试模式能够得以进行来测试误码率。

RX:RX以第一个非/K28.5/符号标记帧的开始, 且以F个八位字节开始一个新的帧。也就是说,RX应存在序列检测器(8b/10b decoder前),检测从物理层中获得的数据中的控制字符。

(4)帧对齐和校正

TX:

RX:

虽然jesd 204b协议将8b/10b编码划分到了数据链路层,但是在大部分的应用下,8b/10b编码被认为是PCS层,所以FPGA IP中如果不包含phy,那么IP链路层输出需要charisk信号用以指示控制字符,因为8b/10b编码对控制字符和普通数据的编码是不一样的。

(5)ILAs

(6)lane对齐和校正