第一部分:存储芯片生产技术原理与物理基础

存储芯片是现代信息社会的 "数据基石"------ 其本质是通过半导体器件的物理特性实现二进制数据的存储与读取。2026 年,随着 AI 算力需求的爆发,存储芯片的技术演进已从 "平面微缩" 转向 "垂直堆叠 + 架构创新",以突破摩尔定律的物理极限。

1.1 存储芯片的定义与核心功能

从物理本质看,存储芯片是利用半导体材料的电荷存储 (如电容、浮栅)或电阻 / 磁阻相变(如 ReRAM、MRAM)特性,将二进制数据(0/1)编码为可检测电信号的集成电路。其核心功能是在计算系统中完成 "数据写入 - 保持 - 读取" 的闭环:写入是通过外部电场改变存储单元的物理状态,保持是通过材料特性稳定存储状态,读取是通过检测存储单元的电信号还原数据。

在计算系统的层级结构中,存储芯片处于 "算力与数据的中间枢纽" 位置:CPU/GPU 作为 "运算核心",其每秒可处理的指令数(IPS)完全依赖存储芯片的带宽 ------ 若存储带宽不足,即使 GPU 算力提升 10 倍,实际运算效率也会因数据等待降至 1/3 以下(英伟达 GTC 2026 白皮书)。这一特性决定了存储芯片的设计目标与逻辑芯片存在本质差异:逻辑芯片追求单晶体管的开关速度,存储芯片则追求阵列的存储密度、数据保持时间与读写能效。

1.2 主流存储芯片技术原理

2026 年,全球存储芯片市场规模达 875 亿美元,其中易失性存储(DRAM)占 52%、非易失性存储(NAND/NOR Flash)占 45%、新兴存储(MRAM/ReRAM/PCRAM)占 3%。不同类型的存储芯片对应不同的物理机制与应用场景,其技术特性的差异直接决定了在计算系统中的定位。

1.2.1 动态随机存取存储器(DRAM):易失性存储的核心

DRAM 是服务器、PC、移动设备的 "主存" 核心,其技术演进的核心逻辑是 "在有限面积内存储更多电荷"。传统 DRAM 采用 1T1C(1 个晶体管 + 1 个电容)单元结构:电容的高电平代表 "1",低电平代表 "0";晶体管作为开关控制电容的充放电,数据读取时会消耗电容电荷,因此需要每 64ms 刷新一次 ------ 这也是 "动态"(Dynamic)一词的由来。

当工艺节点进入 10nm 级后,平面电容的存储面积与电荷保持能力形成了不可调和的矛盾:电容尺寸缩小会导致漏电流指数级上升,数据保持时间从毫秒级降至微秒级,无法满足服务器场景的稳定性需求。为突破这一物理极限,三星、SK 海力士等厂商在 2026 年量产的 d1c 节点(11nm)中,全面采用4F² 垂直沟道晶体管(VCT) 架构:将水平晶体管的沟道垂直竖立,源极、沟道、漏极呈柱状排列,字线与位线间距均优化至 2F(F 为最小特征尺寸)。这一设计将单元面积从传统 6F² 缩小约 30%,同时通过将 CMOS 电路移至存储阵列下方(CBA 架构),进一步提升了集成度;三星数据显示,该架构可使每片晶圆的 DRAM 芯片产量提升约 20%,良率稳定在 65% 以上。

为彻底摆脱电容的物理限制,南京大学缪峰团队与京东方在 2026 年研发的 IGZO(铟镓锌氧化物)沟道 DRAM,采用 4T1C 单元结构,漏电流低至 10⁻⁸A,可在零保持电压下实现 8500 秒的数据保持时间 ------ 这一特性使 DRAM 具备了 "准非易失性",若量产可将服务器待机功耗降低 90% 以上。该技术的核心突破在于 IGZO 材料的高迁移率与低漏电流特性:IGZO 的电子迁移率是传统硅的 20-50 倍,同时漏电流仅为硅的 1/1000,完美平衡了读写速度与数据保持能力。

1.2.2 NAND Flash:非易失性存储的主力

NAND Flash 是 SSD、U 盘、数据中心存储的核心,其技术演进的核心逻辑是 "从平面扩展到垂直堆叠"------2026 年,3D NAND 已占据 91.2% 的 NAND 市场份额,成为绝对主流。

3D NAND 的存储单元结构经历了从浮栅(FG)到电荷陷阱(CTF)的全面迭代:浮栅结构将电荷存储在悬浮栅极中,绝缘层为 SiO₂,优点是读写速度快,但在 200 层以上堆叠时,电子泄漏风险会指数级上升(每增加 50 层,泄漏率提升约 20%);电荷陷阱结构则将电荷存储在氮化硅(Si₃N₄)介质层中,通过阻挡层隔离,更适合垂直堆叠 ------2026 年除美光外,头部厂商均已全面采用 CTF 架构,其数据保持时间可达 10 年以上。

堆叠层数是 3D NAND 技术实力的核心指标:2026 年长江存储实现 294 层 Xtacking®3.0 量产,铠侠推出 332 层 BiCS 10,三星计划 2026 年底量产 300 层以上 V-NAND。堆叠层数的提升直接降低单位容量成本:每增加 100 层,单位 GB 成本可下降约 30%(研精毕智,2026)。为进一步提升性能,长江存储的 Xtacking® 技术将 CMOS 电路与存储阵列分别在不同晶圆上加工,再通过混合键合工艺连接 ------ 这一设计可将存储阵列的堆叠工艺与 CMOS 的逻辑工艺解耦,既不影响堆叠层数提升,又能将 I/O 速度提升约 30%,功耗降低约 20%。

1.2.3 高带宽内存(HBM):AI 时代的专属存储

HBM 是为 AI 服务器、高性能计算(HPC)设计的 3D 堆叠 DRAM,核心价值是通过垂直堆叠实现超高带宽 ------2026 年市场规模占存储芯片总规模的 3%,但营收占比超 15%,是头部厂商的核心利润来源。

HBM 的技术原理是通过硅通孔(TSV)将多颗 DRAM 裸片垂直堆叠,再通过微凸点键合与基底芯片连接,最终通过中介层与 GPU 封装在一起。2026 年量产的 HBM4 实现了两大突破:一是带宽提升至 2.8TB/s(美光数据),是 HBM3E 的 2.3 倍;二是功耗降低约 20%,这得益于低电压 TSV 技术(工作电压从 1.2V 降至 0.9V)与电源分配网络(PDN)优化 ------PDN 可将电源噪声降低 30%,进一步提升信号稳定性。

HBM 的制造工艺瓶颈主要集中在 TSV 刻蚀与堆叠良率:TSV 刻蚀需实现深宽比≥50:1 的通孔,任何偏差都会导致信号短路或衰减;堆叠良率随层数增加呈指数级下降 ------ 每增加一层堆叠,良率约下降 5%,因此 12 层堆叠的 HBM 良率仅约 50%-60%(36 氪,2026)。此外,HBM 的生产周期比普通 DRAM 长 1.5-2 个月,总周期通常超过半年,进一步推高了制造成本。

1.2.4 新兴非易失性存储(MRAM/ReRAM/PCRAM)

2026 年,新兴非易失性存储仍处于产业化初期,但在存算一体场景实现了关键突破 ------ 存算一体是解决 "内存墙" 问题的核心方向,其逻辑是将计算单元嵌入存储阵列,避免数据在存储与计算单元之间的频繁传输,从而大幅提升能效。

- MRAM(磁阻 RAM) :基于电子自旋力矩写入信息,通过磁隧道结(MTJ)的磁电阻变化读出数据。2026 年 MRAM 的最大应用场景是汽车电子(市场占比 24%),尤其是自动驾驶域控制器 ------ 其可在 - 40℃~125℃的宽温域下稳定工作,读写速度达 200MHz,写入吞吐量达 10.4MB/s(瑞萨电子,2026)。台积电在 2026 年解决了 MRAM 的核心技术瓶颈:在钨层中插入超薄钴层,抑制了 β 相钨向 α 相的相变,使自旋霍尔角从 - 0.01 提升至 - 0.08,自旋轨道力矩翻转效率提升了 8 倍。此外,驰拓科技的磁屏蔽封装技术将 MRAM 的写入抗磁能力从 6mT 提升至 63mT,数据保持抗磁能力从 75mT 提升至 360mT,达到常规磁铁免疫水平,额外封装成本仅约 1 元 / 颗。

- ReRAM(阻变 RAM) :通过电压调控介质层的电阻状态实现数据存储,具备非易失性、高速读写、低功耗与高密度集成等优势。2026 年合肥睿科微电子采用 55nm 成熟 CMOS 制程,实现了 ReRAM 存算一体芯片的量产 ------ 其 AI 推理能效达 142 TOPS/W,较传统 GPU 提升了约 100 倍。该芯片采用 2/2/4 位的输入 / 权重 / 输出精度,在 MNIST 和 CIFAR-10 数据集上的推理精度仅下降了 0.8% 和 3.3%,验证了其在可扩展性、高吞吐量和能效方面的优越性。

- PCRAM(相变 RAM) :通过硫系化合物(如 Ge₂Sb₂Te₅)的晶态 / 非晶态相变存储数据。北京时代全芯是国内唯一实现 PCRAM 量产的企业,其产品已应用于航天军工场景 ------ 通过掺杂氮元素,PCRAM 的非晶态稳定性提升了约 50%,数据保持时间可达 10 年以上。此外,纳思达与中科院上海微系统所合作研发的 PCRAM 已通过车规级 AECQ100 认证,可在 - 40℃~125℃的环境下稳定工作。

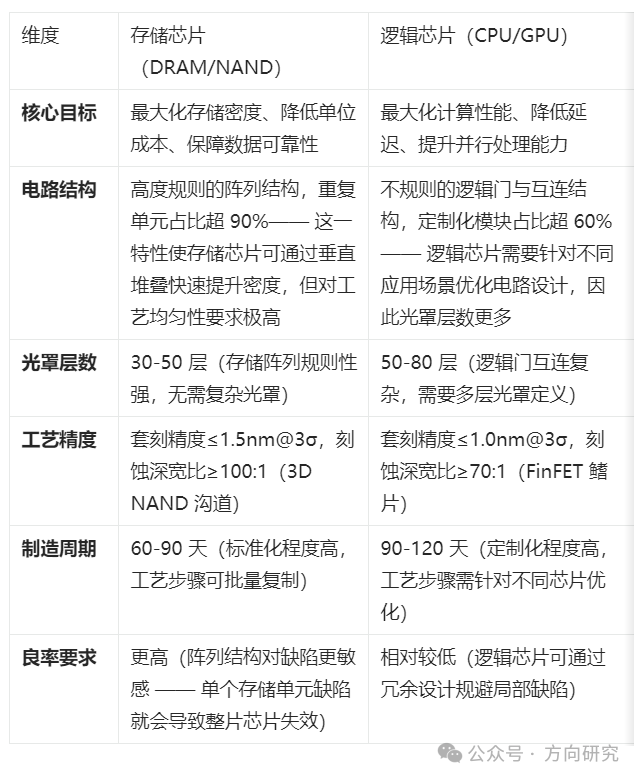

1.3 存储芯片与逻辑芯片的设计制造差异

存储芯片与逻辑芯片的功能定位差异,决定了两者在设计哲学与制造工艺上的根本性分野:逻辑芯片追求 "计算性能最大化",存储芯片追求 "存储密度与能效最大化"。这种差异并非简单的参数不同,而是从电路架构到工艺控制的全链条区别。

上述差异的核心逻辑是:存储芯片的规则阵列允许通过垂直堆叠快速提升密度,但任何局部工艺偏差都会导致大规模失效;逻辑芯片的定制化结构需要更复杂的光罩与工艺,但冗余设计可容忍局部缺陷。例如,存储芯片的刻蚀深宽比要求更高(3D NAND 沟道达 100:1),而逻辑芯片的套刻精度要求更严(≤1.0nm@3σ)。

第二部分:存储芯片制造全流程与核心工艺详解

存储芯片制造是半导体工业的 "皇冠上的明珠"------ 其涉及超 500 道工序,对设备精度、材料纯度与工艺控制的要求均达到了人类工业的极限。2026 年,随着 3D 堆叠与 HBM 技术的普及,存储芯片制造的复杂度较 2020 年提升了 3 倍以上。

2.1 原材料准备:硅片与特种气体

存储芯片制造的起点是超高纯度的原材料,任何杂质都会导致芯片性能下降甚至失效 ------ 例如,硅片纯度每降低一个数量级,存储芯片的良率就会下降约 20%。

- 电子级多晶硅:纯度要求达到 11-13N(即 99.999999999%---99.99999999999%)------ 这意味着每 1000 亿个硅原子中,杂质原子数不得超过 1 个。鑫华科技是国内电子级多晶硅的龙头企业,2024 年市占率超过 50%,其产品已通过长江存储、长鑫存储的认证,打破了海外厂商的垄断。

- 硅片制备:采用直拉法(CZ)或区熔法(FZ)制备单晶硅棒 ------ 直拉法适合制备大尺寸硅片(如 12 英寸),成本较低,是存储芯片的主流选择;区熔法制备的硅片电阻率更高,适合特种存储场景。硅棒经切割、研磨、抛光后,形成厚度约 775μm 的 12 英寸晶圆,表面粗糙度需控制在 0.1nm 以下(中科院半导体所,2026)。2026 年,12 英寸硅片占存储芯片制造的 90% 以上,其平整度要求达到原子级 ------ 任何超过 0.5nm 的凸起都会导致后续光刻失准。

- 特种气体与光刻胶:光刻混合气的配方是行业顶级机密 ------ 华特气体作为国内唯一通过 ASML 光刻气认证的企业,其 Ar/F/Ne、Kr/F/Ne 等 4 种核心配方的比例误差≤0.0001%,否则会导致光刻波长偏移,芯片直接报废。光刻胶方面,2026 年存储芯片主流采用 ArF 浸没式光刻胶,分辨率可达 22nm,国产厂商彤程新材的 KrF 光刻胶已实现量产,市占率超 40%;徐州博康的 HTK 系列光刻胶杂质含量 < 1ppb,吸收系数 < 20%,可满足 EUV 光刻的严格要求。

2.2 晶圆制造(前道工艺)

晶圆制造是存储芯片制造的核心环节,涉及薄膜沉积、光刻、刻蚀、掺杂、热处理等关键步骤,每一步都需精确控制 ------ 例如,光刻的套刻精度偏差若超过 1.5nm,整批晶圆都会报废。

2.2.1 薄膜沉积(Thin Film Deposition)

薄膜沉积是在晶圆表面生长或沉积绝缘层、导电层、半导体层的过程,是 3D NAND 堆叠的基础 ------ 每一层堆叠都需要精确的薄膜厚度控制,偏差≤±0.5%。

原子层沉积(ALD)是 3D NAND 堆叠的关键技术,其通过交替通入反应前驱体,实现原子级精度的薄膜生长,台阶覆盖率可达 100%(微导纳米 iTomic SPX 设备实测数据)。以 3D NAND 的 ONO(氧化硅 - 氮化硅 - 氧化硅)叠层为例,工艺参数控制极为严格:初始氧化层采用热氧化法在 850℃、O₂+H₂O 氛围下生长 5nm 厚的缓冲层,氮化硅层采用 ALD 法在 300℃下沉积 10nm 厚的电荷陷阱层,顶层氧化层采用 PECVD 法在 400℃下沉积 5nm 厚的阻挡层。若炉管内温差超过 5℃,会导致晶圆中心与边缘的薄膜厚度偏差≥3%,直接影响数据保持时间。

除 ALD 外,PECVD(等离子体增强化学气相沉积)也是存储芯片制造的核心沉积技术 ------ 其通过等离子体增强反应速率,可在较低温度下沉积高质量的绝缘层与导电层。例如,DRAM 的电容介质层采用 PECVD 沉积的 HfZrO 高 k 介质,厚度仅 30-90Å,介电常数是 SiO₂的 5-10 倍,可大幅提升电容密度。

2.2.2 光刻(Photolithography)

光刻是将电路图案从掩模版转移到晶圆表面光刻胶上的过程,是存储芯片微缩的核心瓶颈 ------ 其精度直接决定了存储单元的最小尺寸。2026 年,EUV 光刻已成为存储芯片制造的主流技术,占 DRAM 产能的 30% 以上。

光刻工艺的核心步骤与参数控制达到了极致:

- 涂胶:采用旋转涂胶法,将光刻胶均匀涂覆在晶圆表面,厚度控制在 100-200nm,均匀性偏差≤±2%。涂胶速度需严格控制在 3000-5000rpm,否则会导致边缘厚度偏差超标。

- 烘烤:通过软烘(90-110℃,60-90 秒)去除光刻胶中的溶剂,增强光刻胶与晶圆表面的附着力;硬烘(120-150℃,30-60 秒)进一步固化光刻胶,提高其抗刻蚀能力。

- 对准与曝光:采用 ASML NXE:3800E EUV 光刻机(波长 13.5nm),将掩模版上的图案投射到光刻胶上,套刻精度≤1.5nm@3σ------ 这一精度相当于头发丝直径的 1/50000。EUV 光刻的光源功率需达到 600W 以上,转换效率仅约 2.5%,每一片晶圆的曝光成本约为 1500 美元,占存储芯片制造成本的 30% 以上。

- 显影:采用碱性溶液(如 TMAH)选择性去除曝光区域的光刻胶,形成所需的电路图案,显影时间控制在 30-60 秒,偏差≤±5 秒。显影液浓度需严格控制在 2.38%,否则会导致图案边缘粗糙度超标。

EUV 光刻的核心挑战是光源稳定性与光刻胶性能:光源功率波动若超过 5%,会导致光刻分辨率偏差≥2%;光刻胶的吸光率需控制在 20% 以下,否则会导致曝光剂量翻倍,影响良率。

2.2.3 刻蚀(Etching)

刻蚀是将光刻胶上的图案转移到晶圆底层材料的过程,是 3D NAND 沟道与 DRAM 电容形成的关键 ------ 其深宽比与侧壁粗糙度直接决定了存储芯片的性能。2026 年,干法刻蚀已成为存储芯片制造的主流刻蚀技术,占刻蚀工序的 90% 以上。

干法刻蚀与湿法刻蚀的应用场景存在明确分工:干法刻蚀采用等离子体(如 CF₄、O₂)作为刻蚀介质,具备各向异性,深宽比可达 100:1,是 3D NAND 沟道、DRAM 电容等高深宽比结构的唯一选择;湿法刻蚀采用化学溶液(如 HF)作为刻蚀介质,具备高选择性,但各向异性差,仅用于 SiO₂等薄层材料的刻蚀。例如,3D NAND 的沟道刻蚀采用干法刻蚀,而 ONO 叠层的顶层氧化层刻蚀采用湿法刻蚀。

3D NAND 沟道刻蚀的参数控制达到了原子级:刻蚀深度达 10μm,孔径约 100nm,深宽比≥100:1;刻蚀速率需控制在 100-200nm/min,均匀性偏差≤±2%;侧壁粗糙度≤0.5nm------ 若侧壁粗糙度超标,会导致存储单元的漏电流上升,数据保持时间缩短。中微半导体的 NMC612H 刻蚀机已实现 100:1 深宽比的稳定刻蚀,单腔产能提升 40%,良率稳定在 95% 以上,打破了海外厂商的垄断。

2.2.4 掺杂(Doping)

掺杂是通过离子注入或扩散,改变半导体材料导电类型与电阻率的过程,是调整存储单元阈值电压的关键 ------ 阈值电压的精度直接决定了 DRAM 的读写速度与 NAND 的编程 / 擦除效率。2026 年,离子注入已成为存储芯片掺杂的主流技术,占掺杂工序的 80% 以上。

离子注入的参数控制极为严格:注入能量范围为 0.5-200keV(浅结注入 < 5keV),剂量范围为 10¹³-10¹⁶atoms/cm²,精度误差≤±1%;注入角度需控制在 7° 左右,以避开单晶硅的晶格通道效应 ------ 若角度偏差 1°,会导致离子注入深度偏差≥5%,阈值电压漂移≥10%。例如,DRAM 的沟道掺杂采用 BF₂⁺离子注入,能量 5keV,剂量 10¹⁴atoms/cm²,角度 7°,可精确调整晶体管的阈值电压,提升开关速度。

离子注入的核心挑战是避免沟道效应与阴影效应:倾斜角(7°)可避开单晶硅的晶格通道,防止离子非预期地深入衬底;旋转角可确保在倾斜注入时,晶圆各方向的受力均匀,防止因图形遮蔽导致的掺杂不均。例如,若倾斜角偏差 1°,会导致离子注入深度偏差≥5%,阈值电压漂移≥10%,良率下降≥5%。

2.2.5 热处理(Thermal Processing)

热处理是通过加热晶圆,激活掺杂离子、修复晶格损伤、调整薄膜应力的过程,是离子注入后的必要步骤 ------ 若热处理参数不当,会导致掺杂离子扩散,影响存储单元的性能。2026 年,快速热退火(RTP)已成为存储芯片热处理的主流技术,占热处理工序的 90% 以上。

快速热退火的参数控制达到了毫秒级:峰值温度为 1000-1350℃(BF₂⁺离子需 1100℃,As⁺离子需 1050℃),驻留时间为 1-10 秒,温度均匀性≤±1℃@3σ,热预算控制精度达 0.1℃・s。例如,离子注入后的 RTP 处理可激活 90% 以上的掺杂离子,同时修复 80% 以上的晶格损伤,使晶体管的电流驱动能力提升约 30%。

3D NAND 的尖峰退火工艺是热处理的关键创新:其峰值温度为 950-1050℃,驻留时间仅 1-2 秒,可在激活掺杂离子的同时,避免存储单元的电荷泄漏。这一工艺可将 3D NAND 的编程 / 擦除效率提升约 20%,数据保持时间延长约 30%。

2.2.6 化学机械抛光(CMP)

化学机械抛光是通过化学腐蚀与机械研磨的协同作用,实现晶圆表面全局平坦化的过程,是多层互连与混合键合的基础 ------ 其平整度直接决定了后续工艺的套刻精度。2026 年,CMP 已成为存储芯片制造的核心平坦化技术,占平坦化工序的 90% 以上。

CMP 的参数控制极为严格:铜互连层的去除速率需控制在 4467Å/min 左右,均匀性偏差≤±2%;表面粗糙度≤0.1nm;铜柱凹陷深度≤31nm------ 若凹陷深度超标,会导致混合键合时的空洞率上升,良率下降。例如,混合键合前的 CMP 处理需将铜柱凹陷深度控制在 31nm 左右,表面粗糙度≤0.1nm,以确保键合强度与信号传输效率。

CMP 的核心挑战是缺陷控制:抛光垫的硬度、转速比、抛光液的酸碱度等参数,都会影响缺陷的产生。例如,若抛光压力过高,会导致晶圆边缘过度研磨(塌边),需通过弹性挡环和压力分区控制技术来补偿,压力分区数量需≥200 个。此外,抛光液的酸碱度需控制在 pH=10 左右,以确保铜的腐蚀速率与研磨速率平衡。

2.2.7 金属化(Metallization)

金属化是在晶圆表面沉积金属互连层,连接晶体管与存储单元的过程,是存储芯片性能的关键 ------ 互连层的电阻直接决定了数据传输的延迟。2026 年,大马士革工艺已成为存储芯片金属化的主流技术,占金属化工序的 90% 以上。

大马士革工艺的核心步骤是:通过刻蚀绝缘层形成沟槽,再沉积铜金属,最后通过 CMP 去除多余的铜,形成互连线路。2026 年存储芯片的互连层已采用钴(Co)作为阻挡层材料,其电阻率比传统的钽(Ta)低约 30%,可有效降低互连延迟。例如,三星的 DRAM 产品采用钼(Mo)作为字线金属,可将接触电阻降低 40%,提升读写速度约 15%。

金属化的核心挑战是互连延迟控制:随着存储芯片密度的提升,互连层的长度与电阻不断增加,成为限制读写速度的主要因素。例如,采用钴阻挡层可将互连延迟降低约 20%,满足 DDR5 内存的高带宽需求。

2.3 晶圆测试与晶粒分拣(CP 测试)

晶圆制造完成后,需进行晶圆级测试(CP 测试),以筛选出合格的晶粒,避免后续封装成本的浪费 ------CP 测试的良率直接决定了封装环节的成本。2026 年,CP 测试已实现全自动化,测试效率较 2020 年提升了 2 倍以上。

CP 测试的核心步骤与参数控制如下:

- 探针卡接触:采用高精度探针卡(定位精度≤±1μm),与晶圆上的每个晶粒的焊盘接触,施加测试信号。探针卡的针脚间距需与晶粒的焊盘间距完全匹配,偏差≤±0.5μm。

- 电性能测试:测试参数包括读写速度、功耗、阈值电压、漏电流等,每个参数都有严格的阈值 ------ 例如,DRAM 的读写速度需≥8000MT/s,漏电流需≤10⁻⁹A。测试时间需控制在每颗晶粒 10-20ms,以确保测试效率。

- 标记与分拣:对不合格的晶粒进行墨点标记,然后通过激光切割将晶圆切割成独立的晶粒,最后通过自动分拣设备将合格晶粒分拣出来,分拣精度≤±50μm。

泰瑞达的测试设备可实现每小时测试 10000 颗晶粒,良率预测准确率≥95%------ 这一准确率直接决定了封装环节的成本。例如,若良率预测准确率提升 5%,封装环节的成本可降低约 10%。

2.4 封装与测试(后道工艺)

封装是将合格晶粒组装成最终芯片的过程,是 HBM 等高端存储芯片的核心竞争力 ------ 其不仅保护芯片,还影响芯片的散热与信号传输性能。2026 年,先进封装已成为存储芯片性能提升的关键方向,占存储芯片制造成本的 30% 以上。

2.4.1 先进封装技术

2026 年存储芯片的主流封装技术包括晶圆级封装(WLP)、2.5D/3D 封装、系统级封装(SiP)等,其中 HBM 采用的是 3D 堆叠封装技术 ------3D 堆叠封装可将多颗 DRAM 裸片垂直堆叠,实现超高带宽。

- 硅通孔(TSV)工艺:TSV 是 HBM 制造的核心环节,占 HBM 总成本的 30%。其步骤包括:采用深反应离子刻蚀(DRIE)技术形成深宽比≥50:1 的通孔;通过 ALD 法在孔壁沉积 SiO₂绝缘层,厚度约 50nm;通过 PVD 法沉积 Ta/TiN 阻挡层和 Cu 种子层;通过电镀法填充 Cu,形成导电通路;最后通过 CMP 法去除多余的 Cu,实现表面平坦化。TSV 的直径需控制在 5-10μm,间距≤20μm,以确保信号传输效率。

- 混合键合技术:混合键合是 2026 年 HBM4 的核心技术突破 ------ 其无需微凸点,直接将上下晶圆的铜电极和介电材料键合,可将互连间距从传统的 40μm 缩小至 10μm 以下,带宽提升约 50%。台积电的 CoWoS(晶圆上芯片)封装产能已售罄至 2026 年底,是 HBM 供应链的核心瓶颈 ------ 每一片 CoWoS 封装的 HBM4 芯片,需要消耗 3-4 片 DRAM 晶圆。

- 热管理技术:HBM 的热管理是关键挑战 ------12 层堆叠的 HBM 功耗可达 50W,若散热不良,结温会超过 140℃,导致性能下降甚至失效。SK 海力士采用的 MR-MUF(Mass Reflow Molded Underfill)技术,将相邻 DRAM 堆叠间的塑封料替换为热硅,提升纵向与横向散热;同时减薄顶部 DRAM 裸片至 50μm,缩短垂直热路径,可将结温从 140℃降至 70.8℃。该技术可将 HBM 的散热能力提升约 30%,满足 AI 服务器的高功耗需求。

2.4.2 最终测试(FT 测试)

封装完成后,需进行最终测试,以确保芯片符合规格要求 ------FT 测试的良率直接决定了最终产品的质量。2026 年,FT 测试已实现全自动化,测试效率较 2020 年提升了 2 倍以上。

FT 测试的核心步骤与参数控制如下:

- 功能测试:测试芯片的读写功能是否正常,包括数据写入、读取、擦除等操作。测试时间需控制在每颗芯片 1-2 分钟,以确保测试效率。

- 性能测试:测试参数包括带宽、延迟、功耗等 ------ 例如,HBM4 的带宽需≥2.8TB/s,延迟需≤10ns。测试环境需模拟实际应用场景,温度控制在 25℃±1℃。

- 可靠性测试:包括高温存储(125℃,1000 小时)、温度循环(-40℃~125℃,1000 次)、湿度测试(85% RH,1000 小时)等,以验证芯片在极端环境下的稳定性。测试后需对芯片进行电性能复测,确保参数无漂移。

爱德万的测试设备可实现每小时测试 1000 颗芯片,良率预测准确率≥99%------ 这一准确率直接决定了最终产品的质量。例如,若良率预测准确率提升 1%,最终产品的返修率可降低约 5%。

第三部分:核心工艺参数控制与良率优化

存储芯片制造的核心是工艺参数的精确控制 ------ 任何微小的偏差都会导致良率骤降甚至全流程报废。2026 年,存储芯片制造的参数控制精度已进入埃米级(1Å=0.1nm),较 2020 年提升了 10 倍以上。

3.1 光刻工艺参数控制

光刻工艺的核心参数包括分辨率、套刻精度、曝光剂量、焦距控制,其精度直接决定了存储单元的最小尺寸 ------ 光刻参数的任何偏差都会导致存储单元失效。

-

分辨率 :采用瑞利判据公式计算: CD=k 1×λ /NA ,其中

k1

为工艺因子(≤0.35),λ

为曝光波长(13.5nm,EUV),\(NA\)为数值孔径(0.55)。2026 年 EUV 光刻的分辨率≤8nm,可满足 10nm 级存储芯片的需求。分辨率偏差若超过 1nm,会导致存储单元的字线与位线短路,良率下降≥20%。 -

套刻精度:控制在≤1.5nm@3σ------ 若套刻精度超标,会导致存储单元的字线与位线错位,漏电流上升,良率下降。例如,套刻精度偏差若超过 2nm,会导致存储单元的漏电流上升≥20%,良率下降≥10%。

-

曝光剂量:控制在 10-50mj/cm²------ 若剂量偏差≥5%,会导致光刻胶图案的线宽偏差≥3%,影响存储单元的尺寸精度。例如,曝光剂量偏差若超过 10%,会导致光刻胶图案的线宽偏差≥5%,良率下降≥15%。

-

焦距控制:控制在≤±1nm------ 若焦距偏差超标,会导致光刻胶图案的清晰度下降,边缘粗糙度上升。例如,焦距偏差若超过 2nm,会导致光刻胶图案的边缘粗糙度上升≥1nm,良率下降≥10%。

光刻工艺的核心失效机制是套刻误差与曝光剂量偏差:套刻误差会导致存储单元的字线与位线错位,漏电流上升;曝光剂量偏差会导致光刻胶图案的线宽偏差,影响存储单元的尺寸精度。例如,套刻误差偏差若超过 2nm,会导致存储单元的漏电流上升≥20%,良率下降≥10%。

3.2 刻蚀工艺参数控制

刻蚀工艺的核心参数包括等离子体密度、偏置电压、刻蚀气体流量、刻蚀深度均匀性,其精度直接决定了存储单元的深宽比与侧壁粗糙度 ------ 刻蚀参数的任何偏差都会导致存储单元的漏电流上升。

- 等离子体密度:控制在 10¹¹-10¹²cm⁻³------ 若密度偏差≥10%,会导致刻蚀速率偏差≥5%,影响深宽比的精度。例如,等离子体密度偏差若超过 20%,会导致刻蚀速率偏差≥10%,深宽比偏差≥5%,良率下降≥10%。

- 偏置电压:控制在 100-500V------ 若电压偏差≥10%,会导致离子能量偏差≥10%,影响刻蚀的各向异性。例如,偏置电压偏差若超过 20%,会导致离子能量偏差≥20%,刻蚀的各向异性下降≥10%,良率下降≥10%。

- 刻蚀气体流量:控制在 10-100sccm------ 若流量偏差≥5%,会导致刻蚀选择比偏差≥5%,影响侧壁的平整度。例如,刻蚀气体流量偏差若超过 10%,会导致刻蚀选择比偏差≥10%,侧壁粗糙度上升≥0.5nm,良率下降≥10%。

- 刻蚀深度均匀性:控制在≤±2%------ 若均匀性偏差超标,会导致存储单元的沟道长度偏差≥5%,影响阈值电压的精度。例如,刻蚀深度均匀性偏差若超过 5%,会导致存储单元的沟道长度偏差≥5%,阈值电压漂移≥10%,良率下降≥15%。

刻蚀工艺的核心失效机制是微负载效应与侧壁粗糙度超标:微负载效应会导致不同图形密度区域的刻蚀速率差异,影响深宽比的精度;侧壁粗糙度超标会导致存储单元的漏电流上升,数据保持时间缩短。例如,微负载效应若导致深宽比偏差≥10%,会导致存储单元的漏电流上升≥20%,良率下降≥15%。

3.3 掺杂工艺参数控制

掺杂工艺的核心参数包括杂质浓度、结深、注入角度,其精度直接决定了存储单元的阈值电压 ------ 掺杂参数的任何偏差都会导致存储单元的读写速度下降。

- 杂质浓度:控制在 10¹⁶-10¹⁹atoms/cm³------ 若浓度偏差≥5%,会导致阈值电压偏差≥5%,影响 DRAM 的读写速度。例如,杂质浓度偏差若超过 10%,会导致阈值电压偏差≥10%,DRAM 的读写速度下降≥15%,良率下降≥10%。

- 结深:控制在 10-50nm------ 若结深偏差≥5%,会导致晶体管的漏电流偏差≥10%,影响存储单元的可靠性。例如,结深偏差若超过 10%,会导致晶体管的漏电流偏差≥20%,存储单元的可靠性下降≥15%,良率下降≥10%。

- 注入角度:控制在 7°±0.5°------ 若角度偏差≥1°,会导致沟道效应增强,离子注入深度偏差≥5%,阈值电压漂移≥10%。例如,注入角度偏差若超过 1°,会导致离子注入深度偏差≥5%,阈值电压漂移≥10%,良率下降≥10%。

掺杂工艺的核心失效机制是沟道效应与杂质浓度偏差:沟道效应会导致离子注入深度偏差,阈值电压漂移;杂质浓度偏差会导致阈值电压偏差,影响 DRAM 的读写速度。例如,注入角度偏差若超过 1°,会导致离子注入深度偏差≥5%,阈值电压漂移≥10%,良率下降≥10%。

3.4 热处理工艺参数控制

热处理工艺的核心参数包括退火温度、时间、升温速率,其精度直接决定了掺杂离子的激活效率与晶格损伤的修复程度 ------ 热处理参数的任何偏差都会导致存储单元的性能下降。

- 退火温度:控制在 1000-1350℃------ 若温度偏差≥10℃,会导致掺杂离子激活率偏差≥10%,影响晶体管的电流驱动能力。例如,退火温度偏差若超过 20℃,会导致掺杂离子激活率偏差≥20%,晶体管的电流驱动能力下降≥15%,良率下降≥10%。

- 时间:控制在 1-10 秒 ------ 若时间偏差≥1 秒,会导致掺杂离子扩散偏差≥5%,影响阈值电压的精度。例如,退火时间偏差若超过 2 秒,会导致掺杂离子扩散偏差≥10%,阈值电压漂移≥10%,良率下降≥10%。

- 升温速率:控制在 100-500℃/s------ 若升温速率偏差≥50℃/s,会导致晶圆表面的温度梯度偏差≥5℃,影响薄膜应力的均匀性。例如,升温速率偏差若超过 100℃/s,会导致晶圆表面的温度梯度偏差≥10℃,薄膜应力的均匀性下降≥10%,良率下降≥10%。

热处理工艺的核心失效机制是热预算过大与温度梯度偏差:热预算过大会导致掺杂离子扩散,结深偏差;温度梯度偏差会导致薄膜应力的均匀性下降,存储单元的性能下降。例如,热预算若超过设计值的 20%,会导致掺杂离子扩散偏差≥10%,结深偏差≥5%,良率下降≥15%。

3.5 CMP 工艺参数控制

CMP 工艺的核心参数包括抛光压力、转速比、浆料流量、去除速率均匀性,其精度直接决定了晶圆表面的平整度与铜柱凹陷深度 ------CMP 参数的任何偏差都会导致混合键合的良率下降。

- 抛光压力:控制在 1-5psi------ 若压力偏差≥0.1psi,会导致晶圆边缘过度研磨(塌边),平整度偏差≥5nm。例如,抛光压力偏差若超过 0.2psi,会导致晶圆边缘过度研磨(塌边),平整度偏差≥10nm,混合键合的良率下降≥15%。

- 转速比:控制在 0.5-1.5------ 若转速比偏差≥0.1,会导致去除速率均匀性偏差≥2%,影响表面平整度。例如,转速比偏差若超过 0.2,会导致去除速率均匀性偏差≥5%,表面平整度偏差≥5nm,混合键合的良率下降≥10%。

- 浆料流量:控制在 100-500ml/min------ 若流量偏差≥50ml/min,会导致去除速率偏差≥5%,影响表面粗糙度。例如,浆料流量偏差若超过 100ml/min,会导致去除速率偏差≥10%,表面粗糙度上升≥0.5nm,混合键合的良率下降≥10%。

- 去除速率均匀性:控制在≤±2%------ 若均匀性偏差超标,会导致铜柱凹陷深度偏差≥5nm,影响混合键合的良率。例如,去除速率均匀性偏差若超过 5%,会导致铜柱凹陷深度偏差≥10nm,混合键合的良率下降≥15%。

CMP 工艺的核心失效机制是边缘效应与铜柱凹陷深度偏差:边缘效应会导致晶圆边缘过度研磨(塌边),平整度偏差;铜柱凹陷深度偏差会导致混合键合时的空洞率上升,良率下降。例如,铜柱凹陷深度偏差若超过 31nm,会导致混合键合时的空洞率上升≥10%,良率下降≥15%。

第四部分:存储芯片性能优化逻辑与技术路径

存储芯片的性能优化围绕 "密度、速度、功耗、可靠性、成本" 五大核心目标展开,2026 年的优化重点是适配 AI 场景的高带宽、低延迟需求 ------AI 服务器对存储带宽的需求是传统服务器的 10 倍以上,对延迟的要求是传统服务器的 1/10 以下。

4.1 存储密度提升:3D 堆叠与单元微缩

存储密度是存储芯片的核心竞争力 ------ 其直接决定了单位容量成本,是厂商抢占市场份额的关键。2026 年,存储密度提升的核心技术路径是 3D 堆叠与单元微缩,较 2020 年提升了 2 倍以上。

-

3D NAND 堆叠层数提升 :2026 年长江存储实现 294 层 Xtacking

®3.0 量产,铠侠推出 332 层 BiCS 10,三星计划 2026 年底量产 300 层以上 V-NAND。堆叠层数的提升直接降低单位容量成本:每增加 100 层,单位 GB 成本可下降约 30%(研精毕智,2026)。例如,332 层 BiCS 10 的单位 GB 成本较 200 层 NAND 下降约 40%,具备显著的成本优势。

-

DRAM 单元微缩:从 6F² 平面结构向 4F² 垂直沟道(VCT)结构演进,单元面积缩小约 30%,存储密度提升约 40%(三星官网,2026)。此外,三星计划在 2027 年量产 3D DRAM,通过垂直堆叠存储单元,进一步提升存储密度。例如,4F² VCT 结构的 DRAM 存储密度较 6F² 平面结构提升约 40%,可满足 AI 服务器的高容量需求。

-

HBM 堆叠层数提升:从 HBM3E 的 12 层堆叠向 HBM4 的 16 层堆叠演进,容量从 24GB 提升至 48GB,带宽从 1.2TB/s 提升至 2.8TB/s(美光官网,2026)。例如,16 层堆叠的 HBM4 容量达 48GB,带宽达 2.8TB/s,可满足 AI 服务器的高带宽需求。

存储密度提升的核心逻辑是 "垂直堆叠替代平面微缩"------ 通过在垂直方向上堆叠存储单元,突破平面微缩的物理极限。例如,3D NAND 的堆叠层数从 2020 年的 128 层提升至 2026 年的 300 层以上,存储密度提升了 2 倍以上,单位 GB 成本下降了约 50%。

4.2 读写速度优化:接口与架构创新

读写速度是 AI 场景的核心需求 ------AI 服务器需要每秒数十 TB 的数据传输带宽,才能支撑大模型的训练与推理。2026 年,读写速度优化的核心技术路径是接口迭代与存内计算,较 2020 年提升了 3 倍以上。

- 接口技术迭代:从 PCIe 5.0 向 PCIe 6.0 迭代,采用 PAM4 信号调制技术,传输速率从 32GT/s 提升至 64GT/s,带宽提升 100%;从 NVMe 2.0 向 NVMe 2.0c 迭代,支持多流 I/O 与 ZNS(Zoned Namespaces)技术,随机 IOPS 提升约 50%。美光的 9650 系列 PCIe 6.0 SSD 顺序读取速度达 28GB/s,随机读取 IOPS 达 5.5M,较 PCIe 5.0 SSD 提升了 1 倍以上,可满足 AI 服务器的高带宽需求。

- HBM 带宽提升:从 HBM3E 的 1.2TB/s 向 HBM4 的 2.8TB/s 提升,采用 2048-bit 接口、低电压 TSV 技术,功耗降低约 20%。例如,HBM4 的带宽达 2.8TB/s,是 HBM3E 的 2.3 倍,可满足 AI 服务器的高带宽需求。

- 存内计算架构:将计算单元嵌入存储阵列,避免数据在存储与计算单元之间的频繁传输,延迟降低约 50%,能效提升约 100 倍。合肥睿科的 ReRAM 存算一体芯片 AI 推理能效达 142 TOPS/W,较传统 GPU 提升了约 100 倍,可满足 AI 服务器的高能效需求。

读写速度优化的核心逻辑是 "减少数据传输距离"------ 通过接口迭代提升数据传输速率,通过存内计算将计算单元嵌入存储阵列,避免数据在存储与计算单元之间的频繁传输。例如,存内计算可将数据传输距离从厘米级缩短至纳米级,延迟降低约 50%,能效提升约 100 倍。

4.3 功耗降低:电路与材料优化

功耗是移动设备与数据中心的核心需求 ------ 数据中心的存储功耗占总功耗的 30% 以上,降低存储功耗可大幅降低运营成本。2026 年,功耗降低的核心技术路径是低功耗 DRAM 技术、NAND 功耗优化与存算一体,较 2020 年降低了约 50%。

- 低功耗 DRAM 技术:从 LPDDR5X 向 LPDDR6 迭代,工作电压从 1.05V 降至 0.9V,功耗降低约 20%,速度提升约 33%。SK 海力士的 LPDDR6 DRAM 速度达 14.4Gbps,功耗降低约 20%,可满足 AI PC 的低功耗需求。

- NAND 功耗优化:从传统架构向新型架构迭代,存储单元串工作电压从 18V 降至 0.7V,读写功耗降低约 96%。SK 海力士的新型 NAND 存储单元串工作电压从 18V 降至 0.7V,读写功耗降低约 96%,可满足数据中心的低功耗需求。

- 存算一体能效提升:ReRAM 存算一体芯片的 AI 推理能效达 142 TOPS/W,较传统 GPU 提升约 100 倍。合肥睿科的 ReRAM 存算一体芯片 AI 推理能效达 142 TOPS/W,较传统 GPU 提升了约 100 倍,可满足 AI 服务器的高能效需求。

功耗降低的核心逻辑是 "优化电路与材料特性"------ 通过降低工作电压、优化电路设计、采用新型材料,降低存储芯片的功耗。例如,LPDDR6 的工作电压从 1.05V 降至 0.9V,功耗降低约 20%;存算一体可将数据传输功耗从 80% 降至 20% 以下,能效提升约 100 倍。

4.4 可靠性提升:ECC 与磨损均衡

可靠性是企业级存储的核心需求 ------ 数据中心的存储系统需要全年无休运行,任何数据丢失都会导致巨大损失。2026 年,可靠性提升的核心技术路径是 ECC 纠错技术迭代、磨损均衡技术优化与热管理技术优化,较 2020 年提升了约 2 倍以上。

- ECC 纠错技术迭代:从传统的 SECDED(单纠错双检测)向 RAIDDR ECC 迭代,纠错能力提升约 40 倍,延迟压缩至 2 纳秒。英伟达 H200 GPU 搭载的 ECC 加速引擎采用并行校验架构,在 48GB HBM3E 显存中实现每周期 16 字节的纠错能力,较传统方案吞吐量提升 40 倍,可满足 AI 服务器的高可靠性需求。

- 磨损均衡技术优化:从动态磨损均衡向静态磨损均衡演进,静态磨损均衡的延寿效果是动态的 3 倍以上。瑞芯微的专利技术通过分析 NAND 闪存的读延迟和 ECC 使用量,计算块的健康指数,优先选择健康块进行写入,可将 NAND 的使用寿命延长约 2 倍,满足企业级存储的高可靠性需求。

- 热管理技术优化:从传统的风冷向液冷演进,采用直冷式液冷技术,可将 HBM 的结温从 140℃降至 70.8℃,可靠性提升约 20%。SK 海力士的 MR-MUF 技术可将 HBM 的结温从 140℃降至 70.8℃,可靠性提升约 20%,满足 AI 服务器的高可靠性需求。

可靠性提升的核心逻辑是 "主动防护与冗余设计"------ 通过 ECC 纠错技术检测与纠正数据错误,通过磨损均衡技术平均分配写入次数,通过热管理技术降低芯片温度,提升可靠性。例如,RAIDDR ECC 的纠错能力较传统 SECDED 提升约 40 倍,可检测与纠正更多的数据错误;静态磨损均衡的延寿效果是动态的 3 倍以上,可延长 NAND 的使用寿命约 2 倍。

4.5 成本控制:架构与封装优化

成本是消费级存储的核心需求 ------ 消费者对存储容量的需求不断提升,但对价格的敏感度也很高。2026 年,成本控制的核心技术路径是 3D NAND 架构优化、HBM 封装优化与国产设备替代,较 2020 年降低了约 30%。

- 3D NAND 架构优化:从 CTF(电荷陷阱闪存)向 CBA(CMOS 直接键合)架构演进,将控制逻辑电路与存储阵列分别制造,再进行高精度键合,可将存储密度提升约 50%,成本降低约 30%。铠侠的 BiCS 10 采用 CBA 架构,存储密度提升约 50%,成本降低约 30%,具备显著的成本优势。

- HBM 封装优化:从传统的微凸点键合向混合键合演进,可将互连间距从 40μm 缩小至 10μm 以下,带宽提升约 50%,成本降低约 20%。台积电的 CoWoS 封装采用混合键合技术,成本降低约 20%,可满足 HBM 的低成本需求。

- 国产设备替代:刻蚀机、薄膜沉积设备的国产化率已达 50% 以上,可将存储芯片的制造成本降低约 15%。中微半导体的 NMC612H 刻蚀机已占据国内 30% 的市场份额,价格较进口设备低约 30%,可将存储芯片的制造成本降低约 15%。

成本控制的核心逻辑是 "提升生产效率与降低设备成本"------ 通过架构优化提升存储密度,通过封装优化提升良率,通过国产设备替代降低设备成本。例如,CBA 架构可将存储密度提升约 50%,单位容量成本降低约 30%;国产刻蚀机的价格较进口设备低约 30%,可将存储芯片的制造成本降低约 15%。

第五部分:存储芯片 20 年价格周期性特点与驱动逻辑

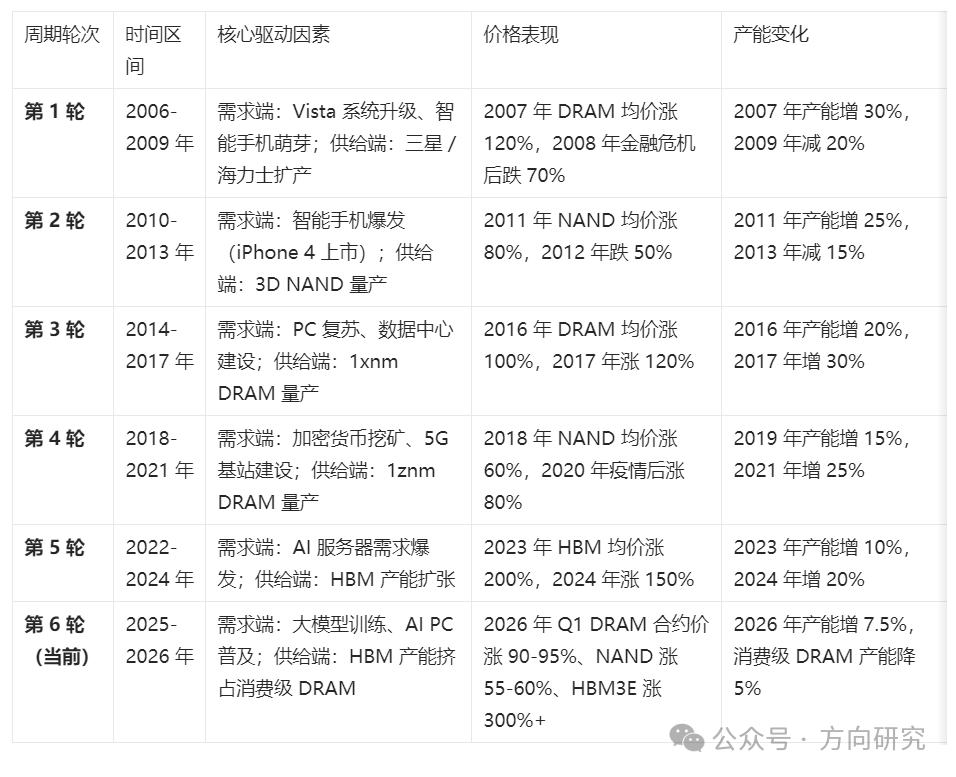

存储芯片行业具有极强的周期性,2006-2026 年的 20 年间,共经历了 6 轮完整的 "涨价 - 扩产 - 过剩 - 降价 - 出清" 周期,核心驱动因素是供需错配 ------ 这一特性是由存储芯片的 "重资产、长周期、寡头垄断" 特性决定的。

5.1 2006-2026 年价格周期复盘

2006-2026 年,存储芯片行业共经历了 6 轮完整的价格周期,每轮周期的时长、驱动因素与价格表现存在明显差异:

上述周期的核心逻辑是 "供需错配":需求爆发时,产能无法快速响应,价格暴涨;需求疲软时,产能无法快速收缩,价格暴跌。例如,2008 年金融危机导致需求骤降,而 2007 年扩产的产能集中释放,DRAM 均价跌 70%;2026 年 AI 服务器需求爆发,而 HBM 产能挤占消费级 DRAM 产能,导致消费级存储供给缺口超 20%,价格暴涨。

5.2 周期共性规律

20 年周期的核心共性规律可总结为三点,这些规律是由存储芯片的 "重资产、长周期、寡头垄断" 特性决定的:

- 时长稳定:完整周期时长约 3-4 年,上行期约 12-18 个月,下行期约 18-24 个月 ------ 这与存储芯片的产能建设周期(2-3 年)高度匹配。例如,2016-2019 年的周期时长为 3 年,上行期 18 个月,下行期 18 个月。

- 涨幅陡峭:上行期价格涨幅通常超 50%,甚至达 100% 以上;下行期跌幅通常超 40%------ 这是由存储芯片的 "重资产、长周期、寡头垄断" 特性决定的:需求爆发时,产能无法快速响应,价格暴涨;需求疲软时,产能无法快速收缩,价格暴跌。例如,2026 年 Q1 DRAM 合约价涨 90-95%,创历史新高。

- 传导有序:价格传导路径通常为 "企业级(服务器)→消费级(PC / 手机)→嵌入式(汽车 / 工业)"------ 企业级需求对价格更敏感,且头部厂商会优先保障企业级订单,因此企业级存储的价格涨幅通常领先消费级 3-6 个月。例如,2025 年 Q3 服务器 DRAM 价格先涨,2025 年 Q4 消费级 DRAM 价格才开始上涨。

5.3 2026 年超级周期的特殊性

2026 年的价格周期与前 5 轮存在本质差异,核心是 "AI 需求的结构性爆发" 而非传统的 "消费电子脉冲式增长"------ 这一差异导致周期的驱动逻辑、价格表现与产能结构均发生了根本性变化。

- 需求端:AI 服务器单台 DRAM 需求达传统服务器的 8-10 倍,NAND 需求达 5-6 倍(TrendForce,2026)。据 Counterpoint 数据,2026 年 AI 服务器的出货量占服务器总出货量的比例已达 30%,较 2025 年提升了 20 个百分点,成为存储需求增长的核心引擎。这一需求是结构性的,而非脉冲式的 ------AI 大模型的训练与推理需要持续的高带宽存储支持,而非短期的消费电子升级。

- 供给端:头部厂商将 80% 以上的先进产能优先分配给 HBM 和高端 DDR5,消费级存储产能被系统性挤压 ------ 例如,SK 海力士 2026 年的 HBM 产能占比从 2025 年的 20% 提升至 50%,消费级 DRAM 产能占比从 60% 降至 30%(SK 海力士官网,2026)。这导致消费级存储的供给缺口超 20%,价格涨幅创历史新高。

- 价格表现:2026 年 Q1 DRAM 合约价涨 90-95%,NAND 涨 55-60%,HBM3E 涨 300%+------ 这一涨幅远超历史平均水平(约 50%)。据 Kingston 公开报告,NAND wafer 价格较 2025 年 Q1 暴涨 246%,消费级 1TB SSD 零售价从 45 美元涨至 90 美元,翻了一倍。这一价格涨幅是由结构性供需错配驱动的,而非传统的周期波动。

5.4 2026 年周期拐点判断

关于 2026 年周期的拐点,机构存在明显分歧,核心是对 HBM 产能释放节奏与 AI 需求持续性的判断差异:

- 乐观判断(伯恩斯坦、美银) :2026 年底涨幅斜率放缓,2027 年供需缺口收窄。核心依据:头部厂商的 HBM 产能将在 2026 年底释放约 10%,消费级 DRAM 产能将在 2027 年回升约 5%;AI 需求的增长速度将从 2026 年的 80% 降至 2027 年的 50%,供需缺口将从 20% 收窄至 10% 以下。

- 悲观判断(36 氪、中金) :2028 年才会出现实质性缓解。核心依据:HBM 的产能建设周期长达 2-3 年,2026 年底释放的产能仅占总需求的 10%;AI 需求的增长速度将保持在 60% 以上,供需缺口将持续扩大至 2028 年。

- 分歧核心:HBM 产能释放节奏与 AI 需求持续性的判断差异 ------ 乐观机构认为 HBM 产能将快速释放,AI 需求将逐步放缓;悲观机构认为 HBM 产能释放滞后,AI 需求将持续高增长。

第六部分:存储芯片产业链技术迭代与竞争格局

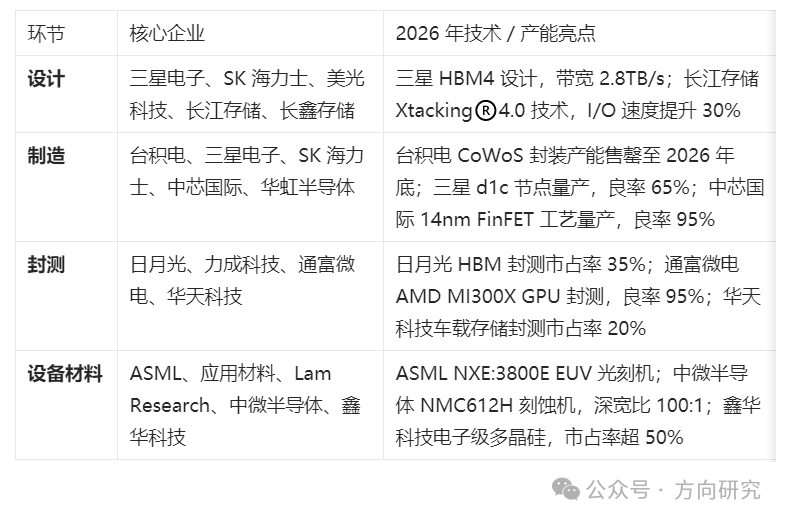

存储芯片产业链涵盖设计、制造、封测、设备材料四大核心环节,2026 年的竞争焦点集中在 HBM 与 3D NAND 领域 ------ 这两个领域是 AI 时代存储芯片的核心竞争力所在。

6.1 产业链核心环节与头部厂商

存储芯片产业链的核心环节包括设计、制造、封测、设备材料,每个环节都有明确的分工与头部厂商,形成了高度集中的竞争格局:

上述企业占据了存储芯片产业链的核心环节,形成了高度集中的竞争格局 ------ 例如,DRAM 市场被三星、SK 海力士、美光三家垄断,合计份额超 95%;NAND 市场被三星、SK 海力士、铠侠、西部数据、美光五家垄断,合计份额超 90%。

6.2 技术迭代趋势

2026 年存储芯片的技术迭代趋势可总结为三点,这些趋势是由 AI 需求驱动的,旨在突破物理极限与提升性能:

- 存储介质从平面到 3D:3D NAND 堆叠层数突破 300 层,DRAM 从平面结构向垂直结构演进 ------ 这是提升存储密度的唯一途径,也是厂商技术实力的核心指标。例如,长江存储的 294 层 3D NAND、三星的 4F² VCT DRAM,都是这一趋势的代表。

- 制造工艺从 28nm 到 7nm:DRAM 工艺节点从 14nm 向 10nm 级演进,NAND 工艺节点从 19nm 向 12nm 级演进 ------ 工艺节点的微缩,可进一步提升存储密度,降低单位成本。例如,三星的 d1c 节点(11nm)DRAM,存储密度较 14nm 提升约 40%。

- 封装技术从 2D 到 3D:HBM 堆叠层数突破 16 层,混合键合技术成为主流 ------3D 封装技术可实现超高带宽,是 AI 时代存储芯片的核心技术方向。例如,HBM4 的 16 层堆叠、台积电的 CoWoS 封装,都是这一趋势的代表。

6.3 竞争格局演变

2026 年存储芯片的竞争格局呈现 "寡头垄断 + 国产突破" 的特征 ------ 寡头厂商占据高端市场,国产厂商在中低端市场实现突破,但在高端领域仍存在技术代差。

-

DRAM 市场:三星、SK 海力士、美光合计占比 95%,国产长鑫存储占比约 3%。长鑫存储 17nm DDR5 产品已实现大规模出货,性能指标与三星、SK 海力士的同规格产品差距缩小至 5% 以内,完全满足消费级、工业级市场需求。此外,长鑫存储的 12nm DDR5 产品已进入研发阶段,计划 2027 年量产。但在 HBM 领域,国产厂商仍存在 1-2 代的技术代差 ------ 长鑫存储的 HBM3 产品良率约 75%,而 SK 海力士的 HBM4 产品良率已达 50-60%。

-

NAND 市场 :三星、SK 海力士、铠侠、西部数据、美光合计占比 90%,国产长江存储占比约 5.2%。长江存储 294 层 3D NAND 已实现量产,Xtacking

®4.0 技术将 I/O 速度提升 30%,功耗降低 20%(长江存储官网,2026)。此外,长江存储计划 2027 年量产 350 层以上 3D NAND。在产能方面,长江存储武汉三期项目将于 2026 年下半年量产,总年产能突破 200 万片,超越 SK 海力士跃居全球 NAND 闪存市场第三。

-

HBM 市场:SK 海力士、三星、美光合计占比 99%,国产厂商尚未实现量产。SK 海力士 HBM 市占率超 50%,是英伟达 H100 GPU 的核心供应商 ------ 其 HBM4 产品已实现量产,带宽达 2.8TB/s(SK 海力士官网,2026)。国产厂商在 HBM 领域的技术代差约 1-2 年,主要瓶颈是 TSV 刻蚀与堆叠良率控制。

第七部分:存储芯片供应链全球化现状与地缘政治风险

存储芯片供应链是全球分工最深入的产业之一,同时也是地缘政治风险最集中的领域之一 ------ 任何一个环节的中断,都会导致全球存储芯片供应的短缺。2026 年,地缘政治风险与供应链脆弱性进一步加剧,成为存储芯片行业的核心挑战。

7.1 全球化供应链的形成逻辑

存储芯片供应链的全球化分工,是由 "比较优势" 驱动的 ------ 不同国家和地区在设备材料、制造、封测等环节具备不同的优势,形成了高度协作的全球供应链:

- 美国:提供设备与材料(如应用材料的薄膜沉积设备、Lam Research 的刻蚀设备)、设计工具(如 Synopsys 的 EDA 工具),占据价值链顶端,附加值占比超 40%。美国的设备材料厂商占据了全球存储芯片设备市场的 70% 以上,是存储芯片制造的核心支撑。

- 日本:提供关键材料(如信越化学的硅片、JSR 的光刻胶)、测试设备(如爱德万的测试设备),附加值占比超 20%。日本的硅片厂商占据了全球存储芯片硅片市场的 50% 以上,是存储芯片制造的基础。

- 韩国:提供制造与封测(如三星、SK 海力士的 DRAM/NAND 制造),附加值占比超 20%。韩国的存储芯片制造产能占全球的 70% 以上,是存储芯片供应的核心。

- 中国台湾:提供先进封装(如台积电的 CoWoS 封装),附加值占比超 10%。中国台湾的先进封装产能占全球的 50% 以上,是 HBM 供应的核心。

- 中国大陆:提供部分制造与封测(如长江存储、长鑫存储的制造,通富微电的封测)、基础材料(如鑫华科技的电子级多晶硅),附加值占比超 10%。中国大陆的存储芯片制造产能占全球的 10% 以上,是全球存储芯片供应链的重要组成部分。

7.2 地缘政治风险与产能区域化调整

2026 年存储芯片供应链面临的核心地缘政治风险是 "技术脱钩"------ 美国对中国的半导体出口管制,限制了中国企业获取先进设备与技术的能力;同时,红海危机等地缘事件导致全球供应链脆弱性凸显。

- 出口管制:2026 年 4 月,美国推出 MATCH 法案,将管制范围扩大至成熟制程设备 ------ 不仅全面禁售 EUV 光刻机及 14nm 以下先进制程设备,还新增对所有浸没式 DUV 光刻机、低温蚀刻、薄膜沉积等成熟制程设备的禁售令。该法案强制荷兰、日本、韩国在 150 天内完全对齐美国芯片设备管制标准,若不配合,美国将实施单边长臂制裁,禁止使用美国技术或零部件的盟国企业对华出口。这导致中国存储产能扩张受阻 ------ 长江存储、长鑫存储的扩产计划被迫推迟,高端存储芯片的量产进度滞后约 2-3 年。

- 产能转移:头部厂商加速将产能从中国大陆转移至东南亚(如越南、泰国)------ 例如,三星计划 2026 年将中国西安的 NAND 产能转移至越南太原,SK 海力士计划 2027 年将中国无锡的 DRAM 产能转移至韩国平泽。这导致中国存储芯片的产能占比从 2025 年的 15% 降至 2026 年的 10%。

- 供应链中断风险:2026 年红海危机导致欧洲与亚洲之间的航运时间延长了约 30 天,存储芯片的运输成本上涨了约 20%(环球时报,2026)。此外,霍尔木兹海峡的紧张局势,也可能导致石油价格上涨,进一步推高存储芯片的制造成本。这凸显了全球存储芯片供应链的脆弱性 ------ 任何一个关键节点的中断,都会导致全球存储芯片供应的短缺。

7.3 中国存储芯片供应链的现状与突破

2026 年中国存储芯片供应链的现状是 "局部突破,整体落后"------ 在部分环节实现了国产化,但在高端领域仍存在技术代差,依赖进口。

- 突破领域:

-

- 硅材料:鑫华科技电子级多晶硅市占率超 50%,纯度达 12N------ 其产品已通过长江存储、长鑫存储的认证,打破了海外厂商的垄断。

- 刻蚀设备:中微半导体 NMC612H 刻蚀机深宽比达 100:1,市占率超 30%------ 其设备已应用于长江存储的 3D NAND 产线,打破了海外厂商的垄断。

- 光刻胶:彤程新材 KrF 光刻胶市占率超 40%,已实现量产 ------ 其产品已应用于长鑫存储的 DRAM 产线,打破了海外厂商的垄断。

- 落后领域:

-

- EUV 光刻机:完全依赖 ASML,国内尚未实现量产 ------ASML 的 NXE:3800E EUV 光刻机,单台价格超 1.5 亿美元,且需提前 2-3 年预定。

- 高端光刻胶:ArF 浸没式光刻胶的国产化率不足 10%,主要依赖日本 JSR、东京应化 ------ 其分辨率可达 22nm,是 10nm 级存储芯片的核心材料。

- 测试设备:HBM 测试设备的国产化率不足 5%,主要依赖泰瑞达、爱德万 ------ 其测试精度可达亚微米级,是 HBM 量产的核心设备。

7.4 供应链未来趋势

2026-2030 年存储芯片供应链的未来趋势可总结为三点,这些趋势是由地缘政治风险与技术创新驱动的,旨在提升供应链的稳定性与自主性:

- 区域化:形成 "北美 - 欧洲 - 亚洲" 三大区域供应链,每个区域都有完整的设计、制造、封测、设备材料体系 ------ 这是为了降低地缘政治风险,保障供应链的稳定性。例如,美国正在推动 "芯片法案",鼓励企业在北美建立存储芯片制造产能;欧盟正在推动 "欧洲芯片法案",鼓励企业在欧洲建立存储芯片制造产能。

- 多元化:设备材料供应商从单一国家向多元化发展,例如,中国的刻蚀设备、光刻胶厂商正在逐步进入全球供应链 ------ 这将降低头部厂商对单一供应商的依赖。例如,中微半导体的刻蚀机已进入三星、SK 海力士的产线;彤程新材的光刻胶已进入美光的产线。

- 自主可控:中国将加大对存储芯片供应链的投入,目标是在 2030 年实现 70% 的国产化率 ------ 这需要在 EUV 光刻机、高端光刻胶、测试设备等领域实现突破。例如,中国正在推动 "国产替代" 战略,加大对半导体设备材料的研发投入,目标是在 2030 年实现 70% 的国产化率。

第八部分:总结与展望

8.1 核心结论

本报告基于 2026 年 4 月最新产业数据与技术文献,得出以下核心结论:

-

技术范式转移:3D NAND 堆叠层数突破 300 层,DRAM 进入 4F² 垂直沟道时代,新兴存储(MRAM/ReRAM/PCRAM)在存算一体场景实现量产突破 ------ 存储芯片的技术演进已从 "平面微缩" 转向 "垂直堆叠 + 架构创新",突破了摩尔定律的物理极限。

-

制造精度极限:存储芯片制造已进入埃米级控制阶段,套刻精度≤1.5nm@3σ,刻蚀深宽比≥100:1,任何参数偏差都会导致良率骤降 ------ 这对设备精度与工艺控制提出了前所未有的要求,是人类工业制造的巅峰之一。

-

AI 驱动超级周期:2026 年存储芯片价格创历史新高,AI 需求是核心驱动因素 ------AI 服务器单台存储需求是传统服务器的 8-10 倍,HBM 产能挤占效应导致消费级存储供给缺口超 20%。这一周期是结构性的,而非传统的脉冲式周期。

-

产业格局重构 :SK 海力士 HBM 市占率超 50%,长江存储 Xtacking

®4.0 技术实现突破,台积电 CoWoS 封装产能成为核心瓶颈 ------ 存储芯片的竞争格局已从 "规模竞争" 转向 "技术竞争",技术实力成为厂商的核心竞争力。

-

供应链风险加剧:地缘政治风险导致产能区域化调整,中国存储供应链在高端领域仍面临挑战 ------EUV 光刻机、高端光刻胶、测试设备等核心领域的国产化率不足 10%。同时,红海危机等地缘事件导致全球供应链脆弱性凸显,存储芯片的运输成本上涨了约 20%。

核心视角:存储芯片已从 "通用计算配角" 演变为 "AI 算力核心引擎",2026 年正处于技术范式转移与产业格局重构的关键节点 ------3D 堆叠突破物理微缩极限、HBM(高带宽内存)成为 AI 服务器刚性需求、地缘政治重塑全球供应链规则。

关键结论

-

技术极限突破:3D NAND 堆叠层数进入 300 层时代(长江存储 294 层量产、铠侠 332 层 BiCS 10 试产),电荷陷阱闪存(CTF)全面取代浮栅(FG)架构;DRAM 从平面 6F² 结构升级为 4F² 垂直沟道晶体管(VCT),存储密度较传统结构提升 40%。

-

制造精度巅峰:存储芯片制造已进入埃米级控制阶段 ------3D NAND 沟道刻蚀深宽比达 100:1、套刻精度≤1.5nm@3σ、薄膜厚度均匀性≤±0.5%,任何参数偏差≥5% 都会导致良率骤降。

-

AI 驱动超级周期:2026 年存储价格创历史新高 ------DRAM 合约价季涨 90%、NAND 涨 55%、HBM3E 涨 300%;AI 服务器单台 DRAM 需求达传统服务器的 8-10 倍,高端产能向 HBM 倾斜导致消费级存储供给缺口超 20%。

-

产业格局重构 :SK 海力士 HBM 市占率超 50%,长江存储 Xtacking

®4.0 技术将 I/O 速度提升 30%;台积电 CoWoS 封装产能已售罄至 2026 年底,成为 HBM 供应链核心瓶颈。

-

供应链风险加剧:2026 年美国 MATCH 法案将管制范围扩大至成熟制程设备,中国存储产能扩张受阻;红海危机导致存储芯片运输成本上涨 20%,全球供应链脆弱性凸显。

8.2 未来展望

2026-2030 年,存储芯片行业将进入 "技术创新与产业重构" 的关键时期 ------ 技术创新将突破物理极限,产业重构将改变全球竞争格局:

- 技术创新:3D NAND 堆叠层数将突破 500 层,DRAM 将进入 3D 时代,HBM 堆叠层数将突破 20 层,存算一体技术将实现大规模应用 ------ 这些技术创新将进一步提升存储密度、读写速度与能效。例如,3D DRAM 的存储密度将较 4F² VCT DRAM 提升约 50%;存算一体技术的 AI 推理能效将较传统 GPU 提升约 1000 倍。

- 市场需求:AI 服务器、AI PC、数据中心将成为存储芯片的主要需求增长点,市场规模将持续增长 ------ 据 TrendForce 预测,2030 年全球存储芯片市场规模将达 1.2 万亿美元,较 2026 年增长约 50%。这一需求将持续驱动存储芯片的技术创新与产能扩张。

- 产业格局:中国存储厂商将在全球市场中占据更重要的地位,国产化率将逐步提升 ------ 据中国半导体行业协会预测,2030 年中国存储芯片的国产化率将达 70%。长江存储、长鑫存储将在 3D NAND、DRAM 领域实现突破,成为全球存储芯片市场的重要参与者。

- 供应链风险:地缘政治风险将持续存在,供应链区域化与多元化将成为主流趋势 ------ 这将导致存储芯片的制造成本上升,但也将为新兴厂商提供机会。例如,中国的存储芯片厂商将在国内市场获得更多的机会,同时也将逐步进入全球市场。

8.3 建议

基于以上分析,提出以下建议供参考,旨在帮助企业与政府应对存储芯片行业的技术变革与地缘政治风险:

- 企业层面:

-

- 加大研发投入:重点投入 3D NAND 堆叠、HBM、存算一体等核心技术,提升技术实力 ------ 例如,长江存储计划 2027 年量产 350 层以上 3D NAND,需加大对堆叠工艺的研发投入;长鑫存储计划 2027 年量产 12nm DDR5,需加大对单元微缩工艺的研发投入。

- 优化产能布局:降低对单一区域的依赖,加速产能区域化调整 ------ 例如,三星计划 2026 年将中国西安的 NAND 产能转移至越南太原,以降低地缘政治风险;SK 海力士计划 2027 年将中国无锡的 DRAM 产能转移至韩国平泽,以降低地缘政治风险。

- 加强供应链合作:与设备材料厂商建立长期合作关系,保障供应链的稳定性 ------ 例如,长江存储与中微半导体建立了长期合作关系,共同开发刻蚀设备;长鑫存储与彤程新材建立了长期合作关系,共同开发光刻胶。

- 政府层面:

-

- 加大政策支持:出台税收减免、研发补贴等政策,支持存储芯片产业的发展 ------ 例如,中国政府出台了 "集成电路产业基金",支持存储芯片的研发与量产;韩国政府出台了 "存储芯片产业支持政策",支持三星、SK 海力士的扩产计划。

- 加强国际合作:推动建立公平、公正的国际贸易秩序,降低地缘政治风险 ------ 例如,中国应加强与欧盟、东南亚国家的合作,共同维护供应链的稳定性;美国应放宽对中国的半导体出口管制,推动全球半导体产业的合作与发展。

- 培养专业人才:加大对半导体专业人才的培养力度,建立完善的人才培养体系 ------ 例如,中国应加强高校的半导体专业建设,培养更多的专业人才;美国应放宽对半导体专业人才的移民限制,吸引更多的全球人才。