1.1 什么是时序约束

在很多 FPGA 初学者甚至是一些初级的 FPGA 工程师眼里,FPGA 的开发就是建个工程、写写代码、分配引脚、编译、然后上板调试看结果而已。一些相对简单的FPGA 工程,姑且可以这么糊弄过去;但是稍微复杂一点的设计,这么开发起来就会显得极其低效和不专业;对于稍具规模的复杂工程,这样更是行不通的。

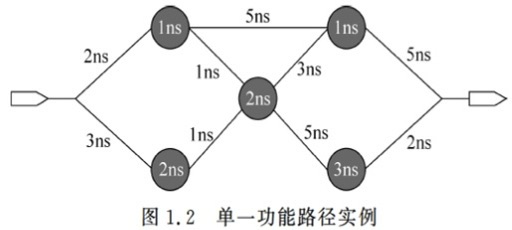

如图1.1所示,在FPGA 的基本开发流程中,设计仿真和设计约束必不可少,可以说它

们是 FPGA 设计中的重点和难点。

设计仿真难在环境的搭建、库的编译和配置(很多初学者往往止步于此),而仿真的有效性和准确性也是设计者开发功底的体现,一个好的设计就一定要配套好的仿真测试平台,以确保设计验证的快速高效。

设计约束涉及 FPGA 开发流程中的"约束输入""分析实现结果""设计优化"等环节,设计约束定义了设计工程在编译过程中为了实现最终的板级功能所需达到的设计要求。设计约束主要分为物理约束和时序约束。

物理约束主要包括1/0接口约束(如引脚分配、电平标准设定等物理属性的约束)、布局约束、布线约束以及配置约束。1/0接口的物理约束以及配置相关的物理约束,是设计中常用到的约束,但约束的方式和原理都相对简单易懂。对于布局约束或布线约束来说,只要掌握基本的方法和技巧,就能够在实际需要时进行应用。说得直白一些,物理约束无非就是一些位置定义和功能开关的设定,相对直观可视,不涉及很深的理论知识,易于理解和掌握。

时序约束则是涉及 FPGA 内部的各种逻辑或走线的延时,反应系统的频率和速度的约束。谈论处理器的处理性能时,常常会提到主频(主时钟频率)这个参数,它是一个很重要的指标,对 FPGA 器件来说也是一样的。现代 FPGA 设计,绝大多数功能是以时序逻辑实现的,也就是通过时钟触发工作,所以时钟频率的高低也是衡量 FPGA 处理能力的一个很重要的指标(但不是唯一指标),这个时钟频率的要求就是通过时序约束实现的。时序约束的目的很简单,让 FPGA编译工具合理地调配 FPGA 内部有限的布局布线资源,尽可能地满足设计者设定的所有时序要求(主要是将走线、逻辑电路等产生的延时限制在范围内)。

没有任何功能逻辑的 FPGA 器件,其内部结构就好比一块尚未焊接元器件的 PCB(Printed Circuit Board),而设计者为项目量身定制的FPGA 逻辑功能就好比 PCB 上的电阻、电容、芯片等各样元器件。PCB通过导线将具有相关电气特性的信号相连接,这些电气信号在 PCB上进行走线传输时势必会产生一定的传播延时(一般定义为 0. 17ns/in,1in=2.54cm)。FPGA 内部也有非常丰富的可配置的布线资源,用于 FPGA 内部各个逻辑节点的导通,这些走线和 PCB 的走线一样,也会由于走线的长短不同而产生或大或小的传输延时(简称"走线延时")。PCB上的信号通过任何一个元器件时(哪怕只是一个小小的电阻或电容)都会产生一定的延时,FPGA的信号通过逻辑门电路进行各种运算处理时也会产生延时(简称"门延时")。在半导体工艺发展的早期,门延时远大于走线延时,以至于走线延时可以忽略不计,但在进入深亚微米乃至纳米工艺之后,门延时被不断地优化降低,使得今天的芯片和 FPGA 设计中,走线延时也成为不可忽略的延时"大头"。那么,问题来了,一个信号从 FPGA 的一端输入,经过一定的逻辑门电路处理后从 FPGA 的另一端输出,这期间会产生多大的延时呢?一组总线的多个信号从 FPGA 的一端输入,经过一定的逻辑门电路处理后从 FPGA 的另一端输出,这条总线的各个信号的延时一致吗?之所以需要关心这此问题,是因为过长的延时或者一条总线多个信号传输延时的不一致,不仅会影响FPGA 本身的性能(能够使用的最高时钟频率和所使用的时钟频率是否能正常工作),而且也会给FPGA之外的电路或者系统带来诸多的问题。

在 FPGA 器件中需要进行时序约束与分析,也正是基于上述这些问题的考虑。FPGA的时序分析与约束,通俗的理解,可以定义为:设计者根据实际的系统功能,通过时序约束的方式提出时序要求;FPGA 编译工具根据设计者的时序要求,进行布局布线;编译完成后,FPGA编译工具还需要针对布局布线的结果,套用特定的时序模型(FPGA 器件厂商能够使用这样的模型,对 FPGA 布局布线后的每一个逻辑电路和走线计算出延时信息),给出最终的时序分析和报告;设计者通过查看时序报告,确认布局布线后的时序结果是否满足设计要求。

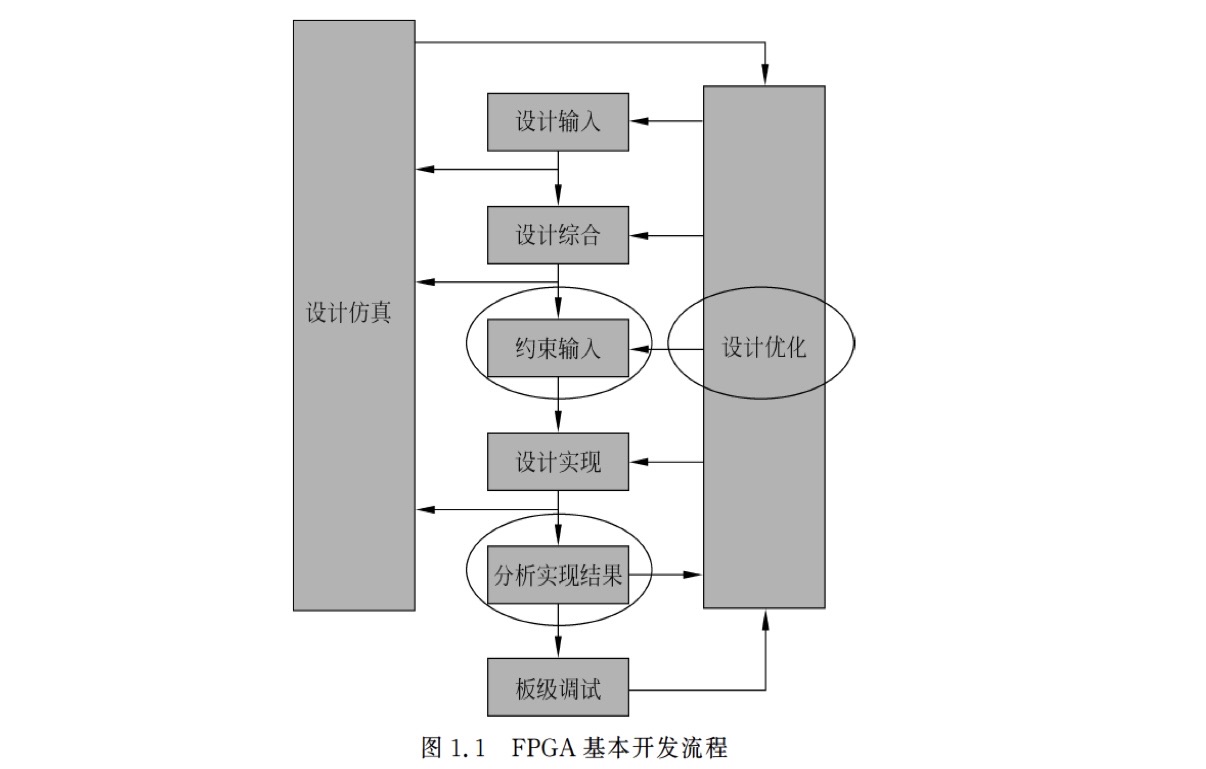

下面举一个最简单的例子说明时序约束与分析的基本概念。如图1.2所示,假设信号从FPGA 的一侧输入,在 FPGA 内部经过一些逻辑处理(产生逻辑延时)和走线连接(产生走线延时),最终从 FPGA 的另一侧输出,图中给出了多条可能实现该功能的路径。遍历所有可能的路径,可以算得延时分别为14ns,24ns,15ns,16ns,21ns,17ns,18ns。可以把这些路径上的圆形节点认为是 FPGA 中所需的逻辑单元及其布局,两个节点之间或输入/输出端口与节点之间的连线认是 FPGA 中的走线。这么多的布局布线方式,如果设计者不对FPGA 提出约束要求,告诉 FPGA编译工具设计者所期望的目标延时(时序要求),那么默认情况下,FPGA 编译工具很可能就随便找一条路径进行布局布线了。如果实际上设计者对此系统的延时是有一定要求的,如延时必须不高于 15ns。那么如果运气好,FPGA 编译工.具选择了14ns或15ns 这两条最短延时路径,系统尚且可以正常稳定地工作;但是,按概率算也还有2/3的可能性,FPGA 编译工具会选择大于 15ns 的另外4条路径,此时设计者的实际延时要求将无法得到满足。所以,在对系统延时(时序)有要求的情况下,不能指望FPGA 编译工具自己"猜测"或靠"碰运气"保证系统延时要求得到满足。需要将对系统的所有时序要求通过时序约束的方式告诉 FPGA编译工具。这样,FPGA 编译工具工作起来就会有的放矢。而且布局布线结束后,也可以通过查看开发工具给出的时序分析报告确认时序要求执行的状况。这正是对 FPGA 设计进行时序约束和时序分析的意义所在。