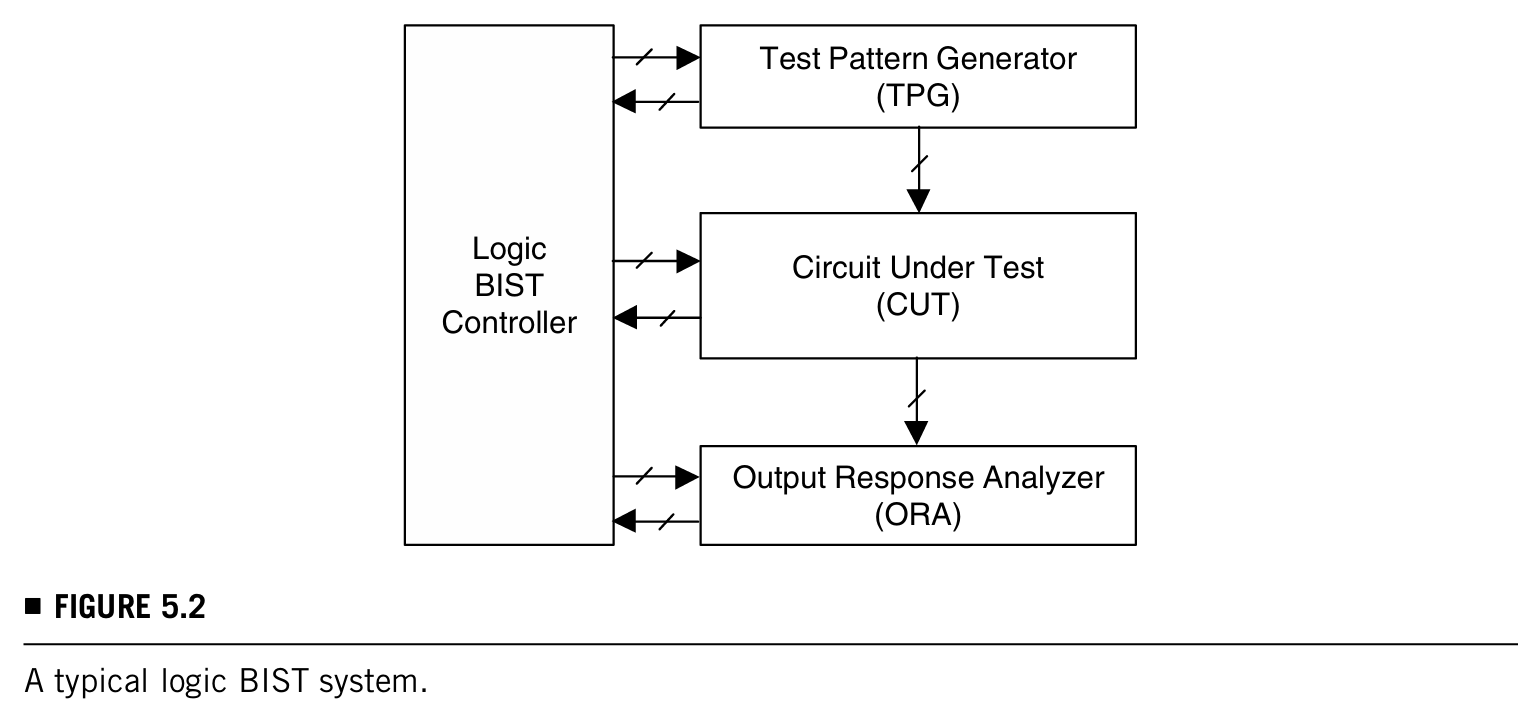

下图展示了一个典型的structural offline BIST技术:

分为以下几个部分:

- test pattern generator (TPG):自动生成测试向量

- circuit under test (CUT):测试向量被施加到待测电路上

- output response analyzer (ORA):自动压缩CUT的输出响应内容,形成一个signature

- logic BIST controller :生成时序控制信号(包括scan使能信号和时钟),用于协调TPG,CUT,and ORA三部分的工作,最后产生一个测试通过没通过的指示(将final signature 和golden signature进行对比)

注意:以上的过程都要遵守BIST-specific design rules,后面单独有一节讲这些规则。

下面是structural offline BIST的三个优点:

- 可以有效检测和报告板上与系统中的错误而且提供诊断信息(电路即便是被集成到板上也能测试,让系统修复变得简单可行);不需要外部测试机就可以测试

- 可以在芯片上容易地追溯错误;一些没有被软件模拟的缺陷能被测出来

- 测试花费更少,比如减少测试时间、减少测试机存储的空间、或者测试机相关的花费

下面是structural offline BIST的缺点:

- 需要处理好unknown值(也就是需要注意一些BIST-specific design rules)

- 因为BIST大多数时候用的pseudo-random patterns,所以要多加额外的测试点去提升故障覆盖率(测试覆盖率可能比用scan低)

5.2 BIST DESIGN RULES

LBIST与传统的scan相比需要更多严格的设计规则。

LBIST的规则限制主要与unknown (X) values的传播相关,因为它的出现会篡改signature,而在scan中仅仅是会降低测试覆盖率而已。

BIST design rules:需要满足所有的scan design rules和BIST-specific design rules。满足所有设计要求就能把设计转换为BIST-ready core。

5.2.1 Unknown Source Blocking(未知来源拦截)

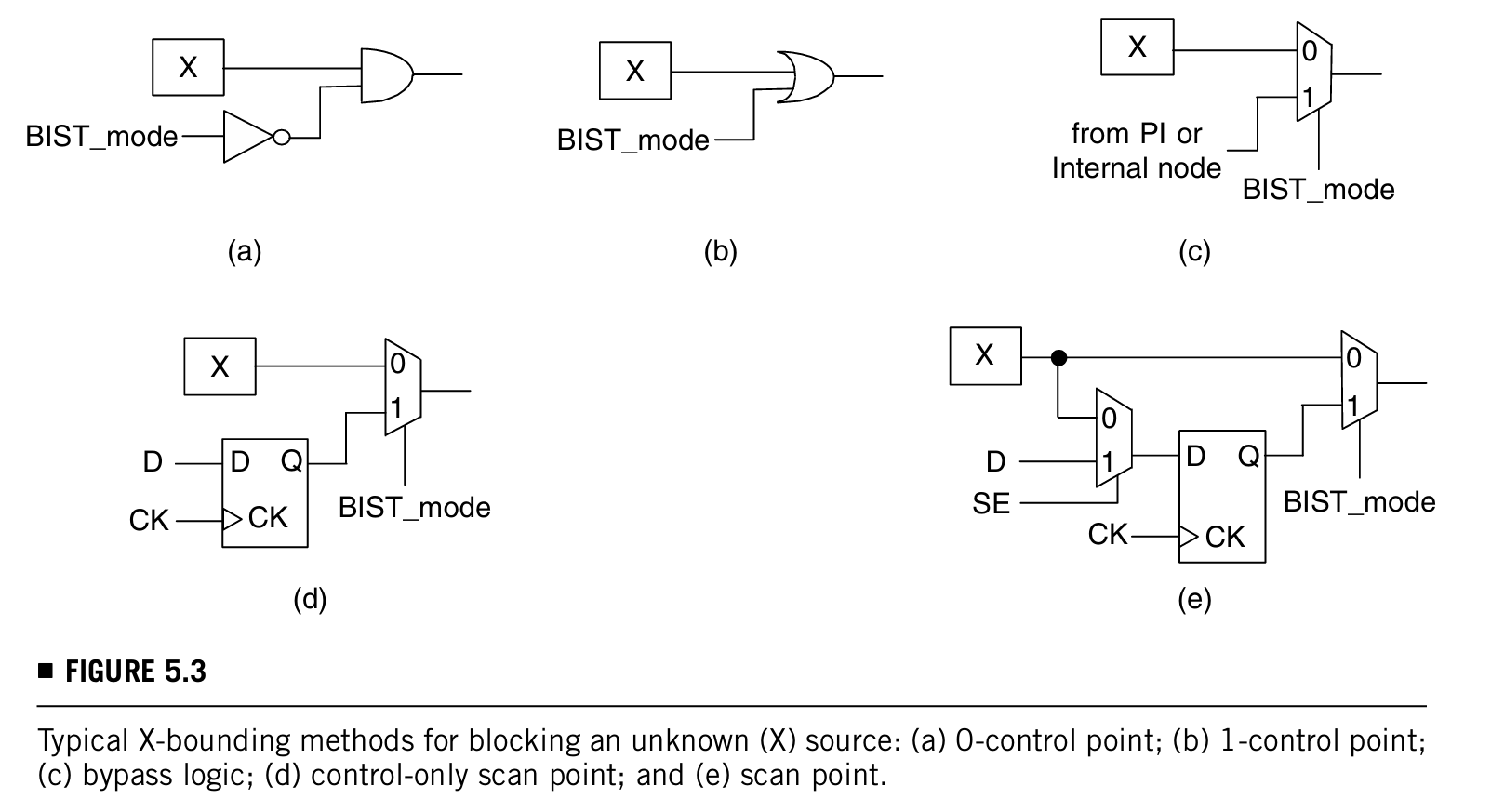

unknown (X) 可能会被直接或者间接地传播到ORA,它们必须被拦截并用DFT修复方法进行修复,这种方法叫做X-bounding 或者X-blocking。下图介绍了5种X-bounding方法的应用:

分别为:

- 0-control point

- 1-control point

- bypass logic

- control-only scan point

- scan point

这个方法也存在一些问题:

- 它可能会增加设计的面积

- 可能会影响时序

根据不同的情境选择上面5种方法。下面的小节就是各种情境。

5.2.1.1 Analog Blocks

analog blocks就是指analog-to-digital converters (ADCs),模拟模块的输出可能是unknown的,它必须是一个known的值,可选的方法是:

- 0-control point

- 1-control point

- bypass logic

- control-only scan point

推荐后两种,因为故障覆盖率更高。

5.2.1.2 Memories and Non-Scan Storage Elements

memories有:

- dynamic random-access memories (DRAMs)

- static random-access memories (SRAMs)

- flash memories

non-scan storage elements有:

- D flip-flops

- D latches

针对以上两大种来源的unknown值典型地采用Bypass logic方法。

5.2.1.3 Combinational Feedback Loops

要避免出现combinational feedback loops,如果它们实在无法避免,那么这个环必须要用以下几种方法打破:

- 0-control point

- 1-control point

- scan point

推荐使用scan point,因为它能实现更高的故障覆盖率。

5.2.1.4 Asynchronous Set/Reset Signals(异步置位/复位信号)

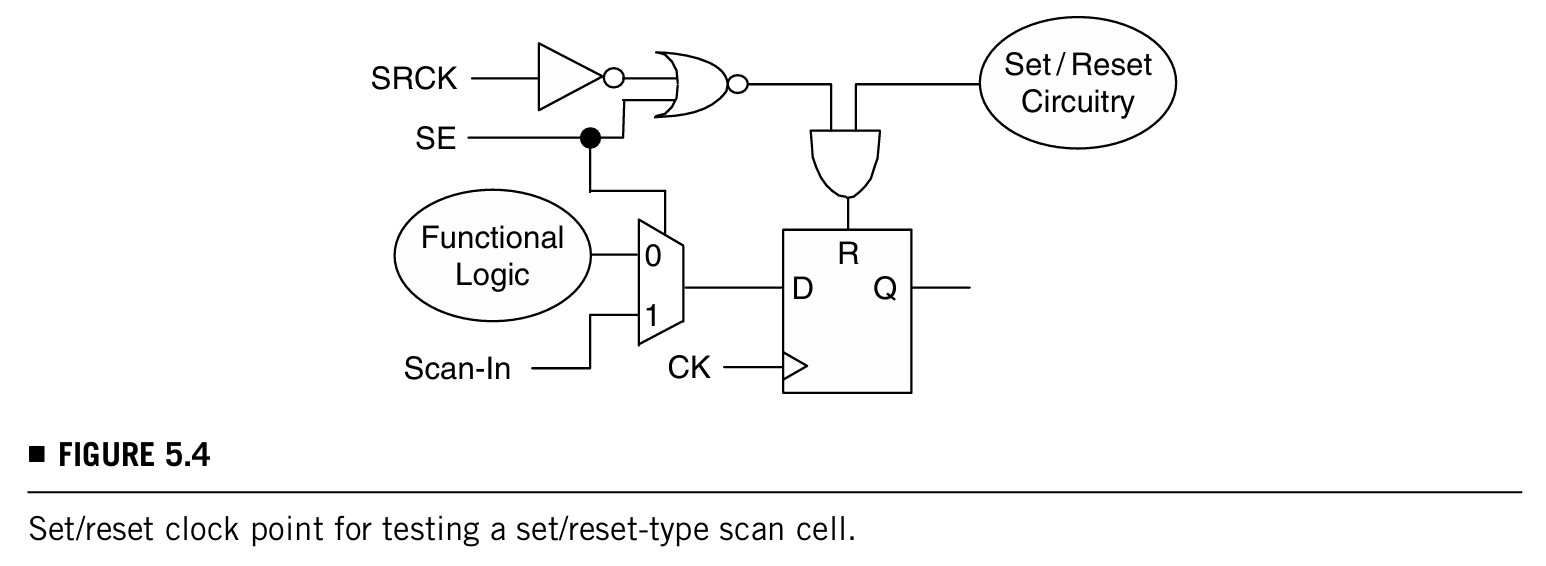

set/reset disable pin必须要在shift operation时被设置为1,也就是不让这个pin起作用,在第2章中用到的是一个外部的external set/reset disable (RE) pin,但是在BIST中建议用内部的已知信号existing scan enable (SE) signal去保护这个shift过程并且在每一个set/reset signal上加上一个时钟set/reset clock point (SRCK),如下图:

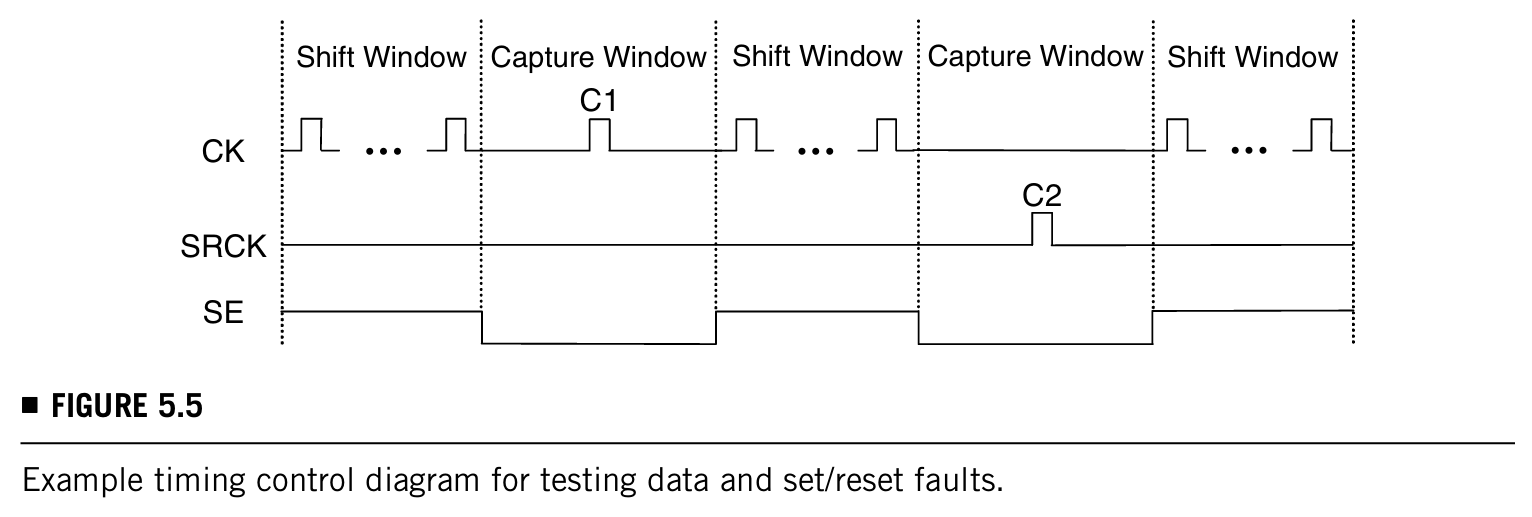

在测试all data和set/reset faults时,注意是在不同的BIST区域中,如下图:

- 在第一个capture window中,system clock (CK)有效,SRCK是held状态

- 在第二个capture window中,SRCK有效,system clock (CK)是held状态

用这样的方式避免了竞争和冒险,而且防止了scan cells中的数据被破坏。

5.2.1.5 Tristate Buses

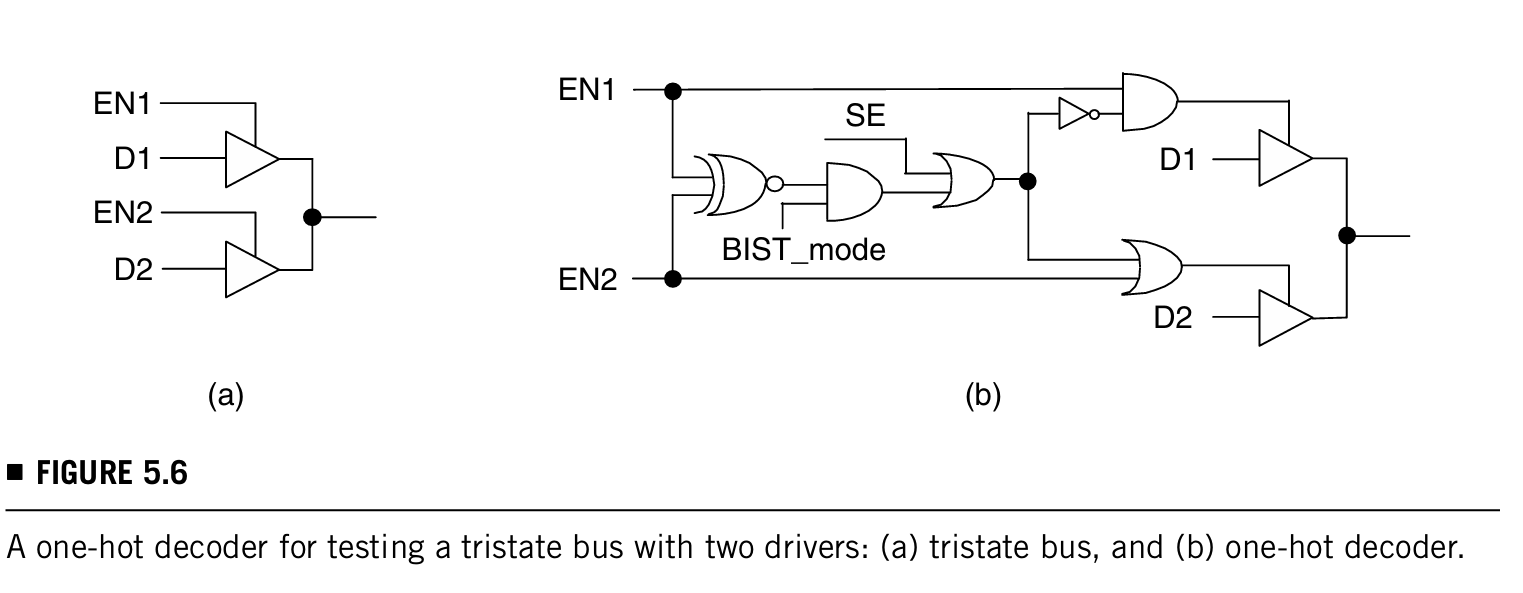

要防止总线争抢,用到的下图所示的one-hot decoder可以使shift或者capture时只选择一个驱动: