VHDL设计-基于四状态Moore型状态机

一、分析实验目的

- 理解 Moore 型状态机原理:掌握Moore型状态机的工作原理,特别是其输出仅依赖于当前状态的特性。

- 学习 VHDL 状态机设计:通过设计一个四状态的Moore型状态机,学习如何在VHDL中实现状态机的编码和逻辑控制。

- 熟悉 Quartus II 设计流程:利用Quartus II软件进行VHDL代码的编写、编译和仿真,熟悉其操作流程和界面。

- 提高设计和调试能力:通过设计、仿真和调试过程,提高解决实际硬件设计问题的能力,特别是在状态机设计中的应用。

二、描述实验过程

- 环境准备:安装Quartus II软件,准备必要的硬件描述语言知识,特别是VHDL。

- 项目创建:在Quartus II中创建一个新的VHDL项目,选择合适的FPGA或CPLD器件。

- 代码编写:编写四状态Moore型状态机的VHDL代码,包括实体声明、架构描述和状态转换逻辑。

- 编译代码:保存VHDL文件,使用Quartus II进行编译,检查是否有语法错误或逻辑错误。

- 仿真测试:创建仿真文件,设置测试向量,运行仿真,观察状态机的输出是否符合预期。

- 结果分析:分析仿真结果,验证状态机的功能是否正确,特别是状态转换和输出逻辑。

- 调试优化:如果仿真结果不符合预期,根据错误信息进行代码调试和优化。

实验环境描述:QuartusII

实验操作过程及配置说明(关键界面一律使用截屏,如,原理图输入设计图需将电脑时间进行同一界面截图;波形仿真需与本电脑的IP地址以及电脑时间进行同一界面截图;出现异常或不成功的操作,需要分析原因并在实验报告中记录):

说明:在VHDL代码编译之后,将门级网表进行截图并放在编译之后的内容之中。VHDL设计-基于四状态Moore型状态机不用波形仿真。

一、VHDL设计-基于四状态Moore型状态机

二、实验操作过程及配置说明

(一)创建项目

- 打开Quartus II软件,选择 File > New Project Wizard。

- 创建新项目,指定项目名称four_state_moore_state_machine和位置。

- 选择适当的FPGA或CPLD器件型号,完成项目创建。

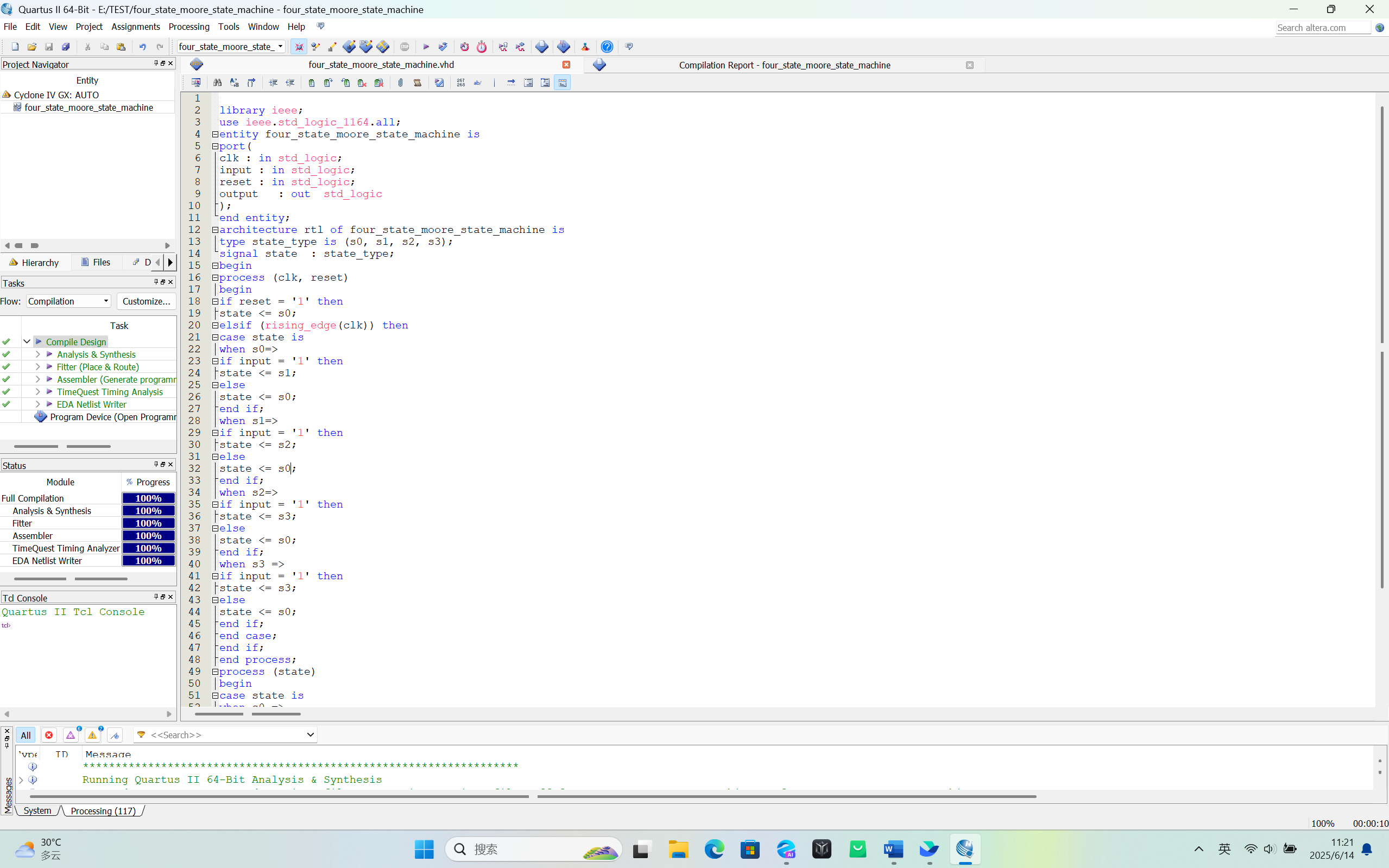

(二)编写 VHDL 代码

- 在项目中创建一个新的VHDL文件(例如:FourStateMooreMachine.vhd)。

- 编写四状态Moore型状态机的VHDL代码。

截图:

(三)编译设计

- 保存VHDL文件。

- 在Quartus II工具栏中点击 Start Compilation 图标,或选择 Processing > Start Compilation 来编译设计。

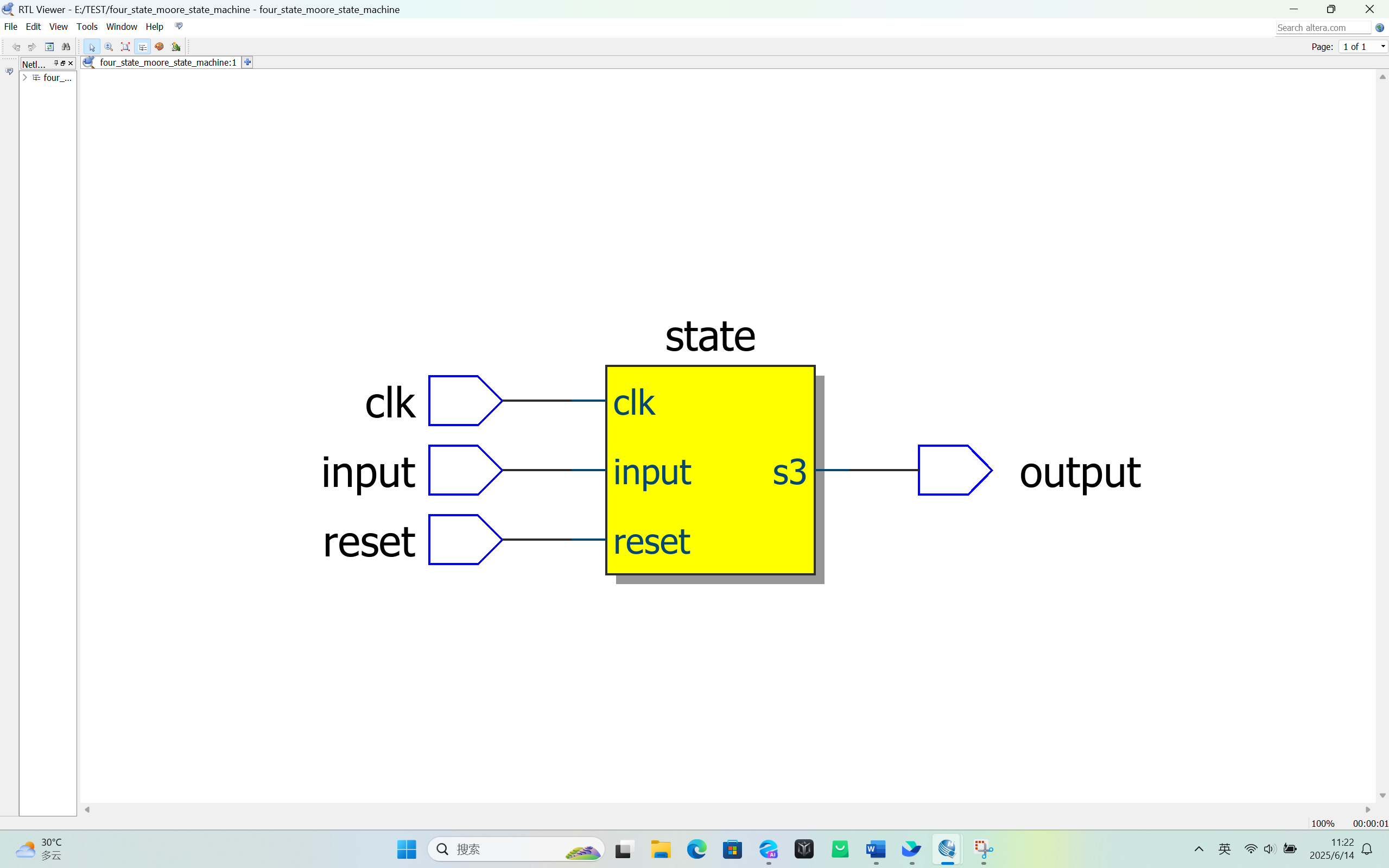

(四)查看门级网表

- 编译完成后,查看门级网表。

- 在Quartus II中,选择 Assignments > Settings,在 Category 中选择 EDA Tool Options,在 Device 中选择 RTL Schematic View。

截图:

二、练习

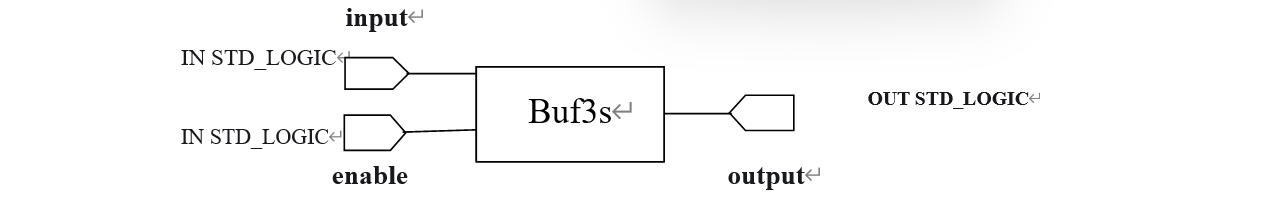

- 画出与下列实体描述对应的原理图符号。用下列图形工具绘制

- ENTITY buf3s IS

PORT(input: IN STD_LOGIC;

enable: IN STD_LOGIC;

utput:OUT STD_LOGIC);

END buf3s;

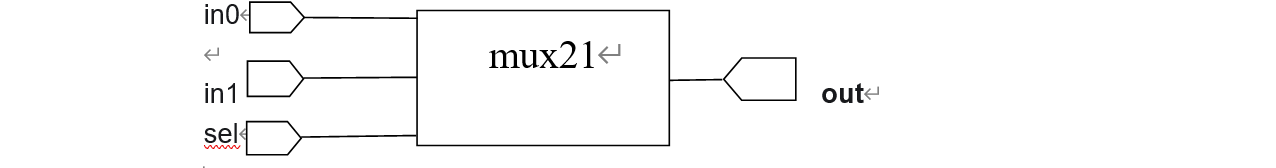

2**.ENTITY mux21 IS**

PORT (in0, in1, sel: IN STD_LOGIC;

output: OUT STD_LOGIC);

END mux21;

3.写出3输入与非门的实体描述,输入a,b,c;输出y。

ENTITY NAND3 IS

PORT (

a : IN STD_LOGIC;

b : IN STD_LOGIC;

c : IN STD_LOGIC;

y : out STD_LOGIC );

END NAND3;

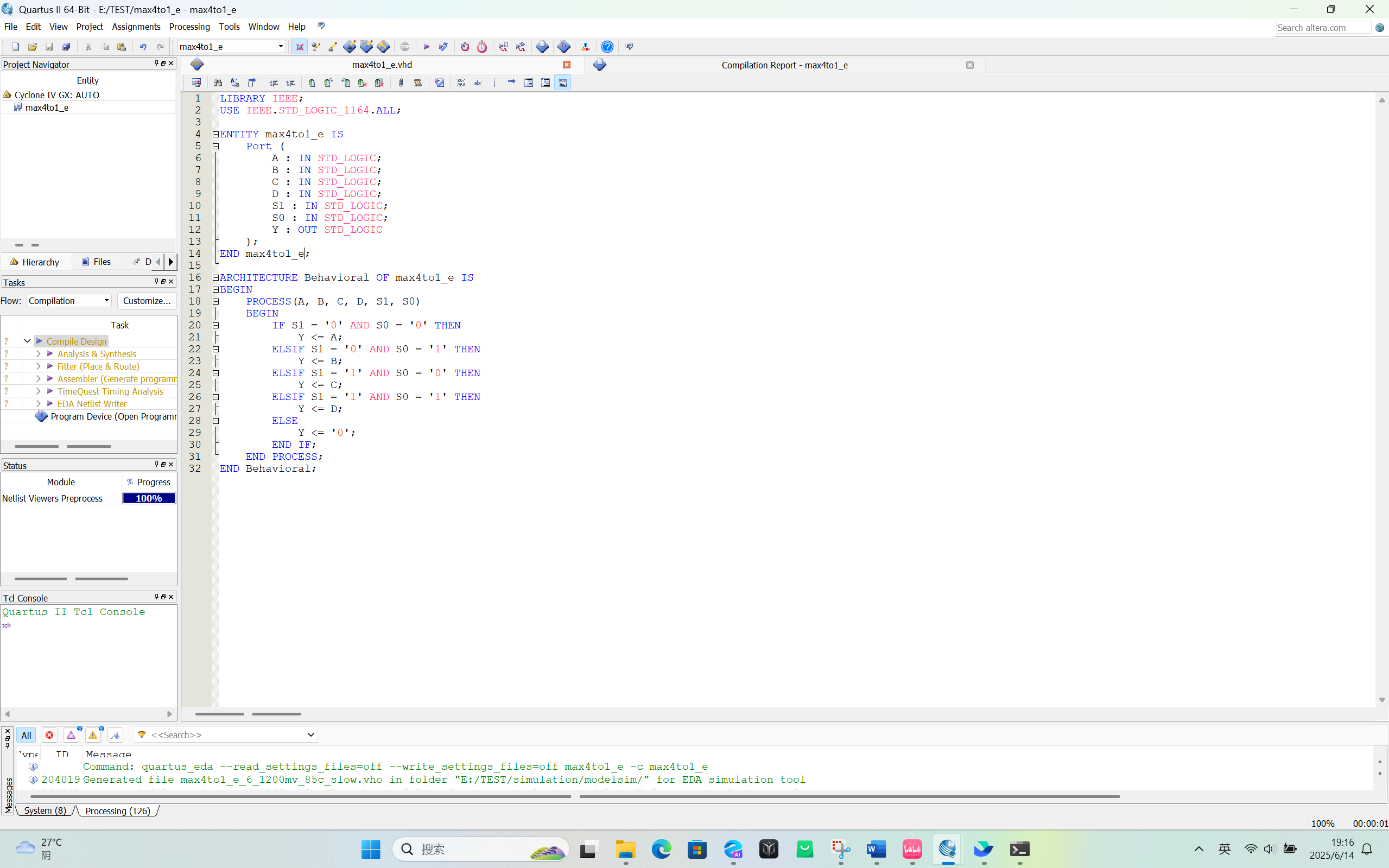

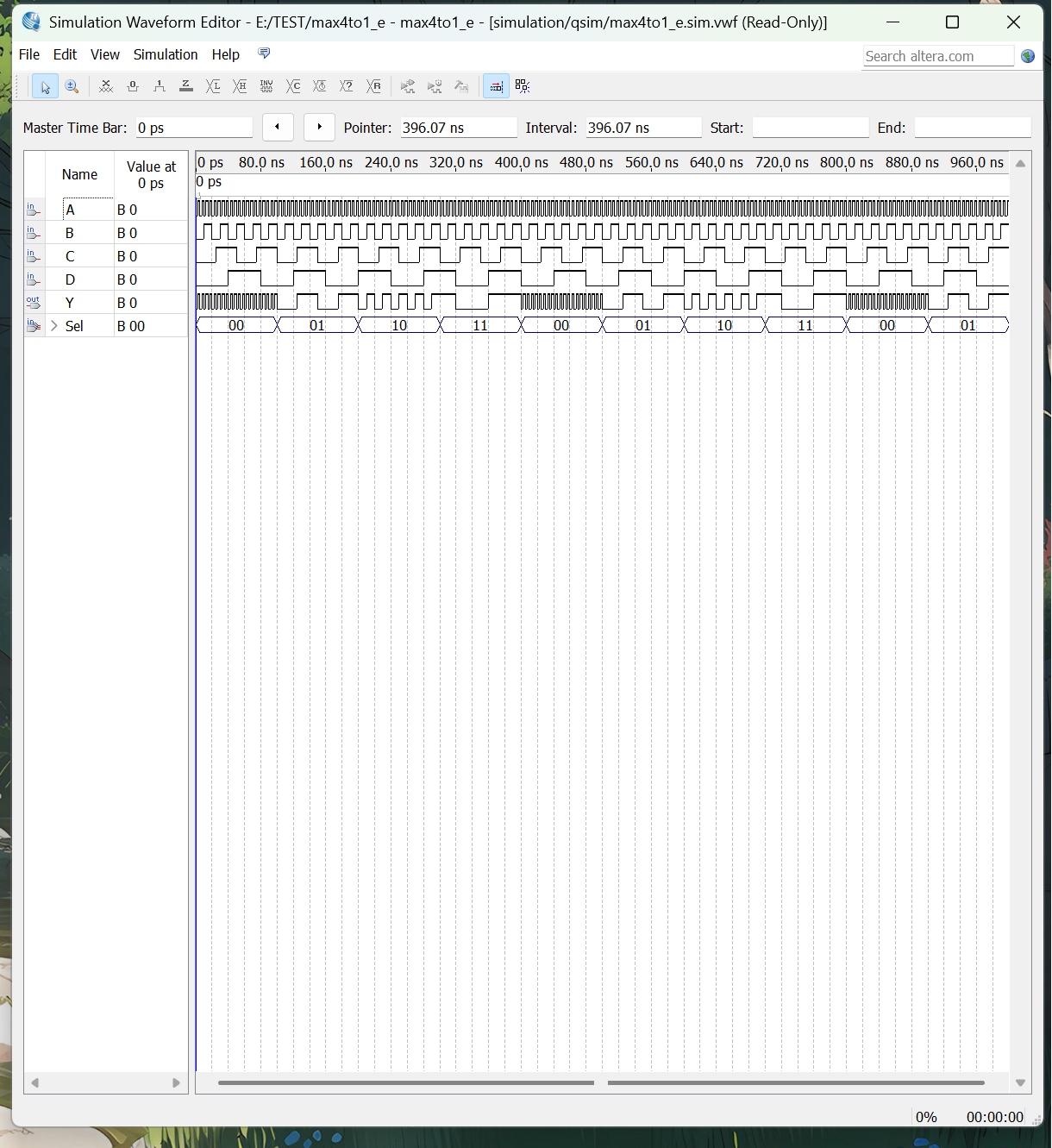

4.根据下列真值表写出4选1多路选择器的VHDL描述。选择控制信号为s1和s0,输入信号为a,b,c,d,输出信号为y,并实现仿真波形图加以验证。

提示:使用process和if语句

s1 s0 y

0 0 a

0 1 b

1 0 c

1 1 d

总结和分析:

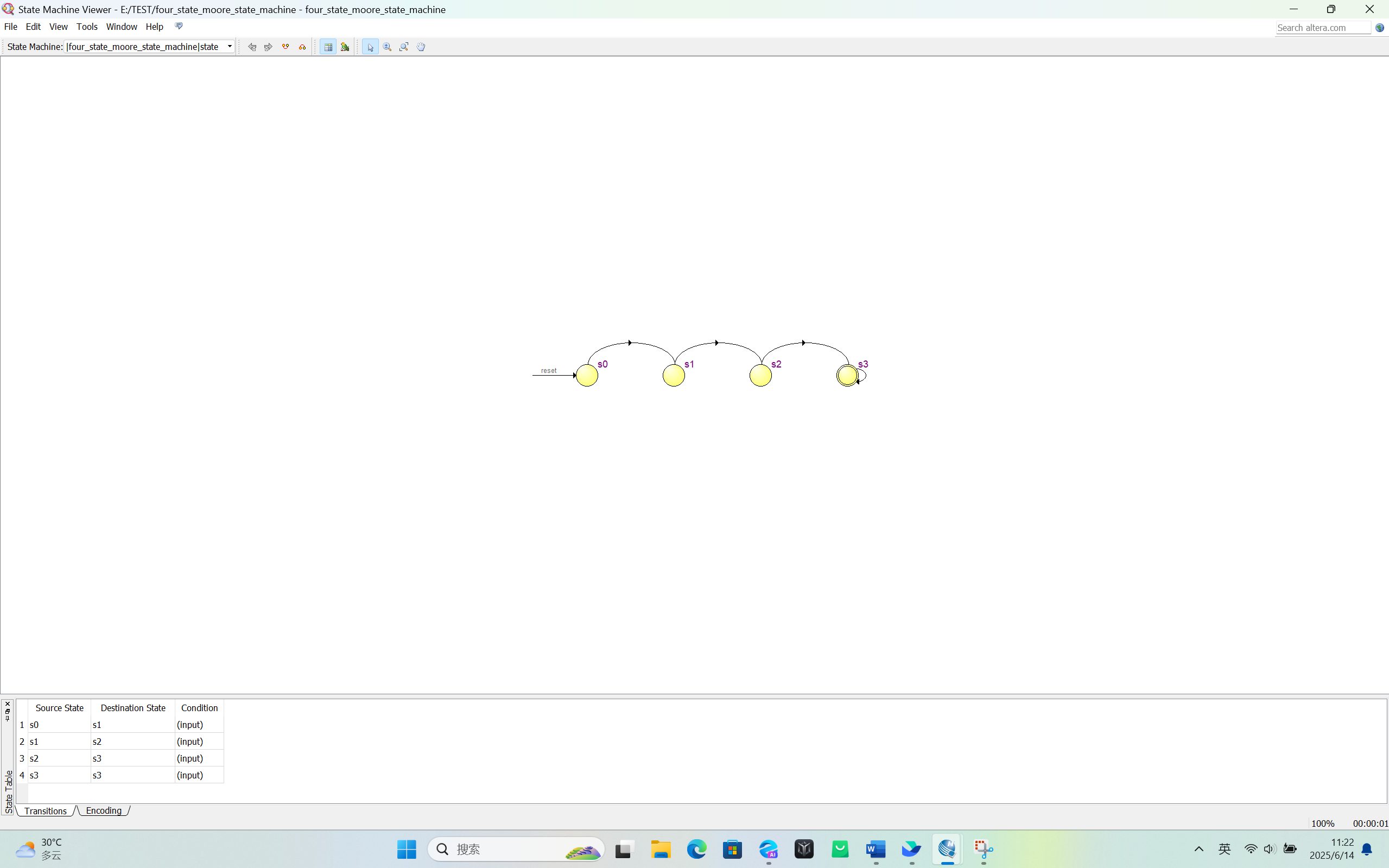

VHDL设计 - 基于四状态Moore型状态机

本实验成功实现了一个四状态的Moore型状态机,加深了对状态机工作原理的理解,特别是在设计状态转移和输出逻辑时的VHDL编码技巧。通过Quartus II的编译和门级网表分析,验证了设计的正确性,提高了对复杂数字电路设计的认识。

VHDL设计 - 3输入与非门

通过设计一个3输入与非门,掌握了VHDL中基本逻辑门的实现方法。实验中,通过简单的VHDL代码实现了与非门的逻辑功能,并通过门级网表验证了设计的正确性,增强了对VHDL编程和数字逻辑设计的理解。

VHDL设计 - 4选1多路选择器

本实验通过VHDL设计了一个4选1多路选择器,实现了根据选择信号动态选择输入信号并输出的功能。使用process和if语句实现了多路选择器的逻辑控制,并通过仿真波形图验证了设计的正确性,提高了对组合逻辑电路设计和VHDL编程的掌握。