APU Cluster

-

什么是APU

APU:Accelerated Processing Unit,加速处理器,整个soc的控制单元。

包含4个cluster,每个cluster里有4个核

-

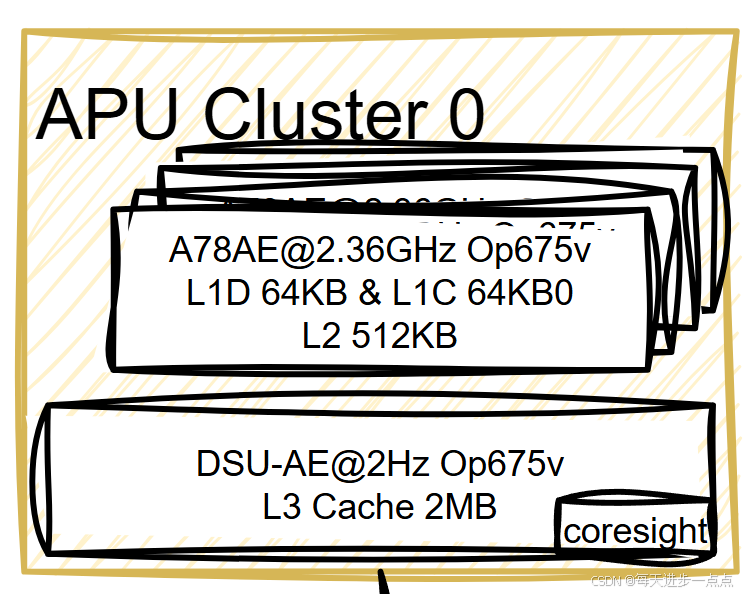

apu cluster 0:四核架构(多核架构)

apu cluster = 一个包含多个cpu核心的集群(比如4核 cortex - A78)

每个cluster内部有4个core,L1D 64KB和L1C 64KB和L2 512KB都为每个core独享

L3 2MB为每个cluster独享

-

L1/L2/L3的区分

-

区分L1/L2/L3之前,先区分缓存cache 和内存DDR

缓存是一个高速的"临时休息区",用于存放处理器最可能马上要用的数据,以减少访问远处"大仓库"(DDR)的次数,从而提升整体系统性能。两者是协作关系,而不是包含关系

-

L1/L2/L3是缓存层级(Cache Hierarchy),目的是让 CPU 更快地访问数据,避免每次都去慢速的 DDR 内存

|-----|---------------|------------|---------------|------|---------------|

| 缓存 | 全称 | 特点 | 速度 | 共享性 | 类比 |

| L1 | Level 1 Cache | 最靠近 CPU 核心 | 极快(1~3 周期) | 每核私有 | 你手边的笔记本(随手可拿) |

| L2 | Level 2 Cache | 第二层缓存 | 快(10~20 周期) | 每核私有 | 办公桌抽屉(几步就能拿到) |

| L3 | Level 3 Cache | 最后一级缓存 | 较慢(30~50 周期) | 多核共享 | 办公室文件柜(需要走过去) |

| DDR | / | / | / | / | 公司档案室(要坐电梯下去) | -

APU Clusters

- APU:Accelerated Processing Unit ,加速处理器,整个SoC的控制单元|

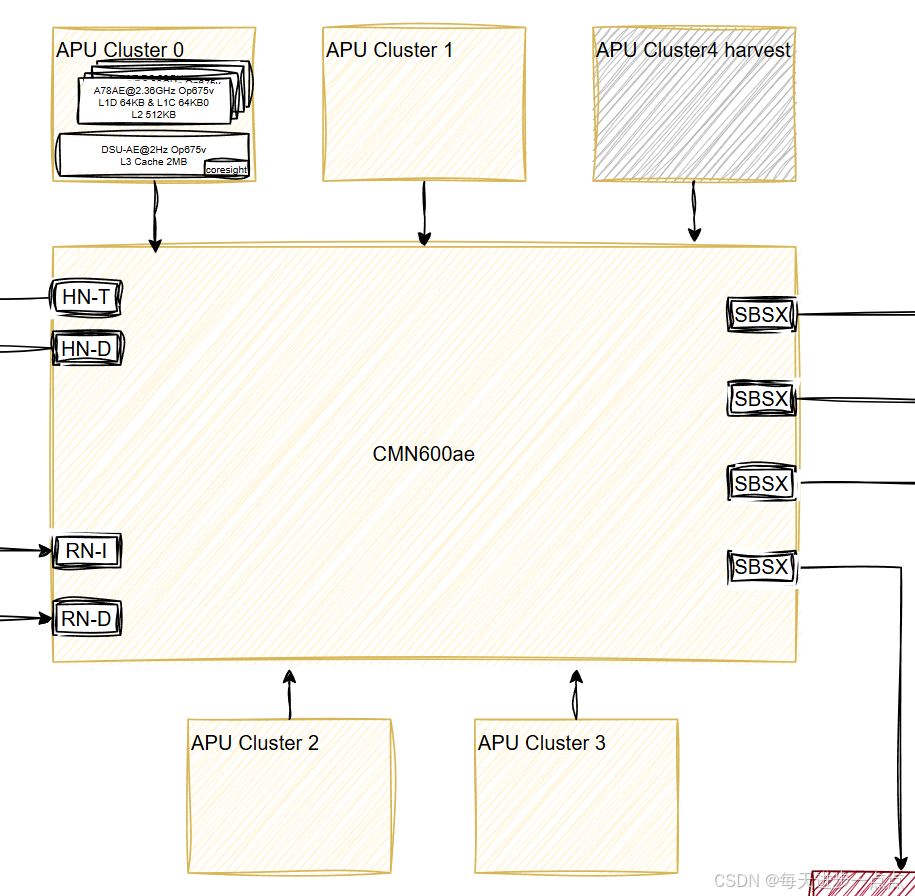

包含4/5个Cluster,每个Cluster中有4个核 - 5个APU cluster通过cmn600ae总线相连,其中有4个cluster是实际工作的,第五个cluster是harvest

看不懂的话,先看这里的补充知识:

- SBSX:在 ARM CMN600/CMN600AE 架构中,SBSX是 "Slave Interface for System Bus" 的缩写

- 功能定位:SBSX是CMN网络的从设备接口(slave port),用于连接非一致性外设或内存控制器

- 每个SBSX对应一个CHI(Coheren Hub Interface) Slave Port ,用于挂载DDR控制器

- HN-T/HN-D/RN-I/RN-D

|------|----------------------------|---------------------------------------------------------------|

| HN-T | Hub Node - Transaction | 处理 地址/控制事务 |

| HN-D | Hub Node - Data | 专门处理 数据传输 |

| RN-I | Root Node - Interface | 连接 ACE-Lite 或 AXI 总线(如连接 MCU、传感器 hub、CAN/FlexRay 控制器) |

| RN-D | Root Node - Data | 专用于大数据流通道,例如摄像头 RAW 数据输入(来自 ISP) |

对于HN-T/HN-D,重点:

将事务(control)与数据(data)物理分离,实现低延迟 + 高吞吐,特别适合自动驾驶中实时性要求高的场景(如摄像头帧数据流 + 控制指令并行传输)。

对于RN-I/RN-D,重点:

RN-I 可能连 MCU 协处理器 或 ASIL-D 安全核 ?

RN-D 很可能直连 BPU 的数据输入队列 或 VPU 的图像输入通道

| 缩写 | 全称 | 角色 | 所属层级 | 典型连接对象 |

|---|---|---|---|---|

| SBSX | Snoop Bus Slave eXtension | CMN 从端口(带监听) | CMN 网络边缘 | DDR、BPU、PCIe、HSM |

| HN-T | Hub Node - Transaction | 事务/控制通道 | CMN 网络内部 | APU/BPU 的 CHI 请求端 |

| HN-D | Hub Node - Data | 数据通道 | CMN 网络内部 | APU/BPU 的 CHI 数据端 |

| RN-I | Root Node - Interface | 非相干接口(控制) | CMN 网络边界 | MCU、CAN、寄存器空间 |

| RN-D | Root Node - Data | 非相干数据流通道 | CMN 网络边界 | ISP、雷达、BPU 数据输入 |

这些设计充分体现了车规级(CMN600AE(AE))高阶自动驾驶芯片的核心诉求:

- 高带宽(分离式 HN-T/D + 多 SBSX)

- 强一致性(SBSX 支持 snoop,保障 BPU/CPU 共享数据正确性)

- 功能安全隔离(RN 提供硬件级域隔离)

- 可扩展性(5 Cluster + harvest + 多接口)