嵌入式刷题硬件设计基础(一)

- FPGA和ASIC的区别?各自的适用场景?

- GPIO的上拉和下拉电阻的作用和选择

- LDO和DC-DC的区别是什么?各自适用于什么场景?

- PCB平时用什么工具画?常用的EDA工具有哪些?

- 三极管和MOS管的区别和应用场景

- 嵌入式系统的电源管理策略有哪些?

- 差分信号的优势是什么?在哪些场景中使用?

- 电阻、电容、电感的基本特性和在电路中的作用

- 1117稳压器的稳压范围是多少?最小压差范围和效率问题是什么?

- CAN总线的显性电平和隐性电平分别是什么?

FPGA和ASIC的区别?各自的适用场景?

FPGA= 可以反复改写的硬件电路

ASIC= 一次性定做、不能改的专用芯片

- FPGA(现场可编程门阵列)(Field Programmable Gate Array)

你可以把它理解成一块万能积木板。

里面有一堆现成的逻辑单元、连线

你写代码(Verilog/VHDL)进去,它就变成你想要的电路

写错了、想改功能?重新下载一遍就行,无限次改 - ASIC(专用集成电路)(Application Specific Integrated Circuit)

就是专门为某个功能定做的芯片,出厂就定型,永远不能改。

比如手机芯片、蓝牙芯片、GPU、CPU 都是 ASIC。

GPIO的上拉和下拉电阻的作用和选择

GPIO上拉/下拉电阻的作用:

上拉电阻:将引脚默认拉到高电平(VCC),防止浮空

下拉电阻:将引脚默认拉到低电平(GND),防止浮空

为什么需要:浮空引脚电平不确定,容易受干扰导致误触发。

阻值选择 :通常4.7kΩ-10kΩ

太小:静态功耗大,因为阻值小,电流大

太大:上拉能力弱,容易被干扰,稍微有点噪音电磁干扰啥的波动就很大

内部 vs 外部 :MCU内部上下拉电阻较大(30-50kΩ),驱动能力弱;

很多单片机引脚,软件一开,就自带上下拉,不用你在 PCB 上焊电阻。

这就是所说的有点太大了,所以高可靠场景用外部电阻

比如,典型应用:按键输入(上拉+按键接地)、I2C总线(外部上拉4.7kΩ)、复位引脚上拉。

LDO和DC-DC的区别是什么?各自适用于什么场景?

它们是干啥的?

都是把电压变成稳定的另一个电压(如 12V→5V、5V→3.3V)

LDO(线性稳压)

像电阻降压,多余电压变热浪费

噪声小、电路简单、便宜

只能降压,压差大时发热严重

输出纹波低

适用: 对噪声敏感的电路(音频、ADC、传感器、MCU),压差小、电流小。

DC-DC(开关电源)

像快速开关斩波,效率高、不怎么发热

噪声大、电路复杂

可升压 / 降压 / 升降压

输出纹波大

适用: 压差大、电流大、要省电 / 发热小的地方(电机、大功耗芯片、电池供电)。

PCB平时用什么工具画?常用的EDA工具有哪些?

Altium Designer:功能最强大,企业中最主流,原理图+PCB一体化,但正版很贵

KiCad:开源免费,功能越来越强,适合个人和小团队

立创EDA(LCEDA):国产在线EDA,和嘉立创PCB打样无缝衔接,对新手非常友好

等等。。。

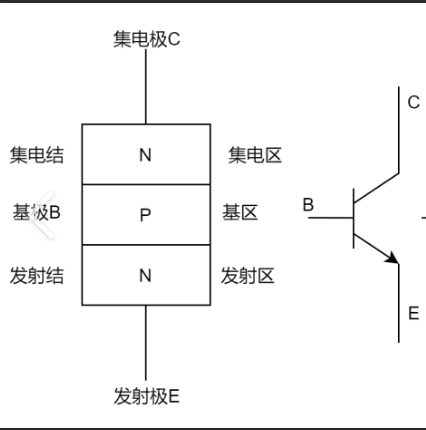

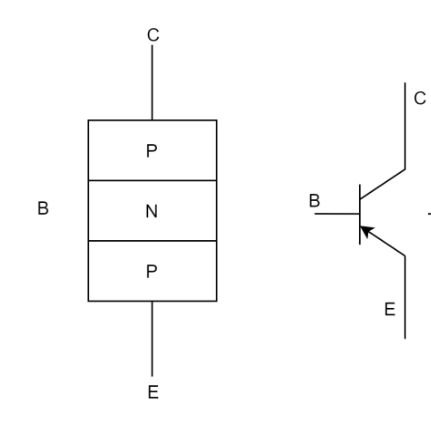

三极管和MOS管的区别和应用场景

三极管和MOS管的区别:

三极管(BJT):电流控制型

基极电流控制集电极电流

导通压降约0.3-0.7V

驱动电流大

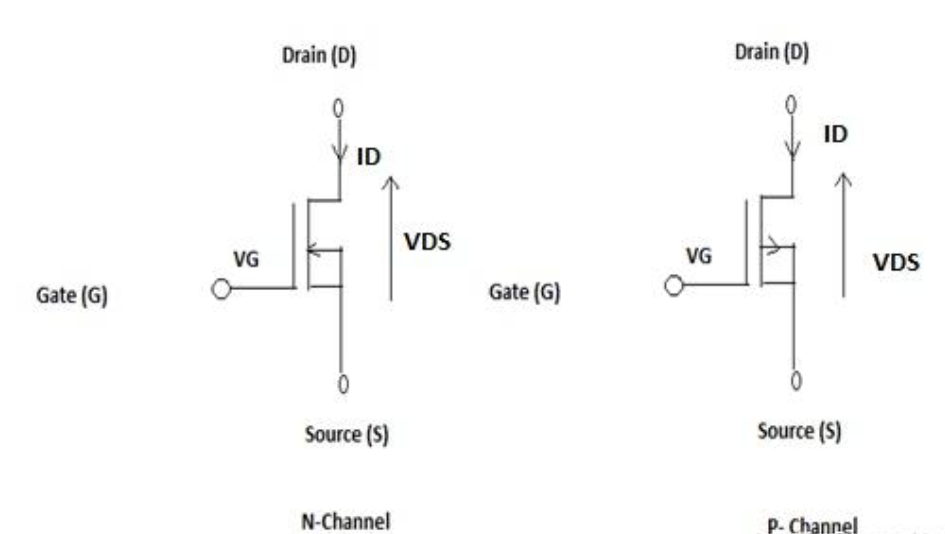

MOS管(MOSFET):电压控制型

栅极电压控制漏极电流

导通电阻低(mΩ级)

驱动功耗极小(栅极几乎不耗电)

应用场景:

三极管:小信号放大、简单开关

MOS管:电源开关、H桥电机驱动、DC-DC(大电流场景首选)

嵌入式中MOS管用得更多

嵌入式系统的电源管理策略有哪些?

1.动态电压频率调节(DVFS):负载低时降低CPU频率和电压

2.睡眠模式分级:

Sleep:CPU停止,外设运行

Stop:大部分时钟关闭,RAM保持

Standby:几乎全部关闭,只有RTC和唤醒引脚工作

3.外设按需开关:不用的外设关闭时钟

4.唤醒源设计:GPIO中断、RTC闹钟、通信接收唤醒

5.Tickless模式:RTOS空闲时关闭系统tick

设计原则:分析功耗预算 → 选择合适的低功耗模式 → 优化活跃时间

差分信号的优势是什么?在哪些场景中使用?

差分信号就是:

用两根线,传输一对大小相等、方向相反的信号。

一根叫 + 信号(D+)

一根叫 - 信号(D-)

最终接收端只看 两者的差值:V = V+ − V−

差分信号的优势:

1.抗干扰能力强:两条线上的共模干扰可以被接收端差分抵消(共模干扰 = 两根线一起被干扰,同涨同落。差分信号天生就能把它抵消掉。)

2.EMI低:两条线电流方向相反,辐射互相抵消(EMI 小 = 对外辐射的干扰小,不骚扰别的电路)

3.信号摆幅可以更小:判断依据是两线之差,不需要绝对电平

使用场景:

高速通信:USB、HDMI、PCIe、以太网

长距离传输:RS485、CAN总线、LVDS

抗噪环境:工业现场、汽车电子

PCB设计要求:差分对等长、等间距、紧耦合,避免在参考平面上跨越割缝。

电阻、电容、电感的基本特性和在电路中的作用

电阻、电容、电感的基本特性:

电阻®:阻碍电流,V=IR

作用:分压、限流、上下拉、匹配

电容©:存储电荷,隔直通交

作用:高低滤波、去耦电容、耦合、储能、定时

(去耦 = 去掉芯片之间的耦合干扰,比如在每个芯片电源脚旁边放一个小电容)

(耦合:用高通特性 → 传信号、隔直流)

特性:电压不能突变

电感(L):存储磁能,隔交通直

作用:滤波、储能(DC-DC)、抗EMI

特性:电流不能突变

1117稳压器的稳压范围是多少?最小压差范围和效率问题是什么?

嵌入式 / 单片机系统(最主流)

5V 转 3.3V:STM32、ESP8266/32、Arduino、树莓派等 3.3V 核心供电

开发板、最小系统板、传感器模块、蓝牙 / Wi-Fi 模块供电

AMS1117是常用的LDO稳压器,固定输出版本有3.3V和1.8V等。

稳压范围:输出1.5V~5V(可调版本)

最小压差(dropout):约 1.1V~1.3V(满载时),这意味着输出3.3V时输入至少要4.4V以上

最大输出电流:1A

效率问题:效率 = Vout/Vin。如果5V转3.3V,效率只有66%,1.7V×1A = 1.7W发热量大。所以大电流大压差场景不适合用LDO,应该换DC-DC。

应用时输入输出端都要加去耦电容(推荐22μF钽电容或陶瓷电容)。

CAN总线的显性电平和隐性电平分别是什么?

CAN总线是差分信号,用CAN_H和CAN_L两根线的电压差来表示逻辑电平:

显性电平(逻辑0):CAN_H ≈ 3.5V,CAN_L ≈ 1.5V,差值约2V。这时总线被某个节点主动驱动。

隐性电平(逻辑1):CAN_H ≈ CAN_L ≈ 2.5V,差值约0V。这时总线处于空闲状态(通过终端电阻拉平)。

关键特性:显性电平会覆盖隐性电平(类似"线与"),这是CAN总线仲裁机制的物理基础------同时发送时,ID值小的(显性位多的)节点赢得仲裁。