杰理蓝牙音箱开发板AC696N上演示降本设计:AC696N"省晶振"方案配置

引言

做杰理蓝牙音频系列芯片开发 ,成本敏感型产品(如走量的小音箱)往往要在物料上精打细算。一颗24MHz外部晶振虽然只要几毛钱,但量大了也是一笔成本。JL杰理AC696N开发板支持"省晶振"方案,直接用芯片内部的LRC时钟源,省掉外部晶振。

本文以杰理AC6966B开发板 为例,把配置步骤和注意事项整理出来,方便降本设计时参考。

杰理蓝牙音箱开发板AC696N上演示降本设计:AC696N"省晶振"方案配置

对于成本极度敏感的产品,去掉外部24MHz晶振能节省几毛钱。JL杰理AC696N支持使用内部LRC时钟源实现"省晶振"设计。

配置步骤(三步缺一不可)

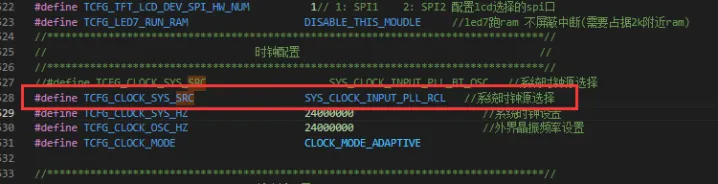

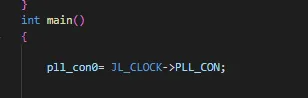

第一步:程序配置

在时钟初始化相关代码中,配置芯片使用内部LRC 作为时钟源,而不是外部晶振。

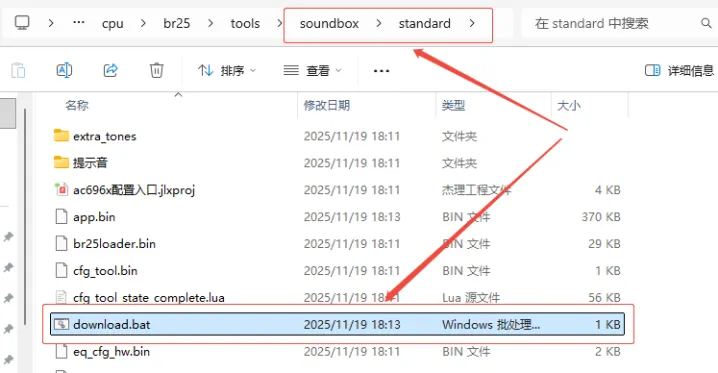

第二步:选用带LRC的Uboot

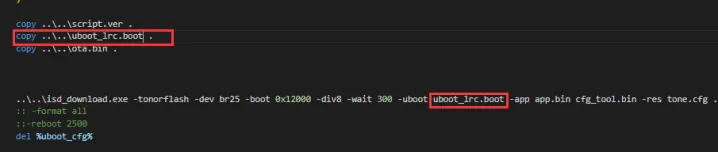

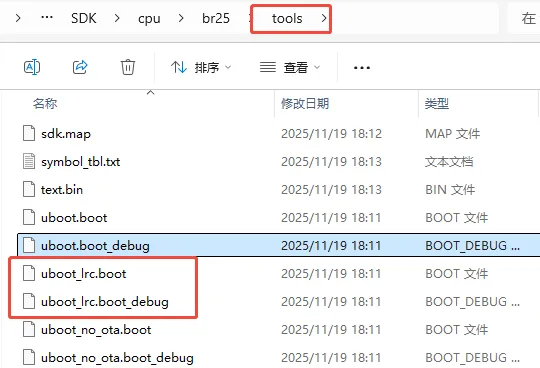

在SDK的download目录下,修改download.bat批处理文件,或直接在下载工具中选择带_lrc后缀的uboot文件,例如:

uboot_lrc.boot(量产用)uboot_lrc.boot_debug(调试用,带打印)

第三步:配置文件声明

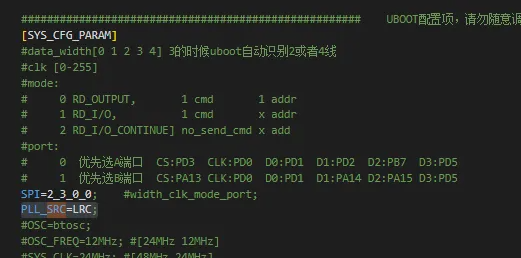

在固件打包配置文件isd_config.ini中,添加一行配置:

text复制下载

PLL_SRC=LRC;

这告知下载工具,此固件使用LRC时钟源。

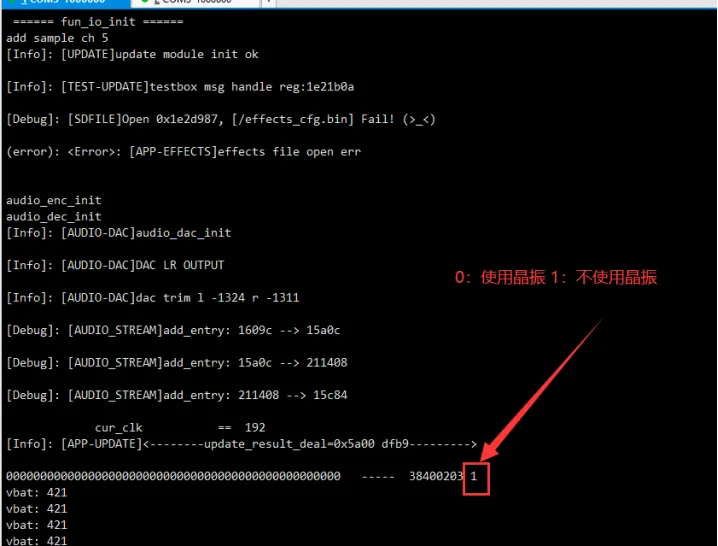

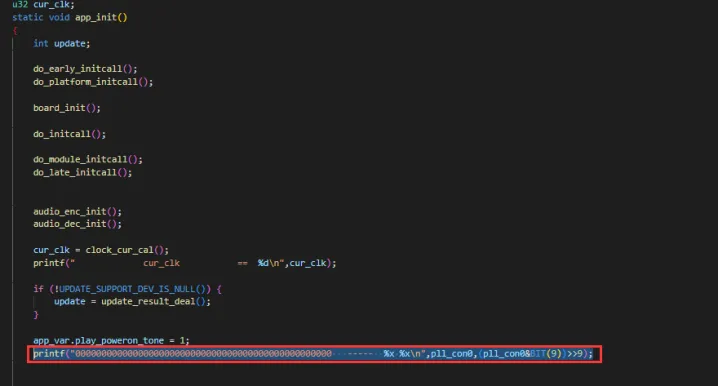

验证方法

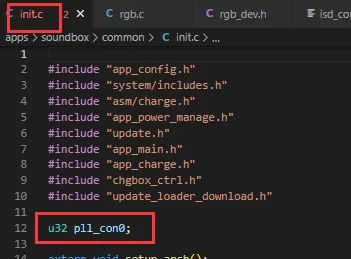

在串口初始化后的代码中,读取并打印PLL_CON0寄存器的特定比特位,可以确认当前时钟源是否为LRC。

注意事项

使用LRC时钟源,精度和稳定性会低于外部晶振,但对于时钟要求不高的普通蓝牙音频应用(如基础音箱、玩具等),通常可以接受。如果产品需要精准的时钟(如录音、高音质解码),建议保留外部晶振。

总结

"省晶振"是JL杰理AC696N 这类高性价比芯片的常用降本手段,通过程序配置、换LRC版uboot、修改配置文件三步即可实现。在杰理AC6966B开发板上验证通过后,可以放心用到量产产品中。记住:降本不降质,先评估产品对时钟精度的要求再决定是否省晶振。