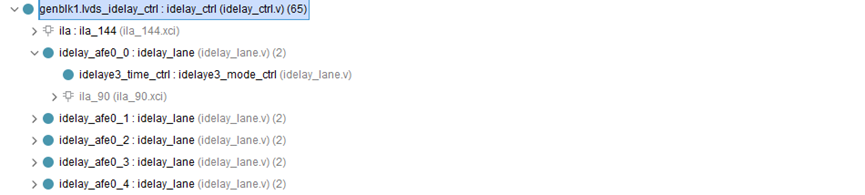

IDELAY校准模块:

idelay_ctrl是整个AFE数据接收系统的核心控制模块,工作在100MHz系统时钟域。

通过主状态机统一调度4个AFE(每个AFE有16个通道,工程有4个afe芯片,每个芯片物理通道16,两个通道共用一个物理通道,共计128通道)的IDELAY校准流程,

进入测试模式全范围延迟扫描逐步锁定最佳延迟退出测试模式正常工作;

同时负责与125MHz时钟域的idelay_lane进行跨时钟域交互。

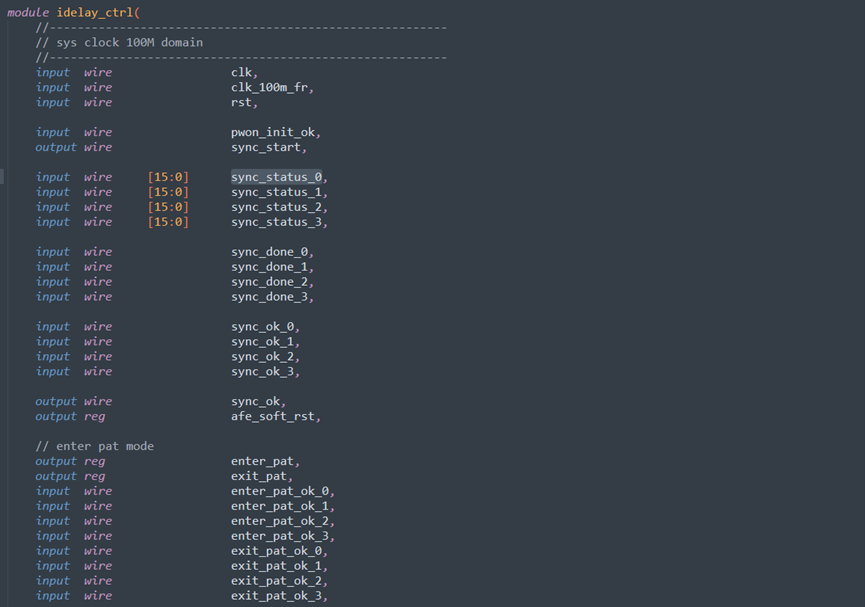

模块端口:

端口分为两个时钟域,上图为100M时钟域的信号,连接的模块是afe同步模块,afe测试模式进入退出模块,

上图为125M时钟域的信号,连接的模块lvds_s2p模块中的hssio ip的IDELAY延时控制端口,使用的是ip输出的125M pll clkout0,在模块内部要跨时钟域使用;

输入接口:

clk:100MHz系统时钟,

rst:全局复位,

pwon_init_ok:AFE上电完成标志,

sync_status_0~3[15:0]:每个AFE各通道的同步状态(来自afe_sync),

sync_done_0~3:每个AFE的同步完成标志(进入WORK后为1),

sync_ok_0~3:每个AFE的同步成功标志(所有通道连续匹配测试码成功),

enter_pat_ok_0~3:控制afe进入测试模式完成,

exit_pat_ok_0~3:控制afe退出测试模式完成,

clk_dly_03、rst_dly_03:各AFE的125MHz时钟和复位(来自afe_process的hssio ip),

rx_cntvalueout_0~3:各AFE的IDELAY当前值(只读,用于校准),

输出接口:

sync_start:同步启动脉冲(restart,用于触发afe_sync进入SYNC),

sync_ok:全局同步成功标志(所有AFE同步成功且锁定),

afe_soft_rst:软复位输出,用于复位AFE芯片,

enter_pat/exit_pat:控制AFE进入/退出测试模式的脉冲,

rx_cntvaluein_03、rx_en_vtc_03、rx_load_0~3:IDELAY控制信号,送到每个AFE的每个通道,控制时序与前述的IDELAYE3的time模式下的控制时序一致;

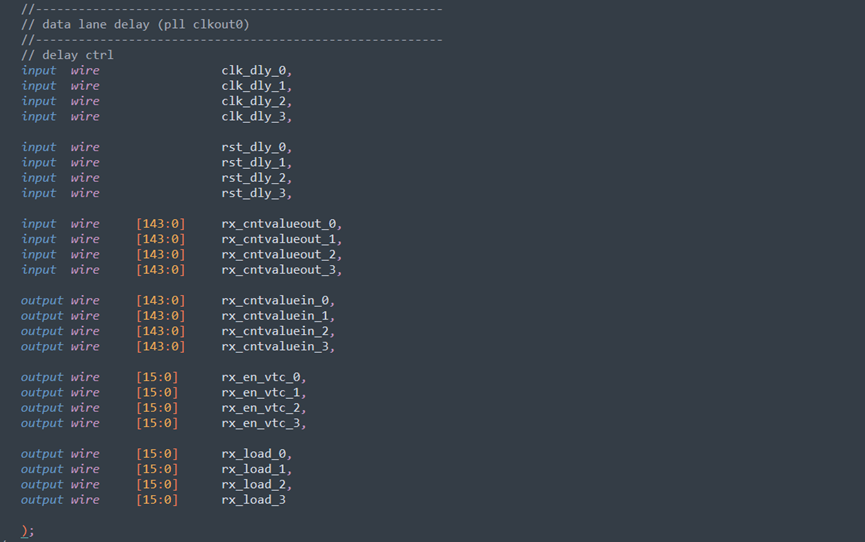

主状态机:

初始IDLE空闲状态:当设备上电pwon_init_ok1且同时没有软复位afe_soft_rst0跳转进入ENTER_PAT状态;

ENTER_PAT状态:控制AFE进入测试模式 ,当接收到外部传来的enter_pat_ok为1表示进入测试模式操作完成,可以跳转DETECT状态;

DETECT状态:对通道数据进行延时修改,扫描检测,完成512次扫描后进入LOCKING状态;

LOCKING状态:当locking_ok1,表示扫描同步成功,跳转到EXIT_PAT状态;当locking_err1表示锁定失败,触发软复位,重新开始全流程;

EXIT_PAT状态:控制AFE退出测试模式,接收到exit_pat_ok1跳转到LOCKED状态;

LOCKED状态:全部通道同步成功且延时锁定到最佳数据采样点,正常输出数据的工作状态,只有当pwon_init_ok0检测到掉电或是全局复位才会退出该状态跳转到IDLE状态重新开始;

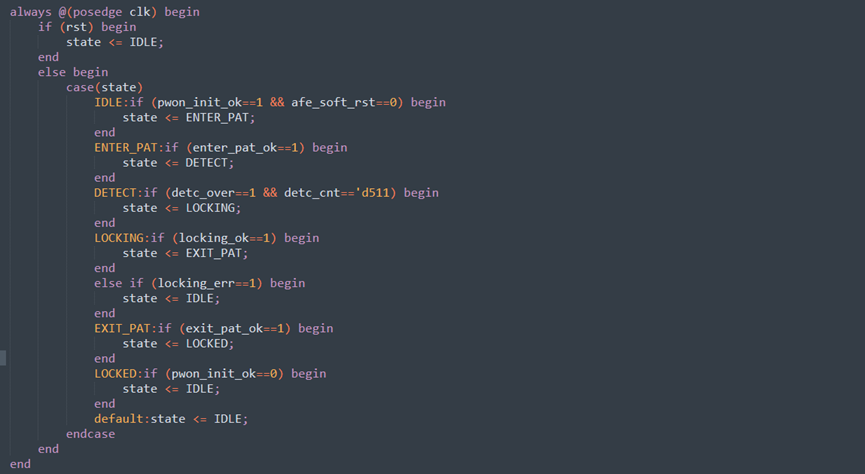

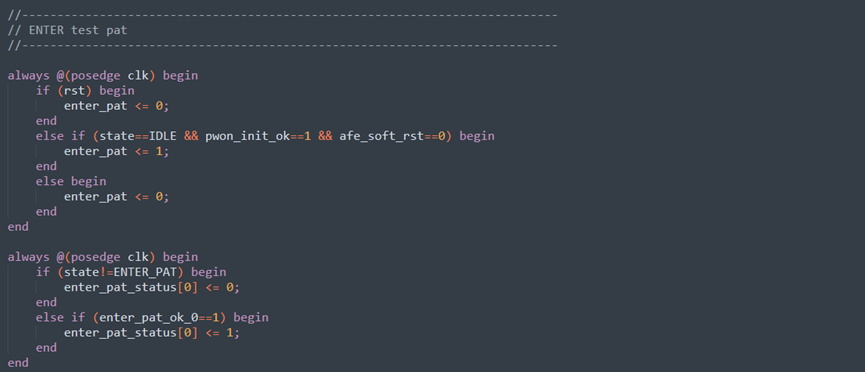

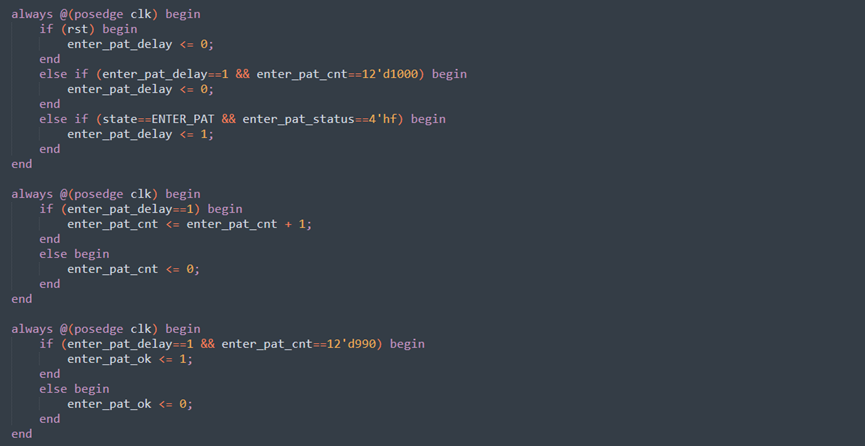

ENTER_PAT子流程:

enter_pat脉冲:在状态进入ENTER_PAT时产生1拍脉冲,驱动外部模块afe_en_pattern驱动spi写寄存器进入测试模式,同时配置10bit测试码;当接收到外部传来的enter_pat_ok为1表示进入测试模式操作完成;

等待所有AFE完成,enter_pat_status[3:0]分别记录各AFE的进入测试模式的状态。当enter_pat_status==4'hf时表示全部进入测试模式,启动enter_pat_delay延迟计数;

延迟等待10us,让AFE在进入测试模式后,等待数据稳定,最后拉高一拍enter_pat_ok;

本文章由威三学社出品

对课程感兴趣可以私信联系