Verilog 3-8译码器设计与仿真:深入理解case语句与组合逻辑

- 一、概述

- 二、3-8译码器原理

- 三、Verilog代码详解

-

- [3.1 主模块设计](#3.1 主模块设计)

- [3.2 Testbench设计](#3.2 Testbench设计)

- 四、仿真截图

一、概述

在数字电路设计中,3-8译码器是一个基础而重要的组件,它能够将3位二进制输入转换为8位输出,每次只有一位输出为高电平。本文将通过一个完整的Verilog实现,深入讲解如何使用case语句实现3-8译码器,并配合Testbench进行功能验证。

二、3-8译码器原理

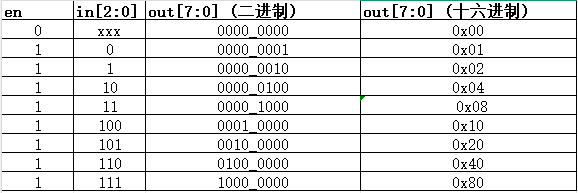

3-8译码器的功能是将3位二进制码转换为8位独热码(One-Hot Code):

输入:3位二进制信号(in[2:0])

输出:8位信号(out[7:0])

使能信号:en,控制译码器是否工作

完整真值表:

三、Verilog代码详解

3.1 主模块设计

c

module test(

input en, // 使能信号

input [2:0] in, // 3位输入信号

output reg [7:0] out // 8位输出信号,定义为reg类型

);

always @(*) begin

if(en) begin

case(in)

3'b000 : out = 8'b0000_0001; // 输入000,输出第0位为1

3'b001 : out = 8'b0000_0010; // 输入001,输出第1位为1

3'b010 : out = 8'b0000_0100; // 输入010,输出第2位为1

3'b011 : out = 8'b0000_1000; // 输入011,输出第3位为1

3'b100 : out = 8'b0001_0000; // 输入100,输出第4位为1

3'b101 : out = 8'b0010_0000; // 输入101,输出第5位为1

3'b110 : out = 8'b0100_0000; // 输入110,输出第6位为1

3'b111 : out = 8'b1000_0000; // 输入111,输出第7位为1

endcase

end

else begin

out = 8'b0000_0000; // 使能无效时,输出全0

end

end

endmodule代码解析:

模块接口定义

输入:en(1位使能),in[2:0](3位输入)

输出:out[7:0](8位输出),使用reg类型是因为在always块中赋值

组合逻辑设计

使用always @()表示组合逻辑,敏感列表中的 表示所有输入信号

当en=1时,根据in的值选择对应的输出

当en=0时,无论输入为何值,输出都为0

case语句使用

case语句是Verilog中实现多路选择的高效方式

每个case项对应一个输入值和对应的输出

下划线_用于提高可读性,不影响数值

3.2 Testbench设计

c

`timescale 1ns/1ps // 时间单位1ns,精度1ps

module test_tb();

reg en; // 测试激励:使能信号

reg [2:0] in; // 测试激励:输入信号

wire [7:0] out; // 观察响应:输出信号

// 实例化被测试模块

test u_test(

.en (en),

.in (in),

.out (out)

);

// 测试激励生成

initial begin

// 初始状态

en = 1'b0;

in = 3'b000;

// 测试序列

#20 en = 1'b1; in = 3'b001; // 20ns后,测试001

#30 en = 1'b1; in = 3'b011; // 再30ns后,测试011

#25 en = 1'b1; in = 3'b101; // 再25ns后,测试101

#20 en = 1'b1; in = 3'b100; // 再20ns后,测试100

#25 en = 1'b0; in = 3'b101; // 测试使能无效的情况

#35 en = 1'b0; in = 3'b111;

#25 en = 1'b1; in = 3'b000; // 测试000输入

#35 en = 1'b0; in = 3'b111;

#300 $stop; // 300ns后停止仿真

end

endmoduleTestbench解析:

时间单位和精度

timescale 1ns/1ps:仿真的基本时间单位是1ns,精度为1ps

信号定义

使用reg类型定义需要驱动的输入信号

使用wire类型定义需要观察的输出信号

测试激励生成

使用initial块生成测试序列

#表示延迟,如#20表示延迟20个时间单位

测试覆盖了部分输入组合和使能信号的变化

实例化被测试模块

使用命名端口连接方式,提高代码可读性

四、仿真截图