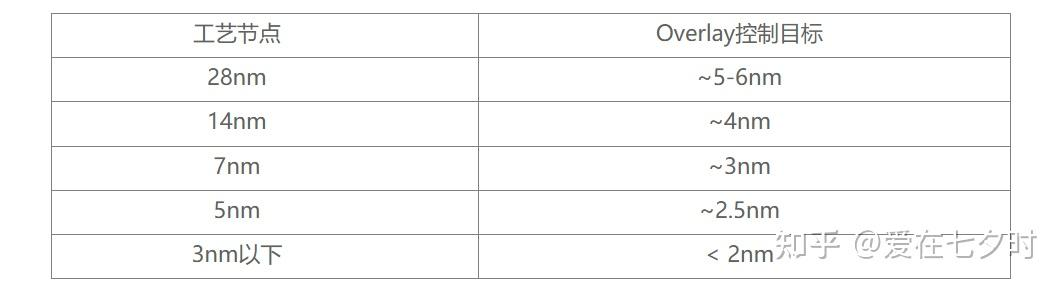

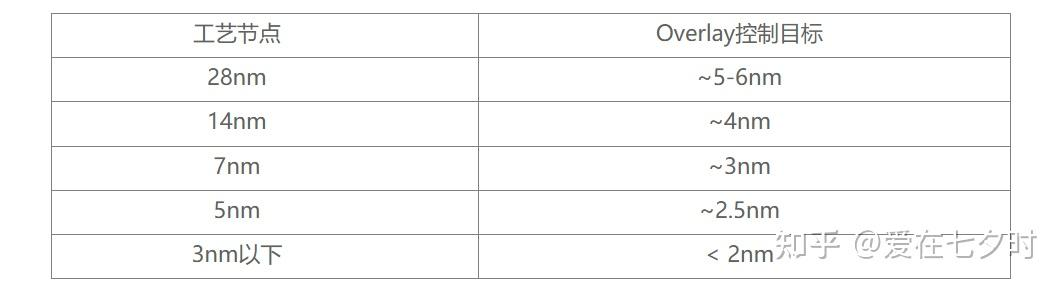

在光刻工艺中,套刻精度(Overlay)已成为影响芯片良率的关键限制因素之一。套刻精度(Overlay)控制的核心目标是确保每一层掩膜图形与其下方图形的精准对准,尤其是在像 5nm 这样的先进节点中,套刻精度(Overlay)容差通常是图形尺寸的 30%。因此,这一精度必须严格控制在几纳米之内,以确保良率的提升。

在光刻工艺中,套刻精度(Overlay)已成为影响芯片良率的关键限制因素之一。套刻精度(Overlay)控制的核心目标是确保每一层掩膜图形与其下方图形的精准对准,尤其是在像 5nm 这样的先进节点中,套刻精度(Overlay)容差通常是图形尺寸的 30%。因此,这一精度必须严格控制在几纳米之内,以确保良率的提升。