大家好。在PCB设计流程中,从原理图到版图的数据传递是承上启下的关键环节。传统方式下,工程师需要手动生成网表、创建PCB文件、再逐一导入封装与连接关系,操作繁琐且容易出错。Cadence 25.1 进一步加强了原理图与 PCB Editor 的集成能力,通过 Export to Layout(输出至版图) 功能,可以直接将设计数据一键传递至版图环境,并支持输出完成后自动启动 PCB Editor,真正实现原理图与版图之间的无缝协同。

本次分享将演示如何利用这一集成功能,完成从原理图到 PCB 版图的快速输出与初始环境搭建。以下是关键步骤总结:

一:原理图输出至版图

-

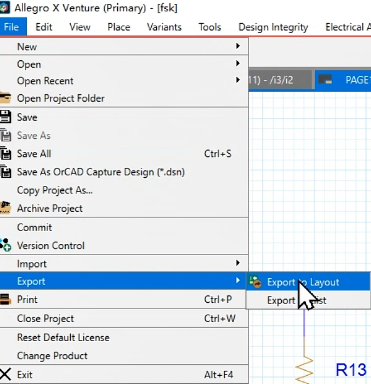

打开原理图,点击菜单 File → Export → Export to Layout。

-

在弹出的窗口中选择 PCB Editor,设定输出文件名称。

-

勾选 Launch Allegro PCB/Package Layout,系统将在输出完成后自动启动 PCB Editor。

-

点击 OK 执行输出,等待下方进度条完成。

二:初始化PCB环境

-

PCB Editor 自动启动后,根据弹出的 License 选择窗口选择可用许可证(如 Allegro X Designer)。

-

点击菜单 Setup → Design Parameters,确认设计单位与精度。

-

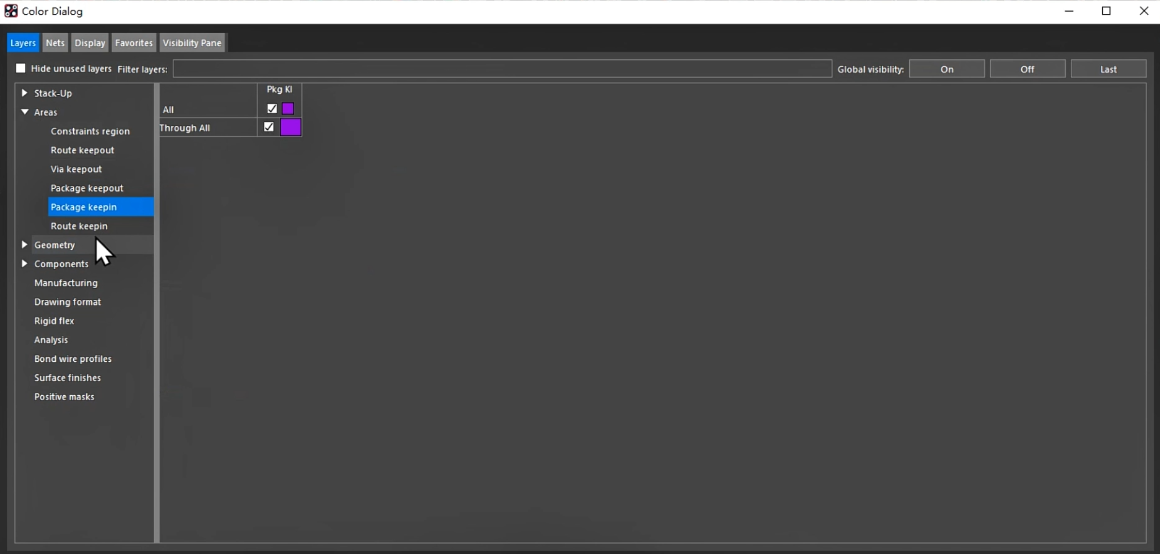

打开 Color 管理器,确保 Package Keepin 与 Design Outline 层面显示为开启状态(可将 Design Outline 设为醒目颜色以便区分)。

三:绘制板框与约束区域

-

根据结构尺寸绘制板外形(Design Outline)。

-

系统会根据规则自动生成配套的 Package Keepin 区域,无需手动绘制。

四:快速放置元器件

-

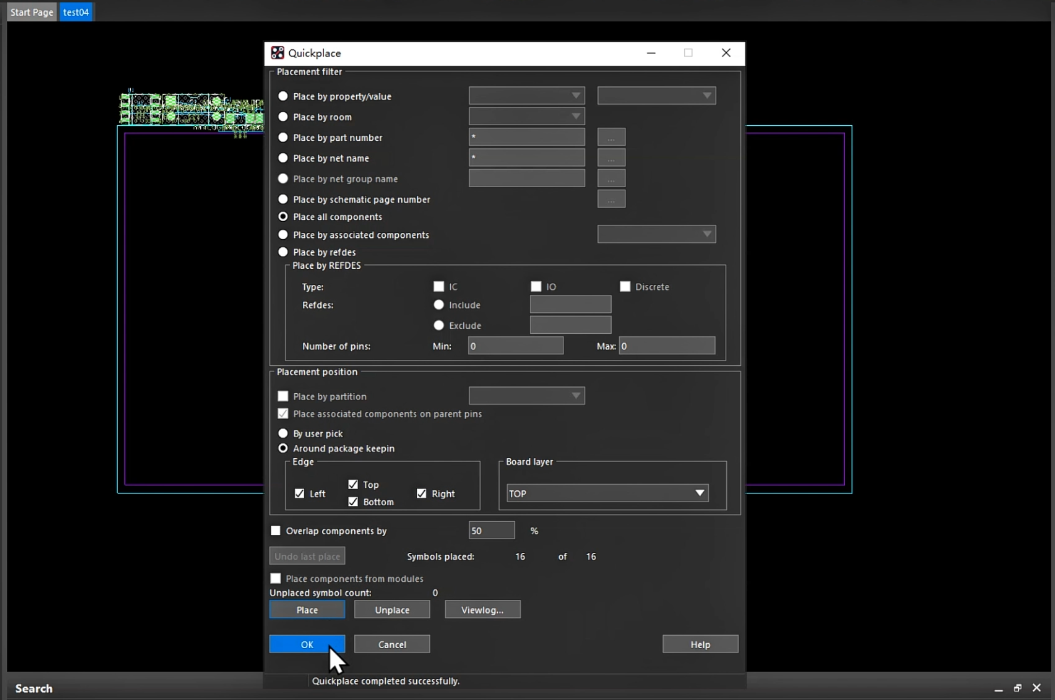

点击 Place → Quickplace,打开快速放置设置面板。

-

点击左下角 Place 按钮,后台的元器件将被释放并排列在工作区边缘。

五:优化显示与布局

-

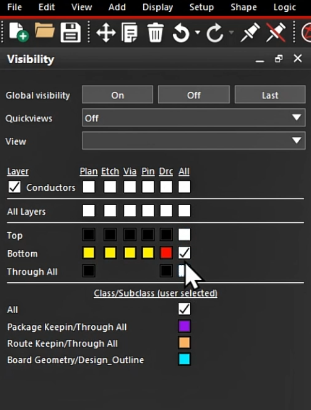

利用 Color 管理器关闭不必要的层面,只保留关键层(如焊盘、丝印等)。

-

将常用层面添加至右侧的 Visibility 面板,便于后续快速开关。

-

确认显示整洁后,即可正式进入布局布线阶段。

通过以上五步,即可完成从原理图到PCB版图的数据传递与环境初始化,显著提升前后端协同效率。

**原创简介:**芯巧电子是 Cadence 全球认证培训合作伙伴,是国内领先的电子、电气设计自动化和信息化管理系统方案与服务提供商,客户覆盖半导体、消费电子、通讯、汽车电子、工业自动化、教育科研等众多领域,业务涉及Cadence PCB及仿真全系列软件代理,PCB软件二次开发,电子元器件建库,PCB Layout 服务,PCB 加工装配等,拥有专业的市场销售、软件服务支持和软件定制开发团队。