模拟PLL与数字PLL(DPLL)的核心区别详解

目录

一、核心定义与架构差异

(一)模拟PLL(APLL)

(二)数字PLL(DPLL/ADPLL)

二、核心性能与实现差异(重点对比)

三、典型应用场景对比

四、核心差异总结表

五、总结

模拟PLL与数字PLL(DPLL)的核心区别详解

锁相环(PLL,Phase-Locked Loop)是电子系统中实现信号同步、频率合成、时钟恢复的核心电路,广泛应用于通信、雷达、芯片设计、电力电子等领域。根据信号处理方式和电路实现形态的不同,锁相环主要分为模拟PLL(APLL)和数字PLL(DPLL/ADPLL,后者为全数字PLL)两大类。二者核心目标一致------实现输入信号与输出信号的相位同步,但在电路架构、性能特性、实现方式和应用场景上存在本质差异,本文将全面拆解二者的核心区别,结合技术细节与应用场景,帮助清晰区分两类PLL的特点与适用场景。

一、核心定义与架构差异

模拟PLL与数字PLL的根本区别,在于信号处理的"连续性"与"离散性",以及核心模块的实现方式,二者的基本架构的差异直接决定了后续所有性能与应用的不同。

(一)模拟PLL(APLL)

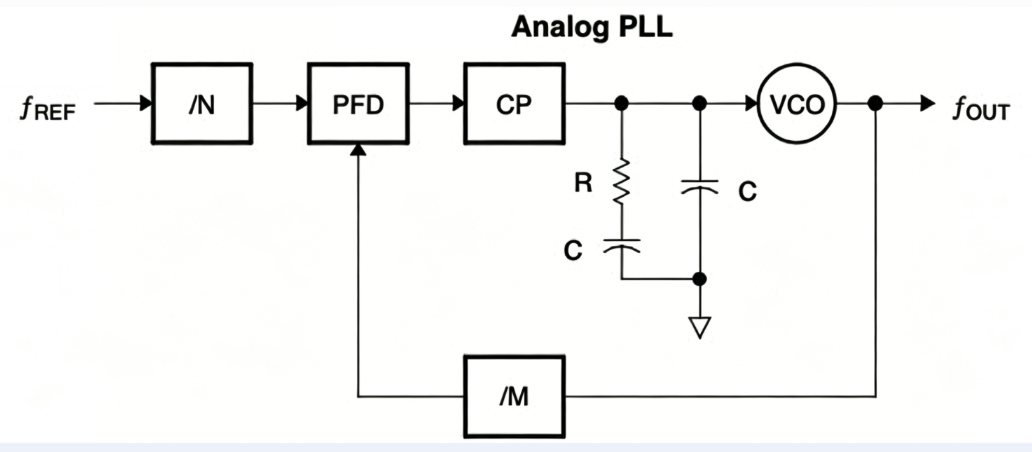

模拟PLL是传统锁相环架构,全程处理连续时间模拟信号,核心依赖模拟器件实现信号的鉴相、滤波与振荡,架构简洁且成熟,适合高频场景。

核心组成模块(全模拟架构):

- 模拟鉴相器(PD):核心功能是比较输入参考信号(如基准时钟)与输出反馈信号的相位差,将相位差转换为连续变化的模拟电压信号(误差电压)。常见类型为乘法器鉴相器、鉴相检波器,输出电压随相位差连续变化。

- 模拟环路滤波器(LPF):用于过滤鉴相器输出误差电压中的高频噪声和纹波,输出平滑的控制电压,稳定环路工作,避免振荡。主要分为无源RC滤波器、有源运放滤波器,参数(带宽、增益)由硬件器件(电阻、电容、运放)参数固定。

- 压控振荡器(VCO):PLL的核心振荡模块,输入为环路滤波器输出的连续模拟控制电压,输出频率随输入电压连续可调的模拟正弦波或方波。VCO的频率范围、相位噪声直接决定模拟PLL的高频性能,常见类型为LC-VCO、RC-VCO。

工作核心逻辑:输入参考信号与VCO输出的反馈信号进入鉴相器,产生与相位差对应的误差电压,经环路滤波器滤波后控制VCO的输出频率,直至VCO输出信号与输入参考信号相位同步(锁相),形成闭环控制。

(二)数字PLL(DPLL/ADPLL)

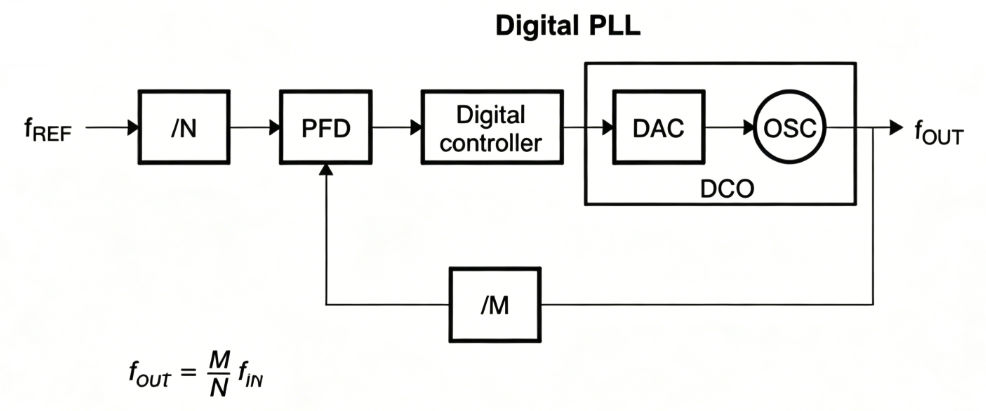

数字PLL是基于数字逻辑实现的锁相环,全程处理离散时间数字信号,核心模块采用数字电路设计,可通过软件编程灵活配置参数,易与数字系统(如SoC、FPGA)集成,是现代数字电子系统的主流选择。

核心组成模块(全数字/混合架构):

- 数字鉴相器(DPD):将输入参考信号与反馈信号的相位差转换为离散的数字量(误差码),而非连续电压。常见类型为相位频率检测器(PFD)、时间数字转换器(TDC),检测精度高,抗噪声能力强。

- 数字环路滤波器(DLF):接收数字鉴相器输出的误差码,通过数字滤波算法(如FIR、IIR滤波)过滤噪声,输出离散的数字控制字(FCW,频率控制字),参数(带宽、增益、相位裕度)可通过软件编程动态调整,灵活性极高。

- 数控振荡器(DCO/NCO):作为数字版VCO,输入为数字环路滤波器输出的数字控制字,输出频率按固定步进量化可调的数字信号(方波、脉冲序列或经DAC转换后的模拟波形)。其工作原理基于相位累加器与基准时钟,频率调节精度取决于控制字位数和基准时钟频率(详见《数控振荡器(DCO)详解》)。

工作核心逻辑:输入参考信号经模数转换(若为模拟参考)后,与DCO输出的反馈信号进入数字鉴相器,产生数字误差码,经数字环路滤波器处理后输出控制字,控制DCO的输出频率,直至实现相位同步,完成锁相闭环。

二、核心性能与实现差异(重点对比)

基于架构的不同,模拟PLL与数字PLL在实现难度、集成度、性能参数、稳定性等方面存在显著差异,以下从关键维度进行详细对比,明确二者的优劣与适用场景。

(一)实现方式与集成度

• 模拟PLL:依赖电阻、电容、运放、VCO等模拟器件,电路设计需考虑模拟信号的干扰、温漂、电源噪声等问题,设计难度较高;集成度低,难以适配纳米级半导体工艺,无法与数字SoC、FPGA无缝融合,通常需要独立的模拟芯片或模块。

• 数字PLL:核心模块由数字逻辑门、寄存器、计数器、相位累加器等数字器件组成,无需复杂模拟器件;易适配纳米级工艺,可直接集成在数字芯片(如FPGA、CPU、SoC)内部,与数字系统兼容性好,集成度极高,大幅缩小电路板面积。

(二)频率范围与噪声性能

• 频率范围:模拟PLL的VCO可轻松实现高频输出(射频、微波级,可达数十GHz),是高频场景的首选;数字PLL受限于数字逻辑的工作速度,通常适用于中低频场景(kHz~数百MHz),高频场景需采用高速工艺或混合架构(如LC-DCO),成本较高。

• 噪声与抖动:模拟PLL的带内噪声低、输出抖动小,适合对信号纯度要求高的场景,但对电源噪声、温度变化、电磁干扰(EMI)敏感,需设计复杂的供电滤波和屏蔽电路;数字PLL抗数字噪声能力强,受温度、电源波动影响小,可通过软件优化抖动性能,但存在采样折叠噪声,高频场景下相位噪声略优于模拟PLL。

(三)灵活性与可调性

• 模拟PLL:环路参数(带宽、增益、捕获范围)由硬件器件参数固定,一旦设计完成,无法通过软件调整,灵活性差;捕获范围较窄,锁定时间中等,若需调整参数,需重新设计电路、更换器件。

• 数字PLL:环路参数可通过软件编程动态配置,如调整数字环路滤波器的带宽、增益,修改DCO的控制字,实现频率、相位的精准调节;捕获范围宽,锁定速度快,可根据应用场景自适应调整性能,无需修改硬件电路,灵活性极强。

(四)功耗与面积

• 模拟PLL:低频场景下功耗较低,但高频VCO、有源滤波器的漏电电流大,功耗随频率升高而显著增加;电路需占用较大的电路板面积,尤其是LC-VCO,电感、电容体积较大,不利于小型化设计。

• 数字PLL:无漏电电容,功耗随半导体工艺进步和工作频率降低而大幅下降,适合低功耗嵌入式系统;数字逻辑集成度高,占用芯片面积小,无需额外的模拟器件,有利于设备小型化、轻量化。

(五)稳定性与可靠性

• 模拟PLL:受温度漂移、器件老化、电源波动影响较大,长期工作稳定性较差,需定期维护或校准,尤其在恶劣环境(高温、高干扰)下,性能衰减明显。

• 数字PLL:全数字架构,无模拟器件的漂移问题,抗温度、电源噪声能力强,长期工作稳定性好,可靠性高,无需复杂的校准流程,适合长期稳定运行的数字系统。

三、典型应用场景对比

基于上述性能差异,模拟PLL与数字PLL的应用场景各有侧重,二者互补,覆盖不同领域的需求。

(一)模拟PLL的典型应用

• 射频通信领域:如手机、基站、卫星通信的本振信号生成、频率合成,需高频、低噪声的信号,模拟PLL(LC-VCO架构)是核心选择。

• 高速模拟时钟:如示波器、信号发生器的时钟源,要求低抖动、高纯度,模拟PLL可满足高频时钟的性能需求。

• 传统广播与解调:如AM/FM收音机、电视信号解调,依赖模拟PLL实现信号同步与解调。

• 微波、雷达系统:高频信号的生成与同步,模拟PLL的高频性能优势显著。

(二)数字PLL的典型应用

• 数字通信系统:如以太网、串口、光纤通信的时钟恢复,需灵活可调的时钟,数字PLL可实现精准的时钟同步。

• 芯片设计:FPGA、CPU、SoC的片上时钟源,需与数字逻辑无缝集成,数字PLL(ADPLL)是主流方案,可通过软件配置不同频率的时钟。

• 软件无线电(SDR):需可编程的载波频率,适配不同通信协议,数字PLL(搭配NCO)可实现灵活的频率调节。

• 低功耗嵌入式系统:如微控制器(MCU)、物联网设备,数字PLL的低功耗、小面积优势适合此类场景。

• 电力系统同步:如智能电网的信号同步,数字PLL抗干扰能力强,可实现精准的相位同步。

四、核心差异总结表

五、总结

模拟PLL与数字PLL并非替代关系,而是根据应用场景的需求互补共存。模拟PLL以"高频低噪"为核心优势,主导高频、高信号纯度的场景,但其集成度低、灵活性差的短板限制了其在数字系统中的应用;数字PLL以"可编程、易集成、低功耗"为核心优势,适配现代数字电子系统的发展需求,在中低频、灵活可调的场景中占据主导地位,随着半导体工艺的进步,其高频性能也在不断提升。

选择两类PLL的核心原则的是:若需高频、低抖动、高信号纯度,优先选择模拟PLL;若需灵活可编程、易集成、低功耗,或应用于数字系统,优先选择数字PLL。在实际工程设计中,也可采用混合PLL架构,结合二者优势,满足复杂场景的性能需求。

参考资料