PCB绘制与检查

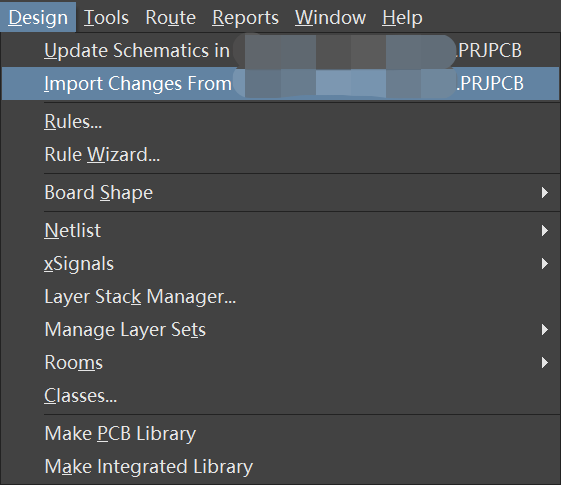

- 让PCB和原理图一致后(最好不要有DRC问题)

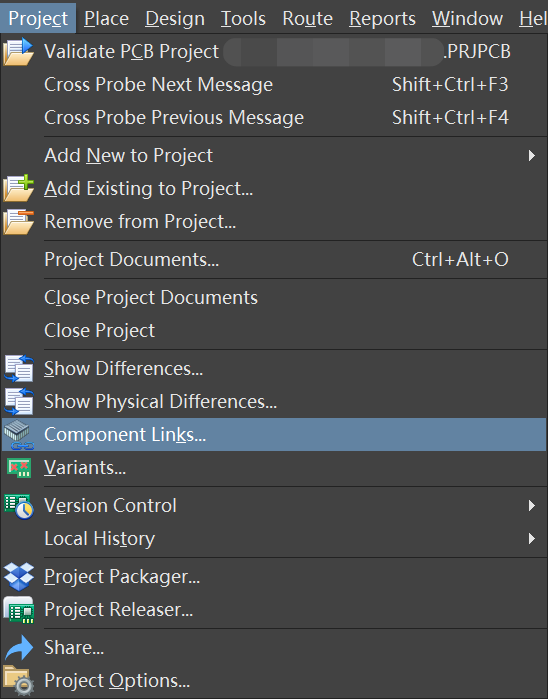

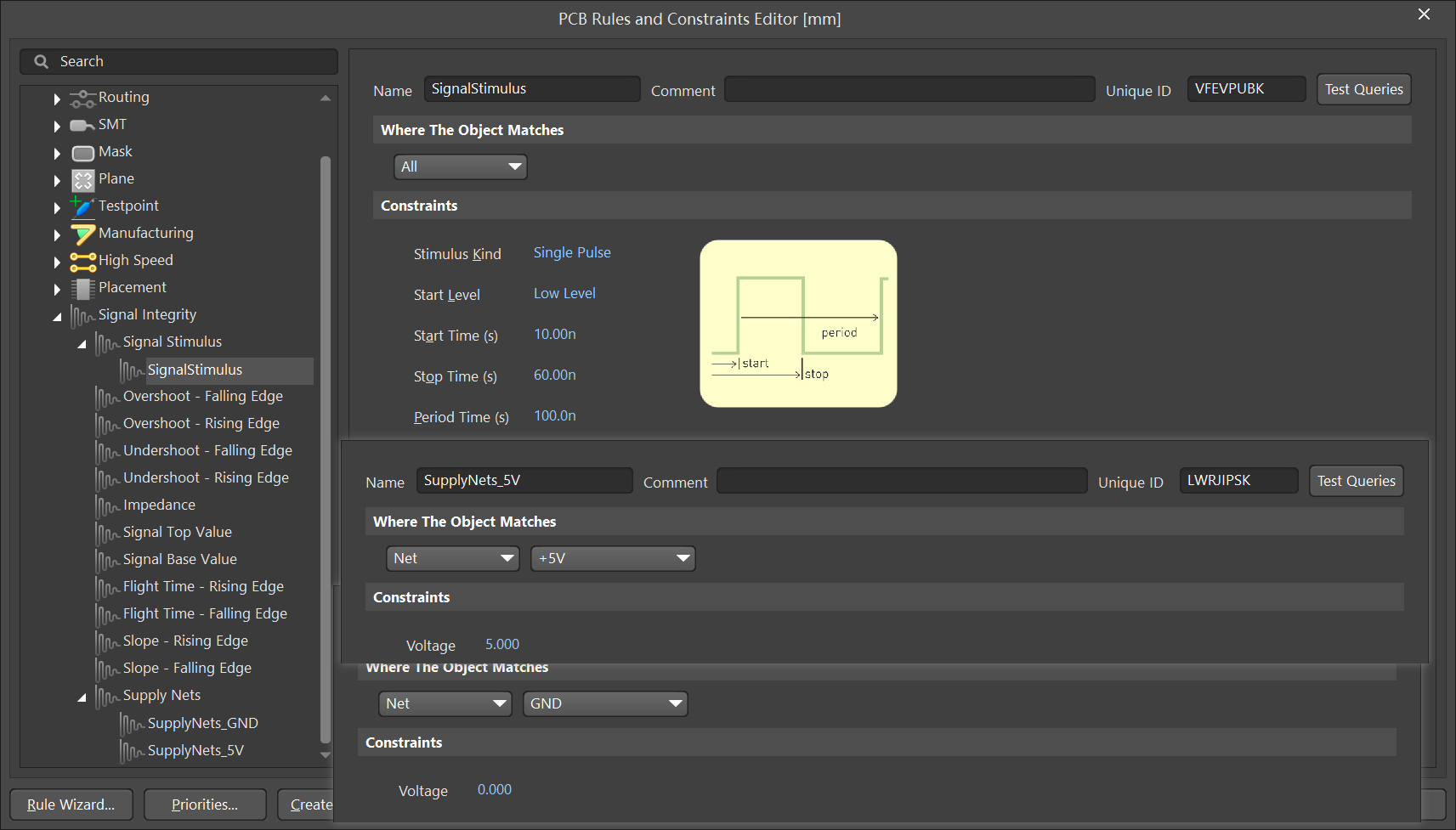

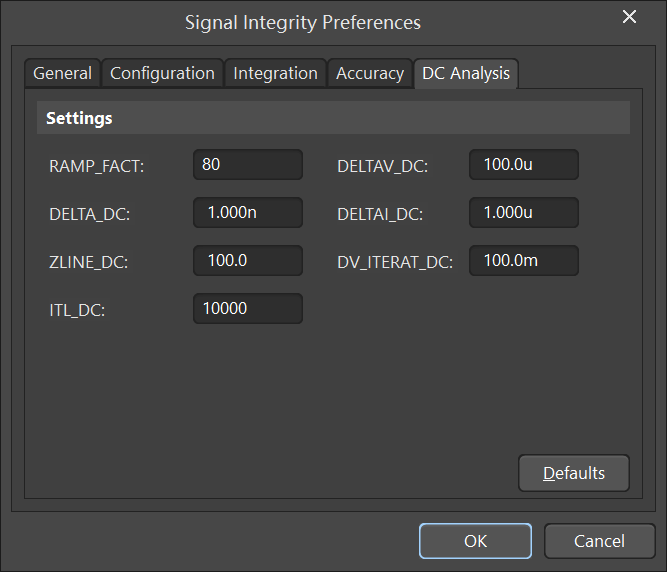

设置激励与电源

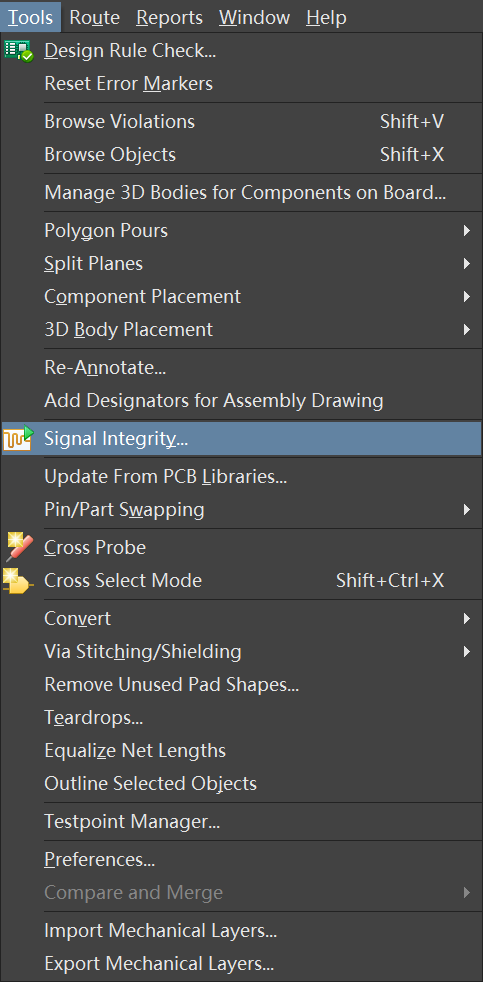

SI分析:单线路的传输分析

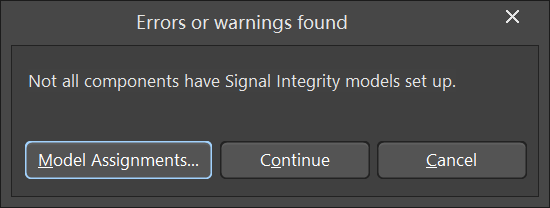

- 可先进行默认模型配置,点击Continue:

-

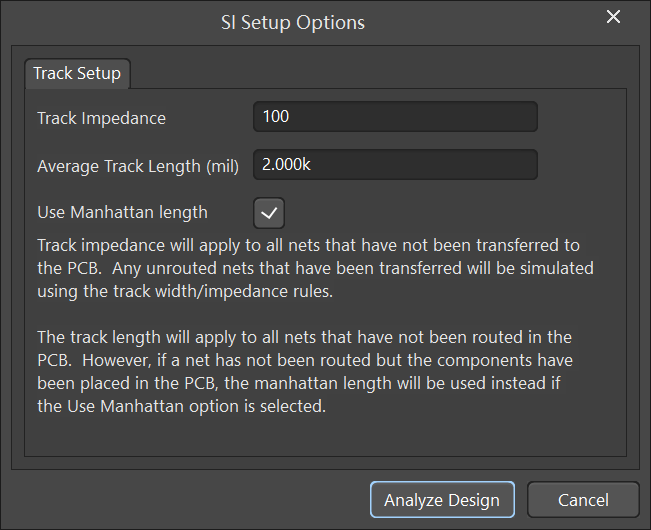

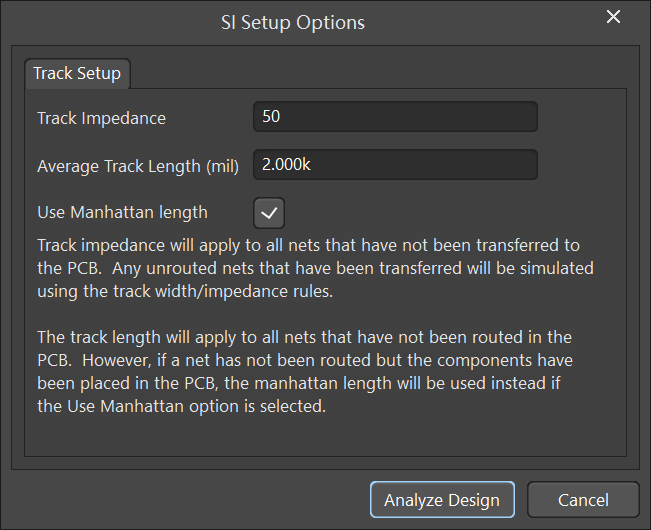

Average Track Length , PCB设计中的网络通常处于以下三种状态之一:

- 已布线: 线已经画好了。

- 软件做法: 直接读取实际的物理长度,忽略这里的"Average Track Length"设置。

- 未布线(但元件已放置): 元件在板子上,但还没有连线。

- 软件做法: 软件会根据勾选的"Use Manhattan length",自动计算两点间的直角距离作为长度。

- 未放置/概念阶段(最关键的部分): 原理图导入了,但某些模块的元件还没放到板子上,或者你正在进行"前仿真",想看如果走线大概是这么长,信号会怎么样。

- 软件做法: 既然没有坐标,也没法算曼哈顿距离,软件就只能盲猜 。它猜的依据就是在这里填入的 "Average Track Length" 。

- 软件做法: 既然没有坐标,也没法算曼哈顿距离,软件就只能盲猜 。它猜的依据就是在这里填入的 "Average Track Length" 。

- 已布线: 线已经画好了。

-

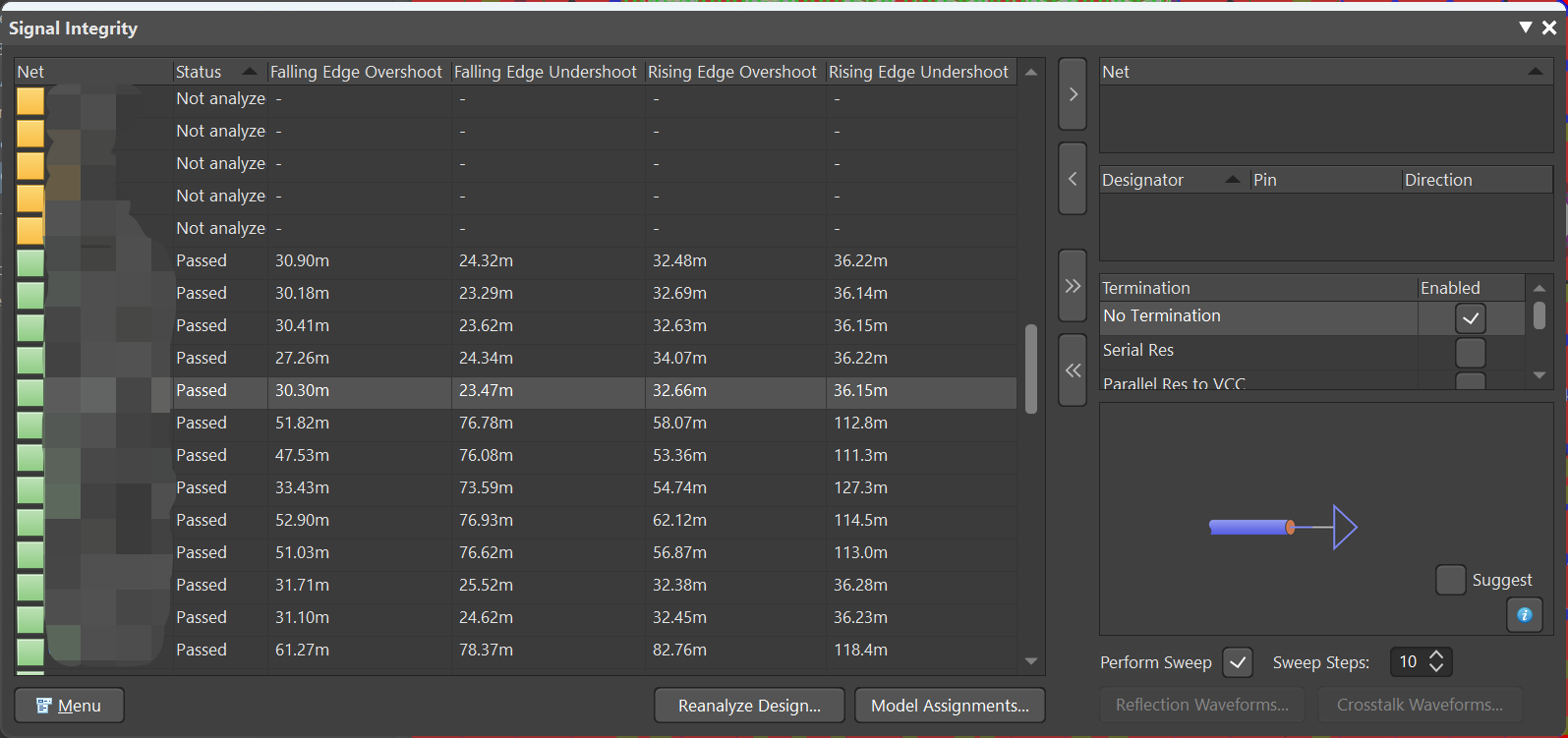

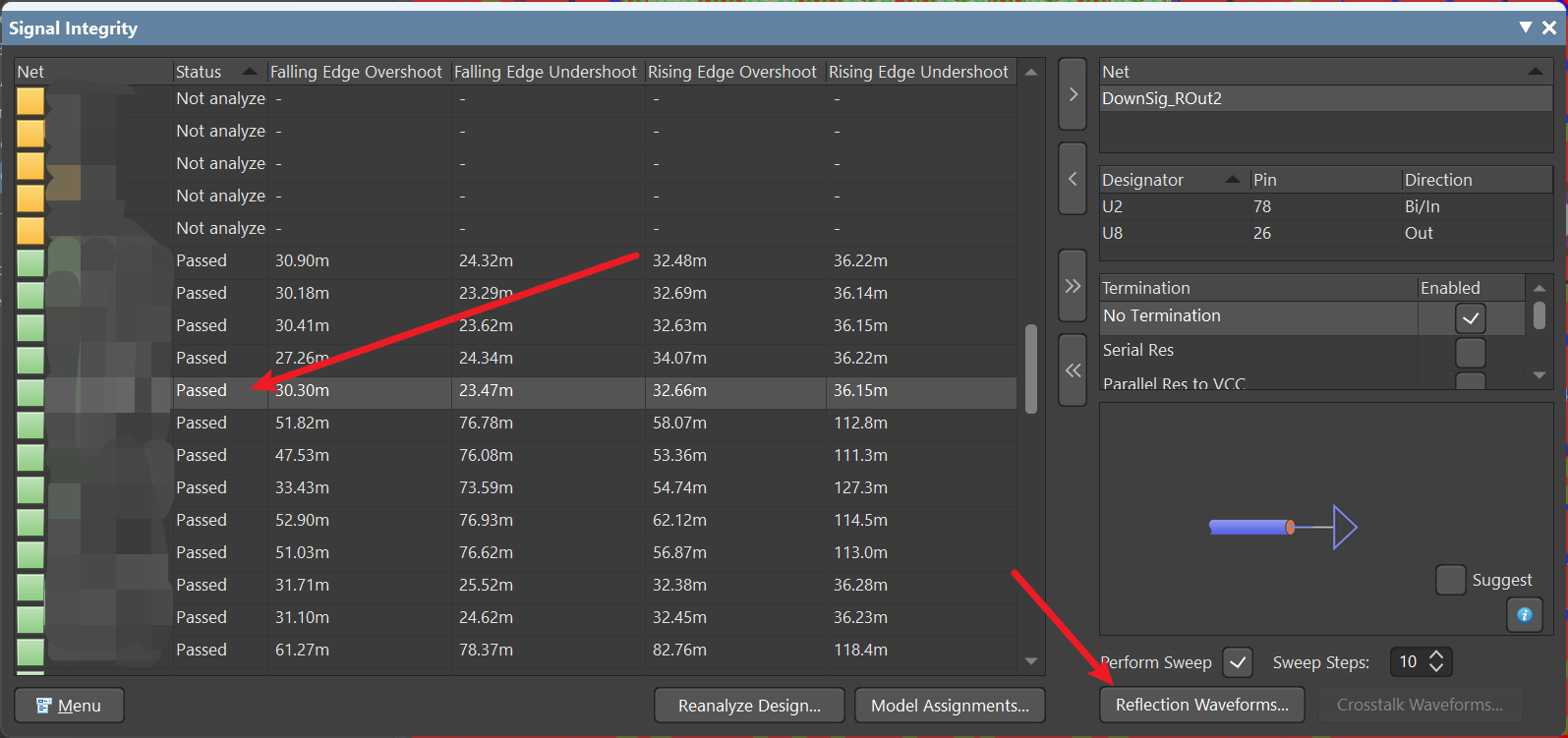

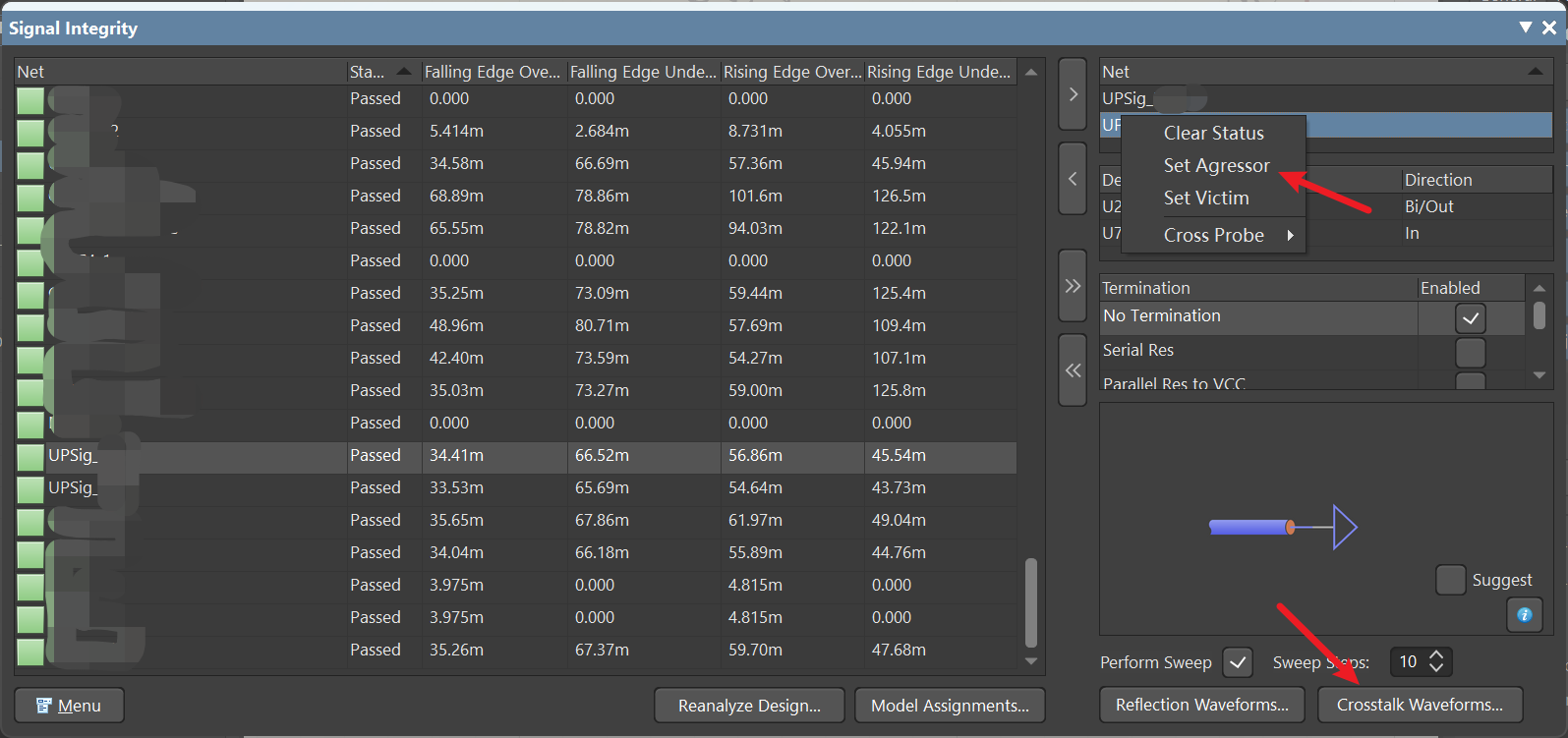

进行线路的传输分析:

- Falling Edge Overshoot / Falling Edge Undershoot:下降沿过冲/下冲。单位是 m (毫伏) ,数值越小越好。

传输分析结果

-

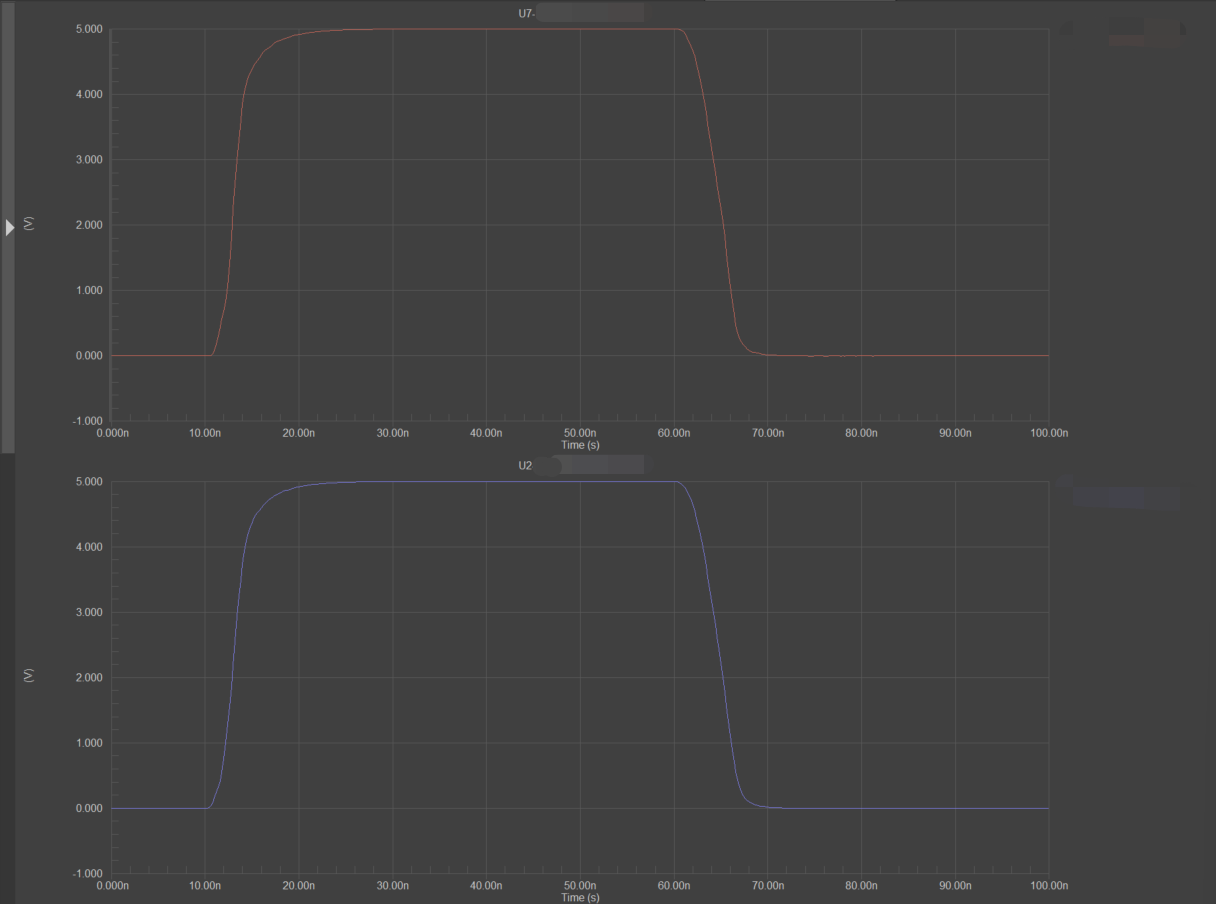

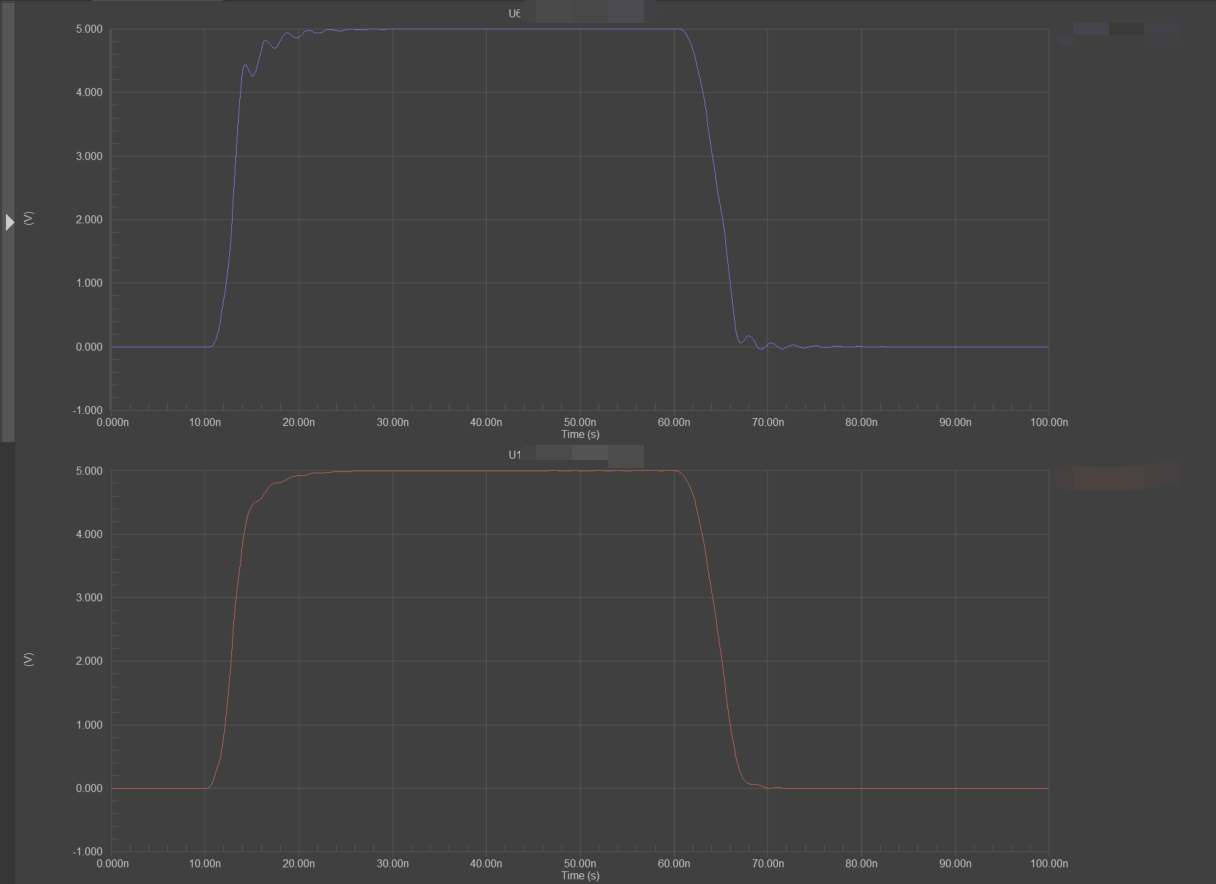

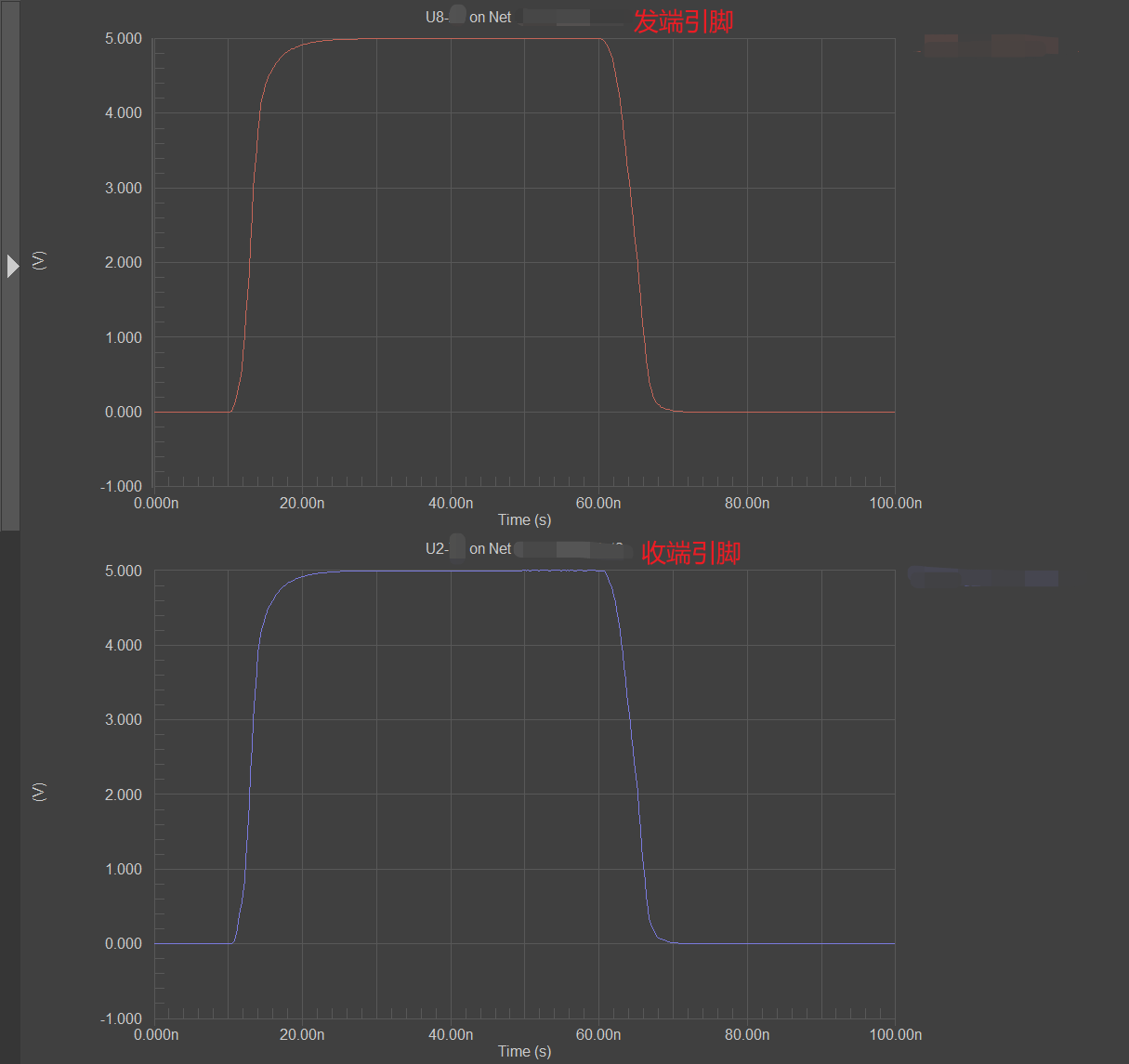

图展示了同一网络在驱动端 和接收端的电压波形对比。

-

上图(红色波形)

- 角色 :这通常是驱动端(Driver),即信号发出的地方(源端)。

- 特征:信号从 0V 上升到 5V,波形非常"方正",上升沿很陡峭。这是理想的输入激励信号。

-

下图(蓝色波形)

- 角色 :这通常是接收端(Receiver),即信号到达的地方(负载端)。

- 特征:这是经过 PCB 走线传输后到达接收芯片的信号。

-

分析 :信号质量极佳,没有明显的过冲、下冲或振铃现象。 走线阻抗匹配做得非常好(可能是源端串联匹配或终端并联匹配起了作用),或者走线很短,传输线效应不明显。

-

注:10MHz,周期约为 100ns。

-

注:首次对设计进行分析时,将启用并运行四条默认容差规则,以及在原理图或 PCB 中设置的所有 Signal Integrity 规则。之后可在Signal Integrity面板中通过单击Menu按钮并选择Set Tolerances来设置这些容差、直流阻抗等。

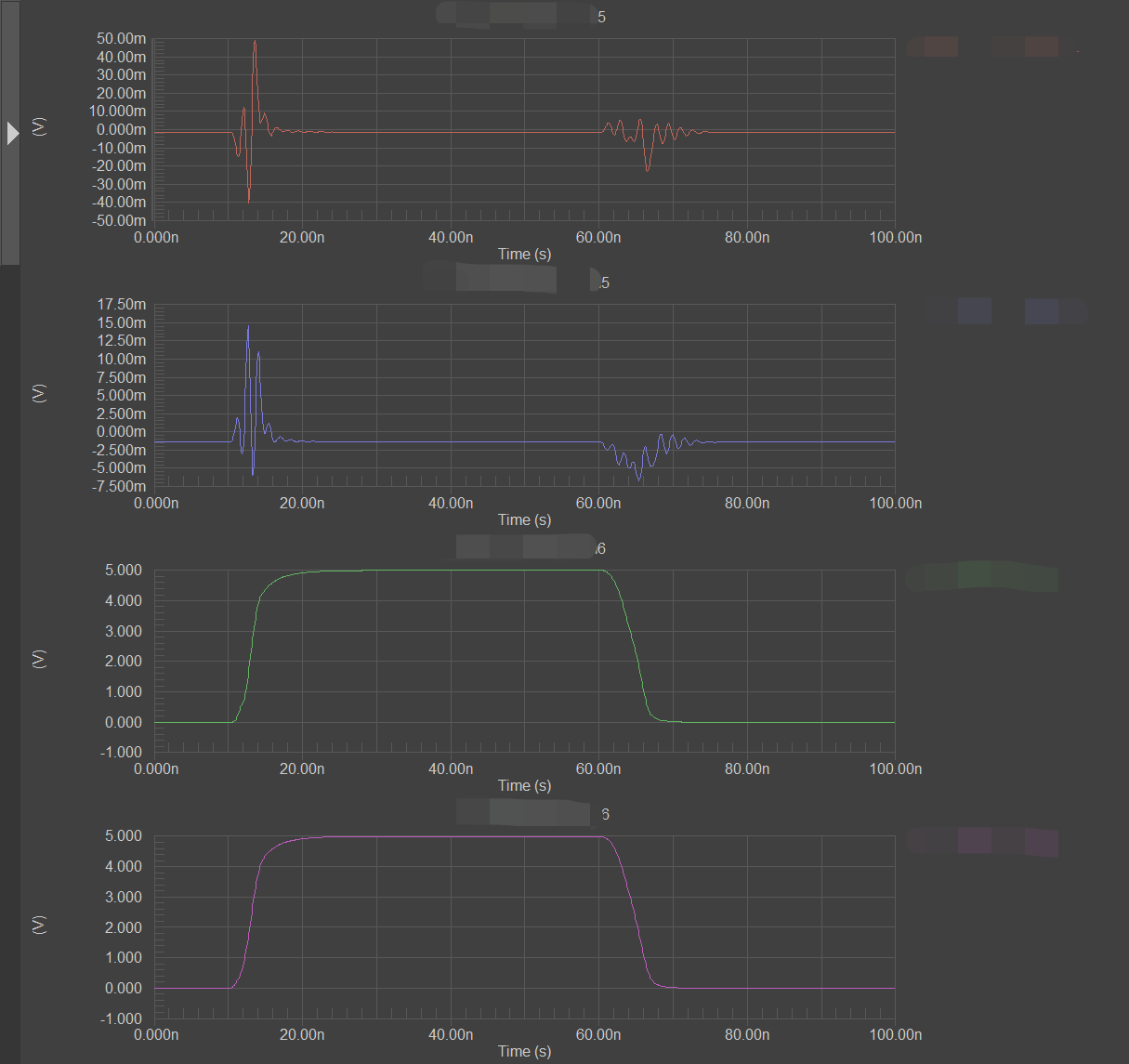

SI分析:串扰分析

分析结果

相关问题及解决

- Class Document Source Message Time Date No.

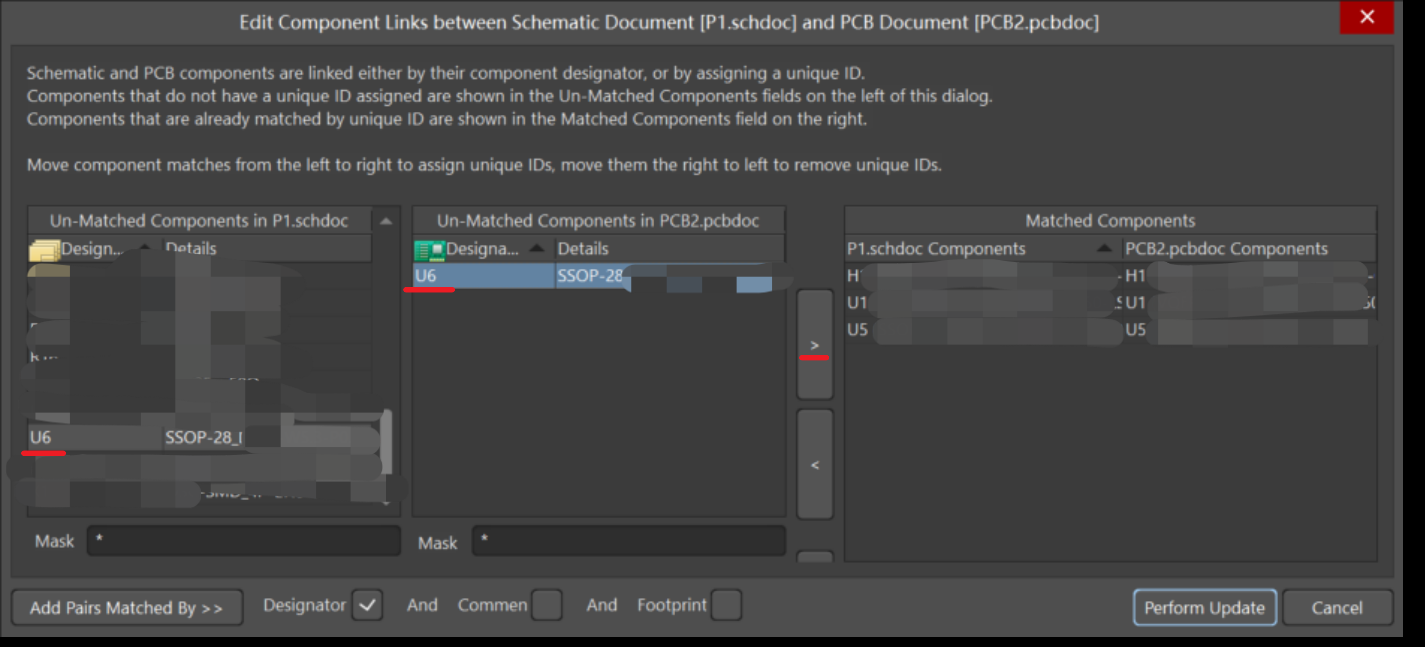

Fatal Error\] PCB2.pcbdoc Signal Integrity U6 - PCB component is not linked to a Schematic component. **:** 😗\* 2026/*/* 581